1

Изобретение отпоеитеи к ячейкам аиалоговой иамяти и может быть исиользоваио ири решеиии различных задач автоматичеекого уиравлеиия.

Известны ячейки аиалоговой памяти, содержаи;ие оиерациоииые усилители, выходы которых через ключи па полевых траизисторах иодсоедипеиы к затворам потоковых повторителей п к заиомииающим копдеисаторам, и резисторы обратпой связи, соедпиеииые с выxoдa rи ячеек и иивертирующими входами операциоппых усилителей.

В известных ячейках апалоговой памяти ири замыкании ключа на выходе схемы устанавливается паиряжеипе С/и,,,х за счет действия глубокой отрицательной обратной связи, поданной через резистор с выхода схемы па 1,нвертируюп1,ий вход усилителя.

Одиако зиачительный ток разряда заномннаюи.1,его конденсатора не обеспечивает длнтелыгого хранения ниформации с больпюй точностью, что является суи1ествеиным недостатком известных ячеек намятн. Ток разряда для известно схемы определяется пход1И)1М током iiCTOKOiioro новторнтетя, током разряда собственно конденсатора и токами утечки через ключ па нолевом транзисторе по переходу сток-исток и по затвору от управляюП1,его сигпала- Практически ток утечки через переход сток-исток ключа на 2-3 порядка

ирспьипает все осталып ш составляюии1е тока разряда заноми;1аюн1его конденсатора, так как определяется токами утечкн запертого перехода ключа.

Другнм недостатком пзвестиой схемы является ее малое быстродействие. При отключеиии запоминающего копдеисатора от выхода ус 1лптеля разрывается петля отрпиательиой обратиой связи, и напряжение на выходе

уснлителя. определяемое входным слгпалом, резко увеличивается, иоэтому прп очередном замыкаиии ключа иереходиые пропеесы в схеме затягиваются. Кроме того, ирп разомкпутом ключе постояшюе паиряжепие t/g,,,x подается па пивертируюо1пй вход усилителя и в противофазе поступает на входной зажим ключа, что увеличивает и без того значительную величину тока утечки через иоследн1п1, а следовательио, снижает точность запомппаппя при там же времеип хранения.

Пел1)Ю изобретений яв.тяется пов1 и1:ение бь1СТ1)оде11стния aiia.ioroBoii намятл. Эта иель Д(кТ1:1-;1отся тем, что между входом

HleiiKii памяти и нсшп ертнруюним входом опср.-нионного илите.тя включен допо-тните.п.пып к.тюч. libixo.T операниоппого уси.тнтеля через вто;)011 j.ieMeirr отрицательно: обратно соедн еп с его инверт руюн1,им входом, ячейк ;амят через резистор еледящой обратпс и i

руЮЩПМ ВХОДО 1 LU I I111

Оба ключа и и иi i ii

лагаемо i i ii i i i i

ПЫ iia ЛЮП-тр 1 iiiLIIи

составляющих loi inii i i i i u

конденсатора, к no L up к i i МИ через вход ULI i и i iii ii i i

управляюпцпе up i i nI i

ключи целесооГ 1 i по i и п i ii i i i i i i зиетора.х.

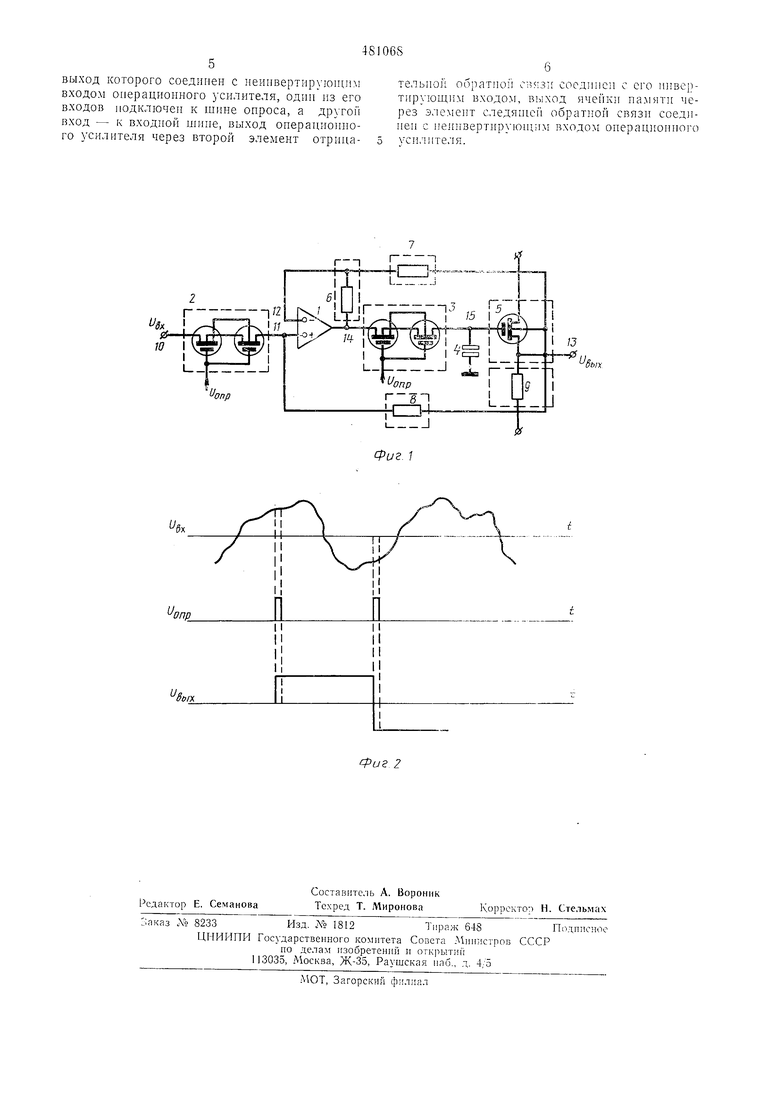

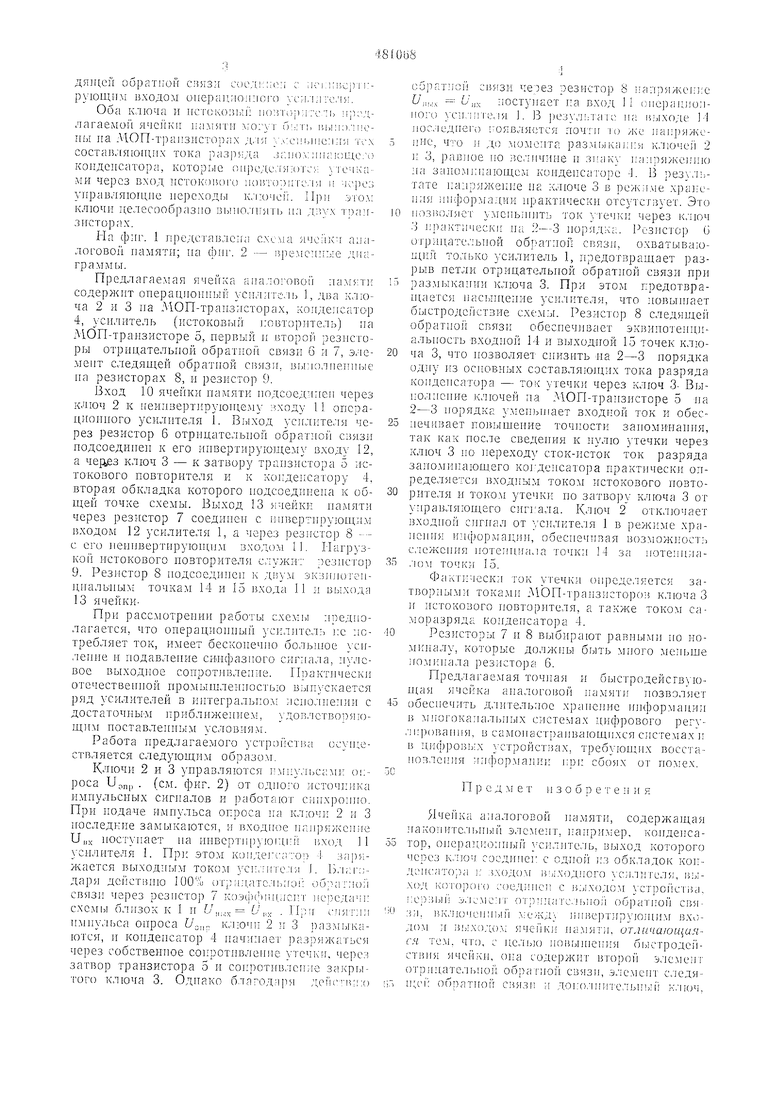

Ha фиг. 1 представлена ячеГпхЛ ааалоговои памяти; па фп1. 2 - времоппые Д|1аграммы.

Предлагаемая ячейка апалогово памяти содержит операпиоппыи успллтс.1ь 1, два ключа 2 н 3 па МОП-трапзпсторах, коидепсатор 4, усилитель (пстоковый 1:о1зторптель) па МОП-транзисторе 5, первый п второй резисторы отрицательпой обратной связи 6 и 7, элемент следящей обратной связи, вылолиеппгяе иа резисторах 8, и резистор 9.

Вход 10 ячейки памяти подсоеднпс через ключ 2 к неиивертнруюн,е,му входу 11 операционного уснлптеля 1. Выход усилителя через резистор 6 отрицательной обратной связи нодсоединен к ето инвертирующему входу 12, а чецез ключ 3 - к затвору транзистора 5 истокового повторителя и к конденсатору 4, вторая обкладка которого подсоединена к общей точке схемы. Выход 13 } чейкЕ памяти через резистор 7 соедипен с инвертирующим входом 12 усилителя 1, а через резистор 8 - с его пеппвертируюпигм входом 11. Нагрузкой истоковото повторителя служп: резистор 9. Pe3iiCTop 8 подсоедннеп к двум экзнпогепцнальным точкам 14 и 15 входа 11 п вых)да 13 ячейкиПри раесмотрепнн работы схемы предполагается, что онерационный усилитель i:e потребляет ток, имеет бесконечно больнюе уснлепне н подавление синфазного сигнала, нулевое выходное сонротнвление. Практнчески отечестве ИИ ой промы нленпостью выпускается ряд усилителей в интегральном нспо.тненин е достаточным нрпблнженнем, удонлетворяюЩ1ГМ ноетавленным условиям.

Работа нредлагаемого ycTpoiicTiia осун1,ествляется следующим образолг

Ключи 2 и 3 управляются нмнульсг. о::и

РОС

опр

нмиульсных сигналов и работают синхроп о. При подаче импульса онроса на 2 и 3 иоследние замыкаются, и входное напряжеппе и„х ноступает па иивертп)ую1дн 1 ГАОД 11 хнлителя 1. При этом копдегс;г:о) i заряжается выходным токо:а усил1 те:1 : даря действию 100% (тра;1атсл1,ио1: связи через резистор близок к I н L

имнульса опроса U,,., ключи 2 н d размыкаются, н конденсатор 4 начинает разряжатьс.я через собственное сопротнвленне утечк.г, через затвор транзистора 5 н сонротнвлеипе закрытого ключа 3. Однако благодаря ;1,(

оопатноп

f/;:s;x - 1-

ного тнл ос,1еднег()

ПНе, Ч;0 п

н 3, равное по ; слнчние и зпаку палряжеишо на заном П1ающс;м кондепсато1)е 4. В .1ьтате нанряженне на ключе 3 в режиме хранения 1нформадии нрактическн отс тствует. Это

0 позволяет ток течки через ключ 3 iipaivTHiecKif на 2-3 порядка. Рознстор и О1рицатсльной обратной связи, охватываюн|,нй только усилитель 1, предотвращает разрыв петли отрицательпой обратиой связи при

5 размыкании ключа 3, При этом предотвраП1,ается пасьпцение усн.тителя, что новынгает быстродействие схемы. Резистор 8 следяиге обратгюн связи обеспечнвает эквипотенднальпость входной 14 и выходной 15 точек ключа 3, что нозволяет снизнть на 2-3 порядка одну из основных составляюндих тока разряда конденсатора - ток утечки через ключ 3- Выполпенне ключей па МОП-транзнсторе 5 на 2-3 порядка умеп зП1ает входной ток и обеспечивает по)5ышение точности заном шання, так как после сведения к нулю утечки через ключ 3 но переходу сток-исток ток разряда заном П ающ.его ко денсатора практически онределяется входным нстокового новто0 рителя и током утечки по затвору ключа 3 от унрав;1яющего енпала. Ключ 2 отключает входной снгнал от снлителя 1 в режиме храпеиия информации, обесиечивая возможность слежения потеппнала точки Н за потеппна5 лом точки 15.

Фактически ток утечки определяется затворнымн токами МОП-транзисторо;; ключа 3 1Г истокового повторителя, а также током саморазряда конденсатора 4.

0 Резисторы 7 п 8 вг тбнрают равными но но.миналу, которые должны быть много меньще го:.11П1ала резистора 6.

Предлагае.мая точная и быстродейсгвуюп(ая ячейка аналоговой памяти позволяет

45 обеепечить длительное хранепне ннформации в :,1ногокапальпых ср1стемах н.нфрового рег лпроваппя, в сад10настра1П5ающ1пхся снстемах и в нцфровых .ттройствах. требуюн;нх восстановления ин(|)ор-мании при сбоях от номех.

П р е д м е т п з о б р е т е н н я

Ячейка аналоговой па.мяти, еодержащая накошгтельный элемент, нанример, конденсатор, онера 1ионный ;/сил ггель, выход которого через ключ сос-дннсп с одпоГ): из обкладок конд;ч1сатора и входом :лходпого -снл; тсли, выход KOToiioio оедгшсп с ;;лходом CT)oiicTBci, i:ep3bni э. oTpinaTc.iBHoii обратной свя- зи. 1И-:люче11;11)Й л:е/кд ппве)т;гру10Н ПМ входом н выхо.Ч()м ячейк , ит.тчаклцияся те.1, что, с нел1))о Н01илн1епия быстродействия ячейки, она содержит второй элемент ()трннател1.110 об|)атно:1 связи, э.:еме гг следяпй псч; обратной связи и Д01;олнительпьм к.П(;ч.

выход которого соединен с неиивертируюпи) входом операционного усилителя, одни из его входов подключен к шине опроса, а другой вход - к входной шине, выход онерацио}1ного усилителя через второй элемент отрицательнол ооратнои снязи соединен с его инвертирующим входо г, выход ячейки намяти через элемент следян1ей обратной связн соедннеп с иеинвертируюниш входом онерационпого усилителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка аналоговой памяти | 1978 |

|

SU729643A1 |

| Пьезополупроводниковый стабилизатор постоянного напряжения | 1980 |

|

SU926636A1 |

| Пиковый детектор | 1979 |

|

SU1170362A1 |

| Аналоговое запоминающее устройство | 1974 |

|

SU510752A1 |

| Генератор импульсов | 1973 |

|

SU491198A1 |

| ИНТЕГРАТОР ТОКА | 2010 |

|

RU2442177C1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU830583A1 |

| ЯЧЕЙКА ПАМЯТИ СТАТИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2012 |

|

RU2507611C1 |

| Аналого-цифровой интегратор | 1977 |

|

SU732905A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1065889A1 |

U,

опр

Фиг 2

Авторы

Даты

1975-08-15—Публикация

1974-05-23—Подача