Изобретение относится к области вычислительной техники и может быть использовано как в специализированных вычислительных устройствах, так и в различных измерительных приборах.

Реализации известных алгоритмов для нахождения функциональных зависимостей вида y-f(x), в том числе y ogax, зачастую весьма сложны, с небольшим быстродействием и невысокой точностью.

Цель изобретения - повышение быстродействия и точности, расширение динамического диапазона вычислений.

Это достигается в предлагаемом логарифмическом устройстве путем преобразования исходного сигнала х в величину выходного сопротивления матрицы R,r f(x), а именно , где N E(x), Е - функция «антье, с последуюш,им умнолсением этой величины на постоянный коэффициент log 2 (Л - основание искомого логарифма), для чего устройство содержит входной запоминающий регистр, сдвигающий регистр, дешифратор, схемы совпадения «И, матрицу сопротивлений с ключами, множительное устройство.

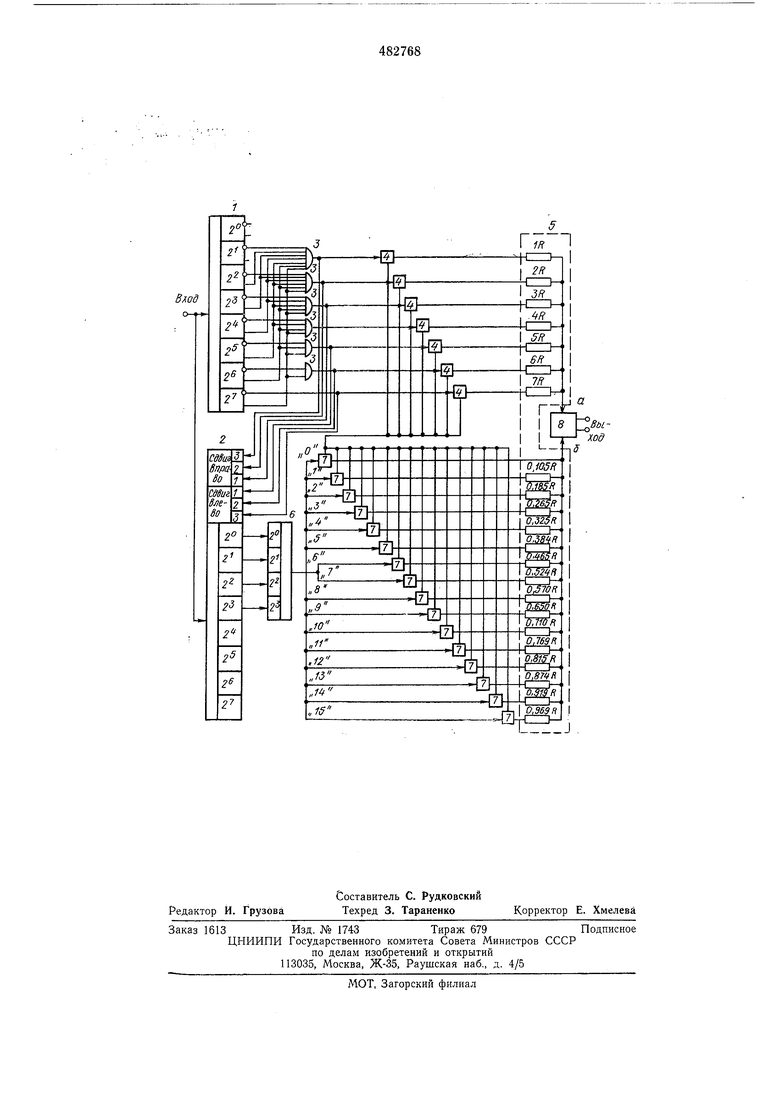

На чертеже представлена блок-схема логарифмирующего устройства, где 1 - запоминающий регистр; 2 - сдвигающий регистр; 3 - схемы совпадения 4 - ключи; 5 - резисторная матрица; 6 - дешифратор; 7 - ключи; 8 - блок умножения.

В качестве примера рассмотрим логарифмирующее устройство с восьмиразрядным запоминающим регистром и с дешифратором на 16 выходов.

С входом логарифмирующего устройства связаны параллельно входы запоминающего регистра 1 и сдвигающего регистра 2. Каждый

из единичных выходов 2, 2 . . ., 2 триггеров запоминающего регистра соединен с входом одной из схем совпадения «И 3, предназначенных для выделения из двоичного кода числа N старщего значащего разряда, остальные

входы каждой из схем «И 3 - с нулевыми выходами триггеров последующих старших разрядов. Каждый из выходов схем «И 3 подсоединен к управляющему входу одного из ключей 4, предусмотренных для подключения

сопротивлений R, 2R, 3R, . . ., или 7R матрицы 5 сопротивлений последовательно к части матрицы с дробными значениями R, а единичный выход 2 триггера запоминающего регистра 1 - непосредственно к управляющему входу ключа 4, стоящего в цепи сопротивления матрицы 5. Выходы схемы «И 3 (кроме схемы «И, соединенной по входу с единичным выходом триггера 2) и единичный выход 2 триггера связаны также с управляющими входами сдвигающего регистра 2 таким образом,

что при вводе в запоминающий регистр 1 кода чис. ;V со старшим значащим ргиридом (2, 2 или 2).сдвигаю1Я:1Гж регистр 2 произво.дит сдвиг кода числа N нЬ 3,2 или 1 разряд вправо соответственно, дл числа Л со старшим значащим разрядом,., 2 или 2 - 1,2 или 3 разряда влево соответственно.

Выходы 2°-2 сдвигающего регистра соединены с входами 2°-2 дешифратора 6, а выходы последнего - с управляющими входами ключей 7, стоящих соответственно в цепях сопротивлений 0,OOOR, 0,105R, 0,185R, 0,265R, 0,325R, 0,384R, 0,465R, 0,524R, 0,570R, 0,650R, 0,710R, 0,769R, 0,815R, 0,874R, 0,919R, 0,969R, дробной части матрицы 5.

Общая точка схемы а, объединяющая вторые выводы сопротивлений кратных /, является одним выходом матрицы 5, общая точка схемы б, объединяющая вторые выводы сопротивлений меньших R, - другим выходом матрицы 5. Выходы а, б матрицы 5 соединены с входами множительного устройства, предназначенного для умножения величины У экв атрицы на значение log 2 с целью получения окончательного результата вычисчения

log„Л/-Ig2Л.lq,,2.

Устройство работает следующим образом. Любое число N может быть представлено как

,a(k)2

гдеа() -вес соответствующего двоичного

разряда числа N.

В логарифматоре применен алгоритм фор 1ирования значения log Л с абсолютной но1рещностью не более 0,015

log „ N { Rin+ (0,57) -« + (0,57)-- (0,43) +

+ (G, (0,43)2-Ь . . . + + . . .+(0,57) .(0,43)-I I log. 2, где N + . . .+2°:

n, m, I, i,. .., 1,0 - показатели степеней значащих разрядов кода числа iV, расположенные в порядке убывания;

р - количество значащих разрядов (членов ряда) числа

/V;

Р - номинальное значение сопротивления резисторов, составляющих матрицу.

Сопротивления матрицы могут быть также рассчитаны по таблице и обеспечить более высокую точность вычисления.

Указанное уравнение позволяет вычислять ;исла N, представленные в двоичном коде, а также дает возможность судить о величине погрешности логарифмирования в зависимости от степени округления числа V, за счет исключения некоторого числа младших разря;:ов. Это выражение получено в результате установленной закономерности и периодичности числовых значений логарифмов чисел Л, анализируемых в интервале О-128 и вычисленных с помощью логарифмических таблиц.

Определение номиналов матриц сопротивлений проводилось не в зависимости от величин коэффициентов данного выражения, которое менее удобно для этой цели, а исходя из следующих положений.

Показатель степени старшего значащего разряда числа Л , представленного в двоичном

коде, численно равен характеристике log2A Пример: для . 2 + 2 + 2° 99, где показатель старшего значащего разряда равен 6 Iog2 99 6, ...

Предварительно вычислив любым из известиых способов (с помощью таблиц, что более удобно) мантиссы логарифмов чисел в интервале 2 , получается массив исходной информации, достаточный для вычисления с такой же точностью лога рифмов всех чисел А ,

меньших 2 , т. е. для вычисления мантисс логарифмов чисел необходимо умножать эти числа на , где т - старший значащий разряд числа А. После этого значение мантиссы вновь полученного числа берется из

известного массива логарифмов чисел в интервале , что аналогично сдвигу кода числа А вправо на т-k разрядов. Для вычисления мантисс логарифмов чисел используется тот же массив исходной информации, но вычисления проводятся с погрешноm-k

стью, зависящей ОТ ,

где ,

m-k

причем в значение Е 2 входят лишь ве1 1

совые значения из значащих младщих разрядов кода числа А.

Таким образом для вычисления мантисс логарифмов чисел необходимо разделить эти числа на 2 , после чего значение мантиссы вновь полученного числа берется из известного массива логарифмов чисел в

интервале , что аналогично сдвигу кода числа А влево на т-k разрядов.

Исходная информация в предложенном устройстве представлена в виде номиналов сопротивлений, кратных R, для вычисления характеристики и номиналов сопротивлений R, численные значения которых соответствуют мантиссам логарифмов чисел в интервале 2-2 + , вычисленных табличным способом. Выбор необходимого значения логарифма числа осуществляется с помощью ключей 4 и 7, подключающих к выходу логарифмирующего устройства два последовательно соединенных сопротивления - одно из матрицы целых R, второе - из матрицы дробных R.

Один коммутирующий вход каждого ключа 4 соединен с соответствующим сопротивлением, а вторые входы ключей 4 и 7 целой и дробной матриц - между собой. Управляющие входы ключей 4 соединены с выходами схем 3 совпадения, выделяющими старший значащий разряд хода числа Л , и с выходами дешифратора 6. Количесттю выходов дешифратора panno количеству номиналов сопротивлений дробной матрицы и выбирается в соответствии с необходимой потрешностью вычисления и объемом устройства. При вычислении чисел с максимально возможным числом разрядов, равным восьми, и шестнадцати нредварительно вычисленных значеиий мантисс логарифмов чисел от 16 до 31 количество сдвигаюших разрядов равно шести, т. е. три разряда для сдвига влево и три разряда для сдвига вправо.

Устройство работает следуюндим образом.

При введении кода числа в заноминаюшг1Й регистр 1 и сдвигающий регистр 2 (например, Л 2 + 2« + 2Ч-23 + 20 217) с единичного выхода 2 триггера поступает управляющий сигнал на ключ 4, стоящий в цепи 7R, и на управляющий вход сдвигающего регистра 2 «сдвиг влево на 3. При этом ключ 4 переходит в открытое состояние, подключив сопротивление 7R к ключам 7, и осуществляется сдвиг кода числа Л на 3 разряда влево. В дешифратор 6 через его входы 2°-2 заносятся значения триггеров кода числа N 2, 2, 2 и 2 соответственно, т. е. дешифрируется сумма 23 + .

С выхода дешифратора 6 «II появляется сигнал, который переводит ключ 7, стоящий в цепи 0,7697, в открытое состояние, подключив последовательно сопротивлению 7R сопротивление 0,769/. Сопротивление матрицы 5 между точками а и б при этом составляет R кв - 7,769/, которое умножается в блоке 8 на постоянный коэффициент log 2, с клемм «Выход снимается результат вычисления .

Таким образом, устройство позволяет получать с наперед заданной точностью значения логарифмов по любому основанию ряда чисел от 1 до /V. При этом достигается быстроденсгвне, ограниченное тотько BiiOMeiieA форл1ировання с выхода дешифратора управляющего сигнала и временем срабатывании одного из ключей матрицы дробных значений

R. Варьирование числом разрядов заноминающего, сдвигающего регистров и дешифратора обеспечивает при заданной точности требуемый динамический диапазон входных сигналов, а простота устройства, использование сернйно выпускаемых микросхем, например серии «Талисман, высокий показатель надежности и экономической эффективности устройства по сравнению с универсальнымн ЦВМ и аналоговыми логарифматорами.

Предмет изобретения

Логарифмирующее устройство, содержащее

запоминающий раствор, прямые и HFmepciibie выходы соответствующих разрядов которого подключены к многовходовым схемам «И, выходы схем «И, а также выход старшего разряда запоминающего регистра подключены

к управляющим входам ключей первой группы, отличающееся тем, что, с целью повышения точности вычисления, устройство содержит сдвигающий регистр, дешифратор, вторую группу ключей, блок умножения и две резпсторных матрицы, выходы которых подключены к входам блока умножения, выход которого соединен с выходом устройства, входы первой резисторной матрицы через ключи первой

и второй групп соединены с входами второй резисторной матрицы, вход запоминающего регистра соединен с входом сдвигающего регистра, соответствующие разрядные выходы которого через дешифратор подключены к уг;равляющим входам ключей второй группы, а выходы соответствующих ммоговходовых схем «И соединены с соответствующнми входамп сдвига сдвигающего регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий преобразователь функций вида у= | 1972 |

|

SU481918A1 |

| Устройство для логарифмирования чисел | 1980 |

|

SU926655A1 |

| Следящий функциональный преобразователь | 1976 |

|

SU634308A1 |

| Цифровой логарифматор | 1975 |

|

SU603996A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1972 |

|

SU448459A1 |

| Цифровое устройство для вычисления логарифма числа | 1979 |

|

SU1003082A1 |

| Устройство для логарифмирования | 1977 |

|

SU615486A1 |

| Цифровое логарифмирующее устройство | 1976 |

|

SU624233A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 2016 |

|

RU2633095C1 |

| Логарифмирующее устройство | 1976 |

|

SU634272A1 |

Авторы

Даты

1975-08-30—Публикация

1972-11-27—Подача