(54) СИНТЕЗАТОР ЧАСТОТ

вертой схем совпадения соединены с выходом второго формирователя импульсов.

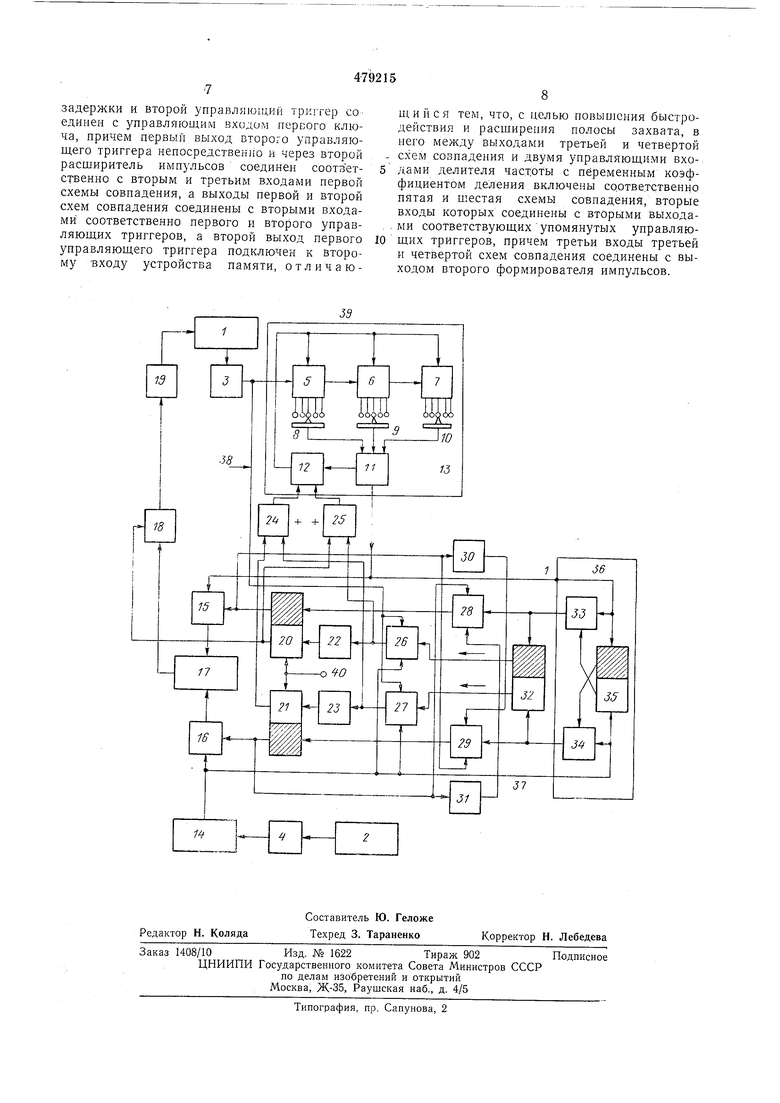

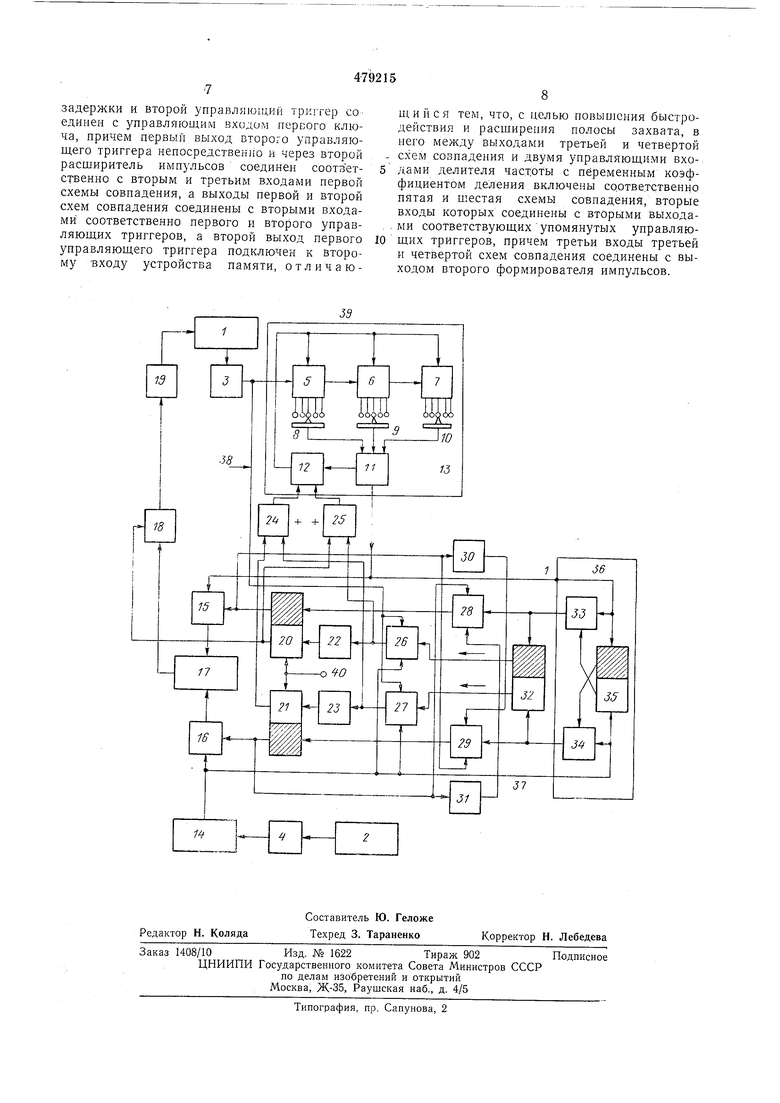

На чертеже дана функциональная схема предлагаемого синтезатора частот.

Предлагаемый синтезатор частот содержит управляемый генератор 1, опорный генератор 2, второй формирователь импульсов 3, ..первый формирователь импульсов 4, счетчики импульсов 5, 6 и 7, переключатели 8, 9 и 10 .коэффициента деления частоты, схему совпадения 11, схему «ИЛИ 12, делитель частоты с переменным коэффициентом деления 13, делитель частоты с постоянным коэффициентом деления 14, второй ключ 15, первый ключ 16, фазовый детектор 17, устройство памяти 18, фильтр нижних частот 19, первый управляющий триггер 20, второй управляющий триггер 21, первый элемент задержки 22, второй элемент задержки 23, щестую схему совпадения 24, .пятую схему совпадения 25, третью схему совпадения 26, четвертую схему совпадения 27, первую схему совпадения 28, вторую схему совпадения 29, первый расщиритель импульсов 30, второй расщиритель импульсов 31, триггер памяти частотной ощибки 32, схемы совпадения 33 и 34, триггер 35, различитель знака частотной ошибки 36, цепь опорного сигнала 37, цепь синхронизируемого сигнала 38, цепь сброса 39, клемму ввода импульсов предварительной установки 40.

Сигналы управляемого и опорного генераторов 1 и 2 соответственно через второй и первый формирователи импульсов 3 и 4 подаются на входы делителей частоты с переменным и постоянным коэффициентами деления 13 и 14. Управляемый делитель частоты 13 содержит счетчики импульсов 5, 6, 7, выходы которых через переключатели 8, 9 и 10 коэффициента деления частоты подключены к входам схемы совпадения 11, выход которой является выходом этого делителя частоты. Выход схемы совпадения И через схему «ИЛИ 12 связан с цепью 39 сброса. Схема «ИЛИ 12 имеет еще два входа, являющиеся управляющими входами делителя частоты с переменным коэффициентом деления 13. Выходы делителей частоты с переменным и постоян ным коэффициентами деления 13 и 14 соответственно подключены к первому и второму входам различителя знака частотной оЩибки 36 и через второй и первый ключи 15 и 16 - к входам фазового .детектора 17. Выход фазового детектора 17 через устройство памяти 18 и фильтр нижних частот 19 подключен к управляющему входу генератора 1. Различитель знака частотной ошибки 36 состоит из триггера 35, запускаемого по установочным входам сигналами делителей частоты с переменным и постоянным коэффициентами деления 13 и 14, и двух схем совпадения 33 и 34, одни из входов которых связаны с установочными входами триггера 35, а вторые - перекрестно с выходами упомянутого триггера 35. Выходы схем совпадения 33 и 34 являются первым и вторым выходами различителя знака частотной ощибки 36 и подключены к установочным входам триггера памяти частотной ощибки 32 и к первым входам первой и второй схем совпадения 28 и 29. Первый и второй выходы триггера памяти частотной ощибки 32 подключены к первым входам соответственно третьей и четвертой схем совпадения 26 и 27, вторые входы которых подключены к выходу делителя частоты с постоян-ным коэффициентом деления 14, а третьи - к выходу второго формирователя импульсов 3. Выход третьей схемы совпадения 26 через последовательно соединенные первый элемент задержки 22 и первый управляющий триггер 20 соединен с управляющим входом второго ключа 15, при этом первый выход первого управляющего триггера 20 непосредствеино и через первый расширитель импульсов 30 соединен -с вторым и третьим входами второй

схемы совпадения 29. Выход четвертой схемы совпадения 27 через последовательно соедииенные второй элемент задержки 23 и второй управляющий триггер 21 соединен с управляющим входом первого ключа 16, при этом

первый ВЫХОД второго управляющего триггера 21 непосредственно и через второй расширитель импульсов 31 соединен с вторым и. третьим входами первой схемы совпадения 28. Входы пятой схемы совпадения 25 соедийены с выходом третьей схемы совпадения 26 и вторым выходом первого управляющего триггера 20. Входы щестой схемы совпадения 24 связаны с выходом четвертой схемы совпадения 27 и вторым выходом второго управляющего триггера 21. Выходы пятой и щестой схем совпадения 24 и 25 подключены к управляющим входам делителя частоты с переменным коэффициентом деления 13. Второй выход первого управляющего триггера 20 подключей к второму входу устройства памяти 18. Первый и второй выходы различителя знака частотной ощибки 36 соединены соответственно с первыми входами первой и второй схем совпадения 28 и 29, а их выходы соединены с вторыми входами соответственно первого и второго управляющих триггеров 20 и 21.

Сиитезатор частот работает следующим образом.

Пусть, например, управляющие триггеры 20 и 21 устанавливаются в положение «1 (как показано на чертеже), а частота управляемого генератора 1, поделенная делителем частоты с переменным коэффициентом деления 13,

больще частоты опорного генератора 2, поделенной делителем частоты с постоянным коэффициентом деления 14. При этом начальная расстройка больше полосы захвата, но меньше полосы удержания. В этом случае на выходе схемы совпадения 33 различителя знака частотной ошибки 36 появляются импульсы, которые через первую схему совпадения 28 опрокидывают первый управляющий триггер 20 в положение «О, перекрывается второй

ключ 15; выборки из пилообразного напряжеиия фазового детектора 17 прекращаются, напряжение на выходе устройства намяти 18 падает до нуля, следовательно, частота управляемого генератора 1 быстро уменьшается. Одновременно с размыканием второго ключа 15 импульсы с выхода схемы совпадения 33 устанавливают триггер памяти частотной ошибки 32 в положение, при котором разрешаюш,ий потенциал прикладывается к первому входу четвертой схемы совпадения 27. Поэтому при совпадении импульсов в цепях 37 и 38 на выходе четвертой схемы совпадения 27 ПОЯВЛЯЮТСЯ импульсы, которые через второй элемент задержки 23 подаются на вход второго управляющего триггера 21 и подтверждают его первоначальное положение. Следовательно, первый ключ 16 включен, и производится запуск генератора пилообразного напряжения фазового детектора 17. Вторая схема совпадения 29 в это время закрыта низКИМ потенциалом с первого выхода первого управляющего триггера 20. Когда частота сигнала на выходе делителя частоты с переменным коэффициентом деления 13 станет меньше частоты сигнала на выходе делителя частоты с постоянным коэффициентом деления 14, появятся импульсы на выходе схемы совпадения 34 различителя знака частотной ошибки 36. При этом триггер памяти частотной ошибки 32 установится в положение, при котором разрешающий потенциал прикладывается к входу третьей схемы совпадения 26. При совпадении импульсов в цепях 37 и 38, выходной импульс третьей схемы совпадения 26 через первый элемент задержки 22 устанавливает первый управляющий триггер 20 в исходное положение, и восстанавливается поток импульсов выборок через второй ключ 15. Кроме того, вследствие действия первого элемента задержки 22 импульс с выхода третьей схемы совпадения 26 проходит через пятую схему совпадения 25 на управляющий вход делителя частоты с переменным коэффициентом деления 13 и через схему «ИЛИ 12 в цепь 39 сброса, вызывая установление в исходное состояние счетчиков импульсов 5, 6 и 7, после чего продолжается обычный режим работы этого делителя частоты. Так как выходной импульс делителя частоты с постоянным Коэффициентом деления 14 совпал с началом счета в делителе чаСтоты с переменным коэффициентом деления 13 и частота следования импульсов на выходе последнего меньше требуемой, то выборки нроизводятся из начального этапа формирования пилообразного напряжения фазового детектора 17, а для компенсации большой начальной расстройки необходимо низкое напряжение с выхода фазового детектора 17, что и достигается. Таким образом, в синтезаторе автоматически создаются благоприятные для захвата начальные условия. Для поддержания этих начальных условий в момент времени установления первого управляющего триггера 20 в исходное состояние запускается первый расширитель импульсов 30, который своим импульсом удерживает в закрытом состоянии вторую схему совпадения 29, исключая возможность опрокидывания второго управляющего триггера 21 и отключения цепи подачи импульсов делителя частоты с постоянным коэффициентом деления 14 на вход фазового детектора 17. ЕСли частота следования импульсов с выхода делителя чаСтоты с переменным коэффициентом деления 13 меньше частоты следования импульсов с выхода делителя частоты с постоянным коэффициентом деления 14, то синтезатор работает аналогично предыдуще му случаю, но прерывание потока импульсов на входе фазового детектора производится первым ключом 16. Синтезатор частот работает полностью автоматически при любых начальных полол ениях триггеров, входящих в его состав, но для уменьшения времени переходного процесса при некоторых возможных ситуациях рекомендуется первый и второй управляюшие триггеры 20 и 21 предварительно устанавливать в положение «1. Для этого одновременно с изменением положений переключателей коэффициента деления частоты 8, 9, 10 в цепь, связанную с клеммой 40, вводится импульс предварительной установки. Предмет изобретения Синтезатор частот, содержащий последовательно включенные опорный генератор, первый формирователь импульсов, делитель частоты с постоянным коэффициентом деления, первый ключ, фазовый детектор, устройство памяти, фильтр нижних частот, управляемый генератор, второй формирователь импульсов и делитель частоты с переменным коэффициентом деления, выход которого соединен через второй ключ с вторым входом фазового детектора, а также с первым входом различителя знака частотной ошибки, первый и второй выходы которого соединены с первыми входами соответственно первой и второй схем совпадения и одновременно с установочными входами триггера памяти частотной ошибки, первый и второй выходы которого подключены к первым входам соответственно третьей и четвертой схем совпадения, вторые входы которых подсоединены к второму входу различителя знака частотной ошибки и одновременно к выходу делителя частоты с постоянным коэффициентом деления ,а выход третьей схемы совпадения через последовательно соединенные первый элемент задержки и первый управляющий триггер соединен с управляющим входом второго ключа, при этом первый выход первого управляющего триггер непосредственно и через первый расширитель импульсов соединен соответственно с вторым и третьим входами второй схемы совпадения, а выход четвертой схемы совпадения через последовательно соединенные второй элемент

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1980 |

|

SU886251A1 |

| Синтезатор частот | 1981 |

|

SU987818A1 |

| Синтезатор чатоты | 1974 |

|

SU555534A1 |

| Цифровой синтезатор частот | 1981 |

|

SU1109913A1 |

| Цифровой синтезатор частоты | 1977 |

|

SU720667A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| Цифровой синтезатор частот с частотной модуляцией | 1985 |

|

SU1293840A1 |

| Синтезатор частот | 1986 |

|

SU1478328A1 |

| Синтезатор частот | 1989 |

|

SU1730720A1 |

Авторы

Даты

1975-07-30—Публикация

1973-02-05—Подача