54) ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕТЕКТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотный дискриминатор | 1978 |

|

SU790235A1 |

| Цифровой частотный детектор | 1979 |

|

SU815863A1 |

| Цифровой детектор частотно-манипулированных сигналов | 1979 |

|

SU879812A1 |

| Цифровой частотный дискриминатор | 1982 |

|

SU1037422A1 |

| Частотный детектор | 1982 |

|

SU1137563A1 |

| Устройство для моделирования дискретного радиоканала | 1983 |

|

SU1103256A2 |

| Устройство для измерения искажения длительности импульсов | 1988 |

|

SU1559327A1 |

| Цифровой частотный детектор | 1984 |

|

SU1307534A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Устройство для моделирования дискретного радиоканала | 1980 |

|

SU962999A1 |

I

Изобретение относится к технике связи и может использоваться в аппаратуре систем передачи: дискретной информации.

По основному авт. св. № 79О235, известен цифровой частотный детектор, содержащий цифровой измеритель длительности импульсов, выполненный в виде соединенных последовательно опорного генератора, ключа и реверсивного счетчика импульсов, выходы которого подключены к входам элемента сравнения чисел, выходы подключенного к входу логического блока, причем установочный вход реверсивного счетчика импульсов подключен к первому выходу логического блока. Дв-,j модулированный сигнал подается на вход формирователя входного сигнала, выход которого подключен ко входу формирователя импульсов, счетному входу триггера и управляющему входу делителя частоты, прямой выход триггера подключен ко второму бходу логического блока, управляющему входу реверсивного счетчика нмпульсов и второму управляющему входу

делителя частоты, на счетньй -вход которого подключен выход опорного генератора. Выход делителя частоты подключен ко второму входу формирователя импульсов, выход которого подключен к входу расщир11теля импульсов, вььходом подключенного к управляющему входу ключа и третьему входу логического блока, второй выход которого является выходом цифрового частотного детектора Ui .

Цифровой частотный детектор работает по способу выделения парыимпульсов, в разности длительностей которых содержится разность между периодом входного частотно-манипулированного сигнала и периодом средней частоты этого сигнала. Затем длительность пары увеличивается в К раз и определяется знак и величина разности длительности имп льсов.

Недостатком цифрового частотного детектора является отсутствие возможности регулировки средней частоты детекти391

руемого сигнала, что обуслаышвает наличие искажений.

Цель изобретения - уменьшение иска жений гфн детектировании.

Указанная цель достигается тем, что в ци4ровой частотный детектор дополнительно введены два кпюч, генератор тока разряда и блок управления, причем первый выход блока у правления подг-слго™ чей к входу генератора тока .разряда,

выход которого подключен к первым вхо дам дополнительных ключей, выходы которых подключены ко второму входу расширителя импульсов, а второй выход блока управления подключен к вторым

входам дополнительных ключей, третьи входы которых поД1слючены соответственно к прямому и ifflBOpCHON-jy ВЫХОРЗ.М

триггера.

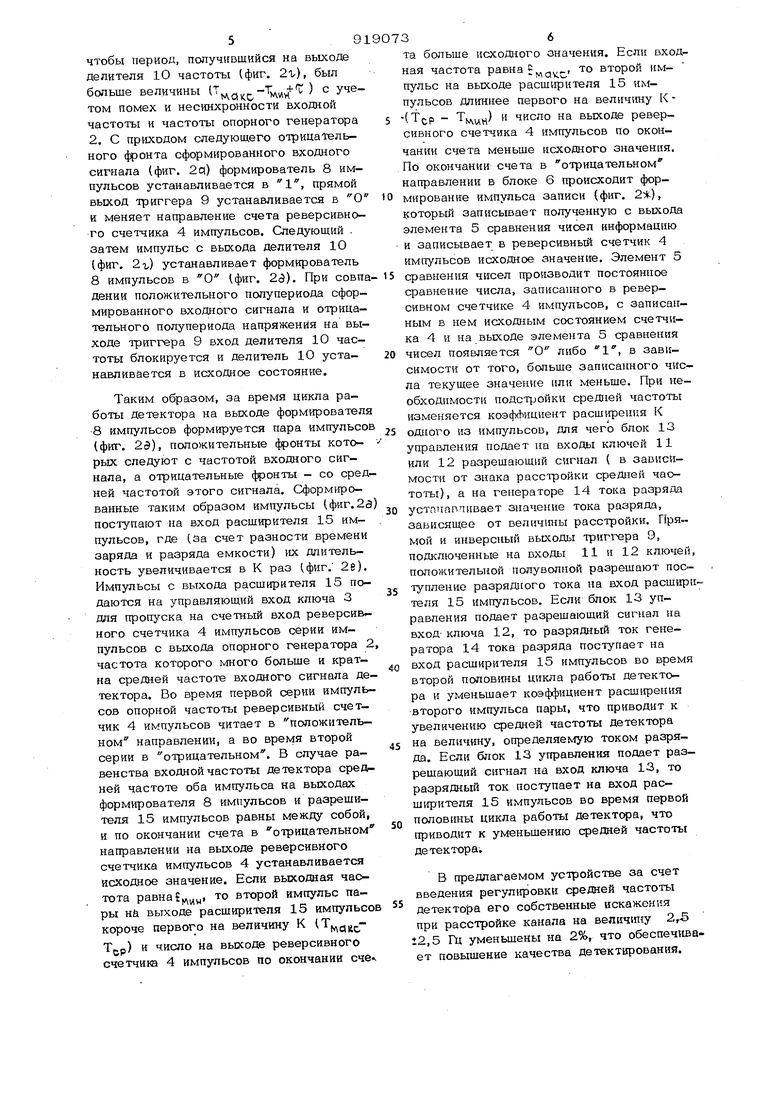

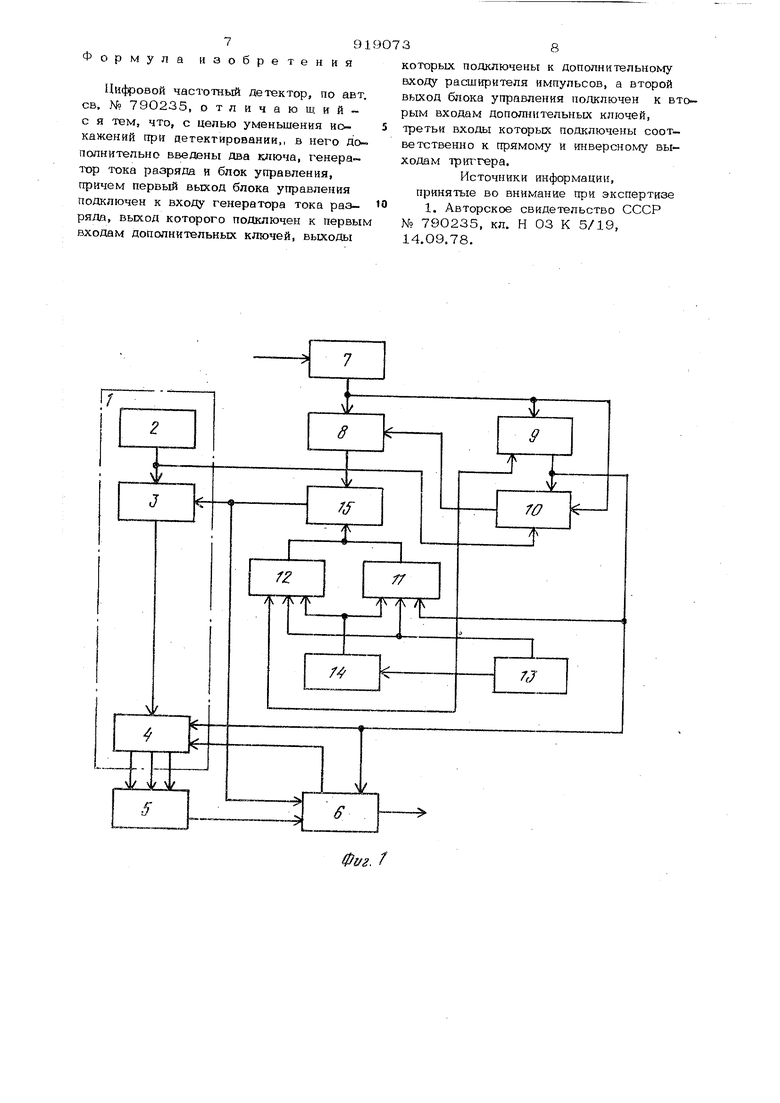

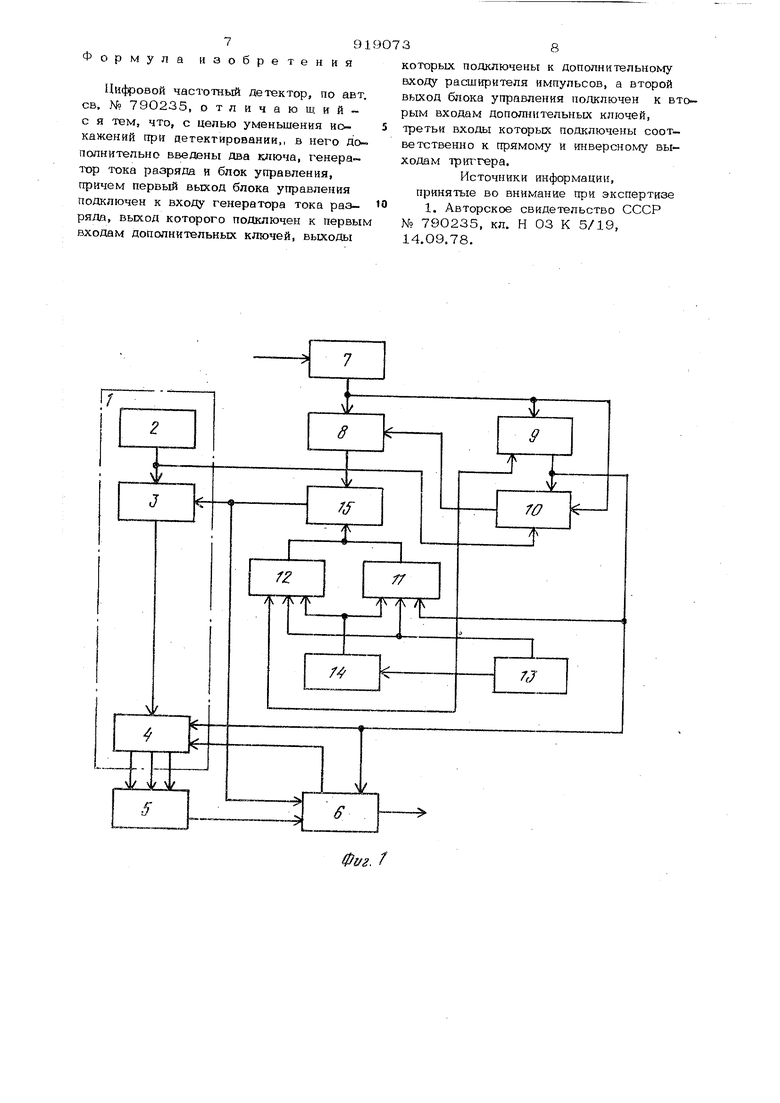

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - диаграммы, поясняющие его работяг.

Циф1эовой частоттгый детектор содержит цифровой измеритель 1 дпнгельности импульсов, выполненный в виде соеди- кенных последовательно опорного генера- гора 2, первого ключа 3 и реверсивного счетчика 4 имп -льсов, выходы которого подключены к входам элемента 5 сравнения -чисел, выхоаом подключенного к.вхо ду логического блока 6, причем установочный вход реверсивного счетчика 4 импульсов поД1Шючен к первому выходу логического блока 6, второй выход которого является выходом детектора., Демодулируемый сигнал подается на оход формирователя 7 входного сигнала, выхо которого подключен к входу формирователя 8 импульсов, c4emoN входу 1:ригг«.ра 9 и управляющему вхозу делителя

10 частоты, к cчeтнo fJ входу дегпгге.гя 10 частоты подключен выход опорного генератора 2, а выход делителя 10 частоты поД1Шючен к второму входу формирователя 8 импульсов. Прямой вькод триггера 9 подключен к второму управляющему входу делителя Ю частоты, третьему входу ключа 11, yrфaвпяюule y входу реверсивного счетчика 4 импульсо и втфому входу логического блоха 6, а инверсный выход триггера 9 по/жлючен к. третьему входу ключа 12„ Первый выход блока 13 по.дключен ко вход. генератора 14 тока разря.да, а второй выход к втсрым входам 1слючей 11 и 12 Выхо т нератора 14 .тока разряда подкл очен к первым входам кльочей 11 к 12, выходы KoitJpbDC подключены к второму , входу расширителя 15 импульсов, к пер34

вому входу которого подключен выход формирователя 8 импульсов. Выход расширителя 15 импульсов подключен к управляющему входу первого ключа 3 и третьем входу логического блока 6.

Устройство работает следующим образом.

Иа вход детектора приходит периодический частотно-манипулированный сигнал, который формщэователем 7 входного сигнала преобразуется в прямоугольны импульсы, следующие с частотой входног сигн.ала (фиг. 2а), Цикл работы детектора, совпадающий с периодом колебания на .выходе трипвра 9 (фиг.25) , состоит из ,цвух периодов входного сигнала, в каждом из которых формируется по одному информационному импульсу (фиг. 2а, 5), Начало цикла совпадает с отрицательным фронтом напряжения на выходе формирователя 7 входного сигнала (фиг. 20) вызывающим положительный фронт напряжения на прямом выходе триггера 9 (фтл 26),

Рассмотрим цикл работы детектора.

В момент прихода первого отрицательного фронта сформи1эованного импульса (фкг. 2а) выход триггера установится в i Сфнг. 25), выход форм фователя 8 импульсов установится в 1 (фиг. 25), а Делитель 1О частоты разблок1фуется и начнет деление опорной частоты (фиг.2 Одновременно .выходной сигнал т эиггера 9 управляет направлением счета реверсивного счетчика 4 импульсов таким обпазом, что если вььход триггера 9 в ед гничном состоянии, то реверсивнь01

счетчик 4 импульсо.в считает в положи(ельном направлен(И,- а если в нулевом состоянии, то счет идет D отрицательном направлении. Де..т1итзль 10 частоты вырабатывает импульсы отрица- талы-юй полярности (фиг, 2г), поступающие на второй вход формирователя 8 HivinynbcoB и устанавливающие его в О (фиг. 23). Эти импульсы имеют частоту г-(-рДгде л - цело.е число, а - средняя Чистота частотно-манипулироваиного ситиала) и сдвянуты относигельно момента запуск.а делителя 10 (фиг. 2S) на Бреыя . Величина ;выбирается из услоБ|{й/: Т,„,,,, (гдег,,д максимальный период входного колебания с учетом .зоздействия помех, мшимальный период входного колебания с учетом воэдейст.вия помех, величина п выбирается с таким расчетом, чтобы с одной сторо- iLbi перио.а делителя 1О частоты полуЧ1ШСЯ минимальным, а с другой стороны, чтобы период, получившийся на выходе делителя 10 частоты (фиг. 2г), был больше величины , У том помех и несинхронности входной частоты и частоты опорного генератора 2. С приходом следующего отрица1ельного фронта сформированного входного сигнала (фиг. 2q) формирователь 8 импульсов устанавливается в 1, прямой выход триггера 9 устанавливается в О и меняет направление счета реверсивного счет-чика 4 импульсов. Следующий . затем импульс с выхода делителя 10 (фиг. 2г) устанавливает формирователь 8 импульсов в О (фиг, 2Э). При совп дении положительного полупериода сформированного входного сигнала и отрицательного полупериода напряжения на выходе триггера 9 вход делителя 10 частоты блокируется и делитель Ю устанавливается в исходное состояние. Таким образом, за время цикла работы детектора на выходе формирователя 8 импульсов формируется пара импульсо (фиг. 2Э), положительные фронты которых следуют с частотой входного сигнала, а отрицательные фронты - со сред ней частотой этого сигнала. Сформрфованные таким образом импульсы (фиг.2а поступа от на вход расширителя 15 импульсов, где (За счет разности времени заряда и разряда емкости) их длительность увеличивается в К раз (фиг. 2е). Импульсы с выхода расширителя 15 подаются на управляющий вход ключа 3 для пропуска на счетный вход реверсив1ного счетчика 4 импульсов серии импульсов с выхода опорного генератора 2 частота которого ivffloro больше и кратна средней частоте входного сигнала детектора. Во время первой серии импульсов опорной частоты реверсивный счетчик 4 импульсов читает в положительном направлении, а во время второй серии в отрицательном. В случае равенства входной частоты детектора средней частоте оба импульса на выходах формирователя 8 импульсов и разрешителя 15 импульсов равны между собой, и по окончании счета в отрицательном направлении на выходе реверсивного счетчика импульсов 4 устанавливается исходное значение. Если выходная частота равна | у, то второй импульс пары ни выходе расширителя 15 импульсов короче первого на величину К ,сГ Tj-p) и число на выходе реверсивного счетчика 4 импульсов по окончании сче 9 36 та больще исходного значения. Если входная частота равна с,, то второй импульс на выходе расщ(фителя 15 нмпу льсов длиннее первого на величину К ( - ) и число на выходе реверсивного счетчика 4 импульсов по окончании счета меньше исходного значения. По окончании счета в отрицательном направлении в блоке 6 происходит формирование импульса записи (фиг. 2), который записывает полученную с выхода элемента 5 сравнения чисел информацию и записывает в реверсивный счетчик 4 импульсов исходное значение. Элемент 5 сравнения чисел производит постоянное сравнение числа, записанного в реверсивном счетчике 4 импульсов, с записанным в нем исходным состоянием счетчика 4 и на выходе элемента 5 сравнения чисел появляется О либо 1, в зависимости от того, больше записанного числа текущее значение или меньше. При необходимости подстройки средней частоты изменяется коэффициент расширения К одного из импульсов, для чего блок 13 управления подает на входы ключей 11 или 12 разрешающий сигнал ( в зависимости от знака расстройки средней частоты), а на генераторе 14 тока разряда устпнавливает значение тока разряда, зависящее от величины расстройки. Прямой и инверсный выходы тригх ра 9, подключенные на входы 11 и 12 ключей, положительной полуволной разрешают поступление разрядного тока на вход расшири теля 15 импульсов. Если блок 13 управления подает разрешающий сигнал на вход ключа 12, то разрядный ток генератора 14 тока разряда поступает на вход расширителя 15 импульсов во время второй половины цикла работы детектора и уменьшает коэффициент расш1фения второго импульса пары, что приводит к увеличению средней частоты детектора на величину, oпpeдeляe Iyю током разряда. Если блок 13 управления подает разрешающий сигнал на вход ключа 13, то разрядный ток поступает на вход расширителя 15 импульсов во время первой половины цикла работы детектора, что приводит к уменьшению средней частоты детектора. В предлагаемом устройстве за счет введения регулировки средней частоты детектора его собственные искажения при расстройке канала на велижгау 2,5 Гц уменьшены на 2%, что обеспечивает повышение качества детектирования.

Формула изобретения

Цифровой частотный детектор, по авт. ев, № 790235, отличающийс я тем, что, с цепью уменьшения искажений при детектировании,, в него дополнительно введены два ключа, генератор тока разряда и блок управления, причем первый выход блока угфавления подключен к входу генератора тока разряда, выход которого подключен к первым входам дополнительных ключей, выходы

которых подключены к дополнительному входу расширителя импульсов, а второй выход блока управления подключен к врым входам дополнительных ключей, третьи входы которых подключены соответственно к прямому и инверсному выходам триггера.

Источники информации, принятые во внимание при экспертизе

Фиг. /

и и LJ и ff ПП Ф1/г,г II -1Г

Авторы

Даты

1982-04-07—Публикация

1980-09-29—Подача