ного элемента, четвертый и пятый входы связаны с выходом фиксатора нуля, шестой вход - с реверсивным счетчиком, седьмой - с генератором импульсов, а выходы логического блока соединены с соответствующими входами реверсивного счетчика.

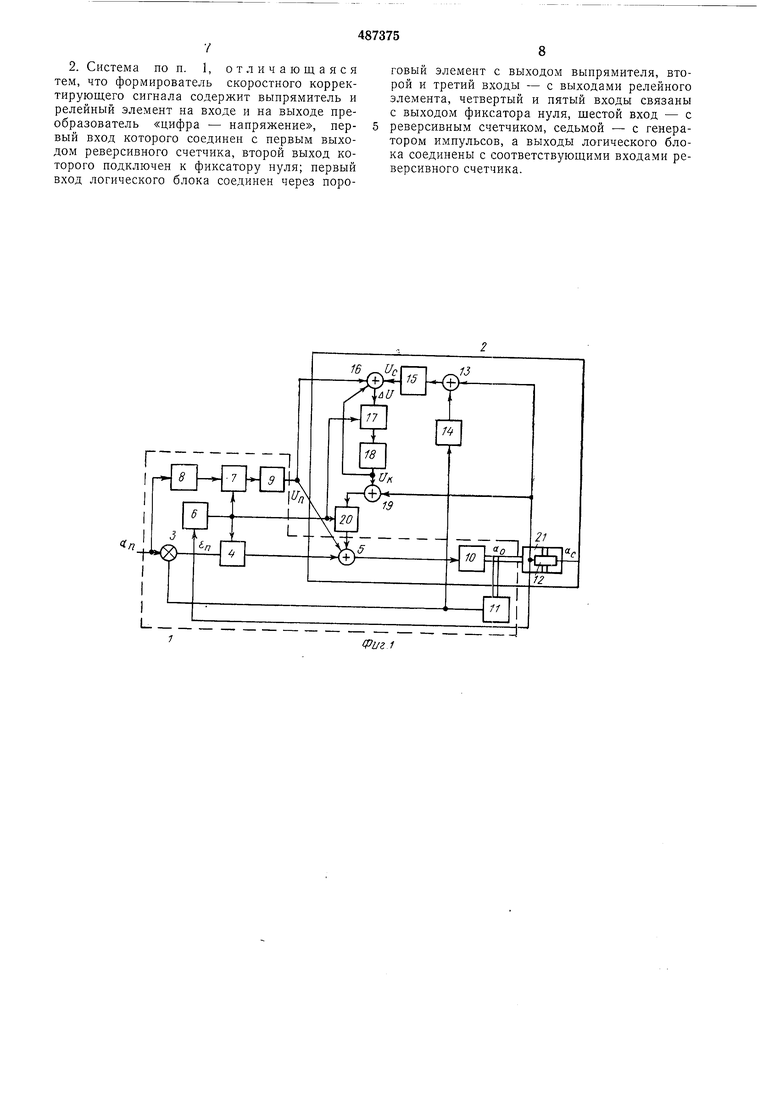

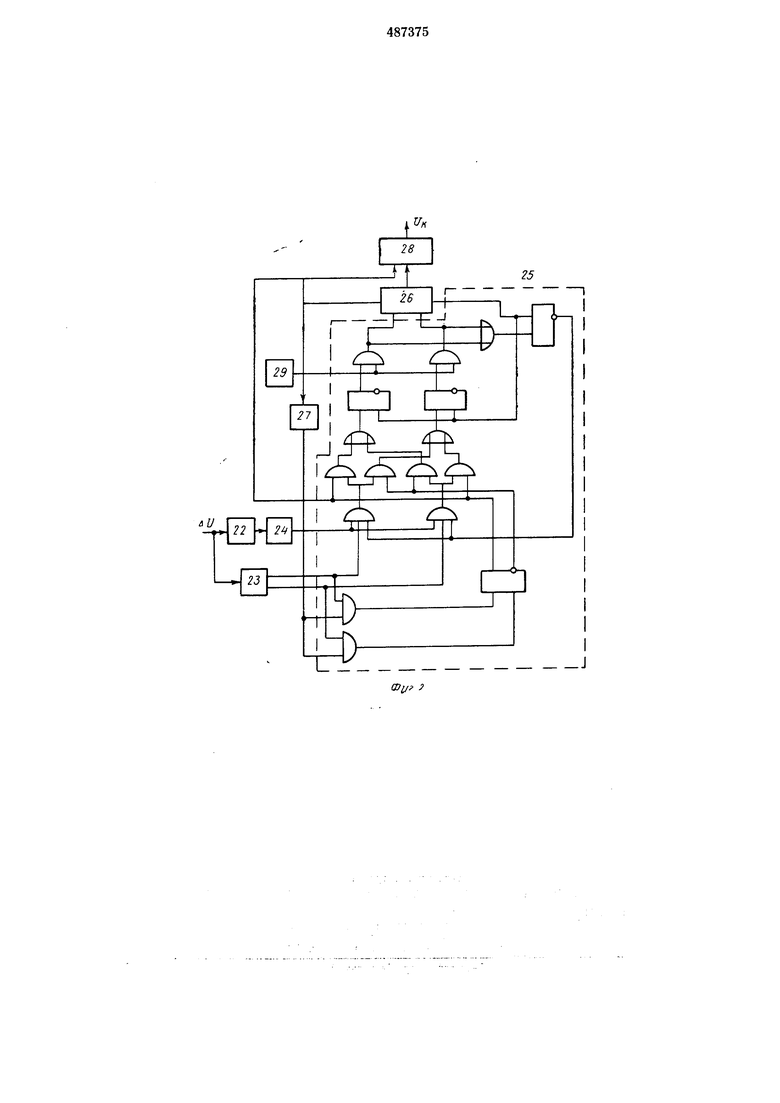

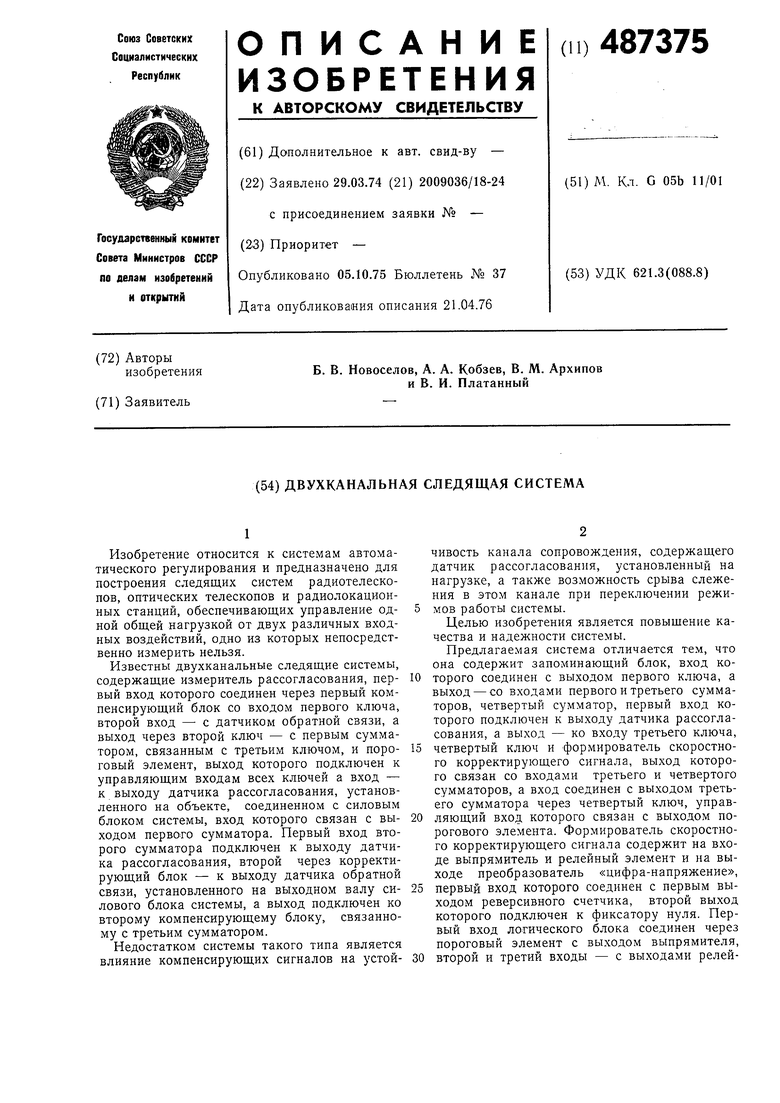

На фиг. 1 показана блок-схема предлагаемой двухканальной следящей системы; на фиг. 2 - схема формирователя скоростного корректирующего сигнала.

Двухканальная следящая система состоит из канала программного управления 1 и канала сопровождения 2. Канал 1 состоит из измерителя рассогласования 3, выход которого через ключ 4 соединен с первым входом сумматора 5; порогового элемента 6, выход которого соединен с управляющими входами ключа 4 и ключа 7, вход которого соединен с выходом компенсирующего блока 8. Выход ключа 7 соединен со входом запоминающего блока 9, выход которого соединен со вторым входом сумматора 5. Выход последнего соединен с входом силового блока системы 10, выход которого соединен с входом датчика обратной связи 11, выход которого соединен с вторым входом измерителя рассогласования 3.

Канал сопровождения 2 состоит из датчика рассогласований 12, на входы которого поданы сигнал углового положения исполнительной оси системы OQ и задающее воздействне а,с, а выход соединен с выходом порогового элемента бис первым входом сумматора 13, второй вход которого соединен с выходом корректирующего блока 14, вход которого соединен с выходом датчика обратной связи 11 канала 1. Выход сумматора 13 соединен со входом компенсирующего блока 15, выход которого соединен с первым входом сумматора 16. Второй вход последнего соединен с выходом запоминающего блока 9. Выход сумматора 16 через ключ 17 соединен с выходом формирователя скоростного корректирующего сигнала 18, выход которого соединен с третьим входом сумматора 16 и с первым входом сумматора 19, второй вход которого соединен с выходом датчика рассогласования 12, а выход через ключ 20 соединен с третьим входом сумматора 5, выход которого соединен со входом силового блока 10, выход которого соединен с объектом 21 и с одним из входов датчика рассогласований 12. Управляющие входы ключей 17 и 20 соединены с выходом порогового элемента 6 канала 1.

Формирователь скоростного корректирующего сигнала 18 (фиг. 2) состоит из выпрямителя 22 и релейного элемента 23, входы которых соединены с выходом ключа 17. Выход выпрямителя 22 соединен со входом порогового элемента 24, выход которого соединен с первым входом логического блока 25, первый и второй выходы которого соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика 26. Первый выход счетчика, объединяющий нулевые выходы триггеров, соединен со входом устройства фиксации нуля 27, а второй - со входом преобразователя «цифра - напряжение 28, выход которого соединен с одним из входов сумматоров 19 и 16. Второй и третий входы логического блока 25 соединены соответственно с первым и вторым выходами релейного элемента 23, четвертый и пятый - с выходом устройства фиксации нуля 27, щестой - с третьим выходом счетчика 26, седьмой - с выходом генератора импульсов 29, а третий выход соединен со входом установки знака преобразователя «цифра - напряжения 28.

Двухканальная следящая система работает следующим образом.

В режиме отработки программы ключи 4 и 7 замкнуты, а ключи 17 и 20 разомкнуты, и программное воздействие Од отрабатывается каналом 1. Для компенсации составляющей ощибки, пропорциональной прогнозируемой скорости нагрузки, на вход сумматора 5 поступает компенсирующий сигнал t/n с выхода компенсирующего блока 8. При достижении каналом 1 заданной точности наведения, характеризуемой величиной ошибки сопровождения ЕС. срабатывает пороговый элемент 6, выходной сигнал которого размыкает ключи 4 и 7 и замыкает ключи 17 и 20. На вход сумматора 5 поступает сигнал, пропорциональный ошибке ЕС, и запомненный на все время сонровождения в блоке 9, сигнал U (in) пропорциональный прогнозируемой скорости в момент п.

Сигнал Ни, пропорциональный скорости изменения воздействия а, формируется по методу дифференциальной «вилки путем суммирования сигналов, пропорциональных Ко и ЕС, поступающих на сумматор 13 с выходов датчика 11 (через корректирующий блок 14) и датчика 12 соответственно, и последующего дифференцирования в блоке 15.

На выходе сумматора 16 формируется сигнал At/, поступающий через открытый ключ 17 на вход формирователя 18. Если при этом модуль А(У превысит допустимую величину At/g. формирователь 18 формирует линейно нарастающий сигнал с максимальной амплитудой Af/g и длительностью Гк- Величины At/g; TK постоянны для каждого цикла коррекции.

Знак формируемого сигнала совпадает со знаком Af/.

Причем в каждом цикле коррекции линейно нарастающий сигнал алгебраически суммируется с величиной корректирующего сигнала t/K, имевшего место после предществующего цикла коррекции и представляющего собой алгебраическую сумму амплитуд Af/g предыдущих циклов.

Алгебраическая сумма UK (t) и t/n (п), формируемая в сумматоре 5, представляет собой компенсирующее воздействие для канала 2. Величина ALg выбирается равной ошибке формирования компенсирующего сигнала, соответствующей допустимой величине ощибки канала 2 ЕС. При /At// At/g выходной

Сигнал формирователя 18 остается постоянным. Величина Гк должна удовлетворять следующему соотношению

I т

пер к -р: 1

--макс

где иер - длительность переходного процесса в канале 2 на линейно нарастающее возмущение в сул1маторе 5; AQg - величина изменения скорости воздействия Ос, соответствующая величине Af/g;

ймакс - максимальное ускорение воздействия Ос.

Условие Гк пер исключает влияние положительной обратной связи, появляющейся при нарущении условия эквивалентности плечей «вилки из-за наличия люфтов, упругих деформаций и гнутий в цепи элементов 10, 12, 21.

AQ,. При выполнении условия Тк ;

терминированная составляющая сигнала /Af// не превыщает A/7g в течение цикла коррекции. Если при формировании линейно нарастающего сигнала превышение /Af// над At/ произойдет за счет действия помехи, то формирователь 18 не реагирует на данное превыщение до конца цикла коррекции.

Формирователь скоростного корректирующего сигнала 18 работает следующим образом.

В момент равенства сигналов t/n и f/c реверсивный считчик 26 находится в нулевом состоянии, что фиксируется устройством фиксации нуля 27, вход которого соединен с выходом счетчика 26.

Положим для определенности, что скорость изменения сигнала f/c вначале положительна и Af/ 0. Сигнал At/ поступает на выпрямитель 22 и релейный элемент 23. При накоплении отклонения Af/ до величины Af/,,, равной порогу срабатывания порогового элемента 24, логический блок 25 разрещает прохождение определенного количества импульсов с генератора импульсов 29 на суммирующий вход реверсивного счетчика 26. Линейно нарастающий код реверсивного счетчика 26 подается на преобразователь «цифра - напряжение 28, с выхода которого сигнал f/к поступает в сумматор 5 и на третий вход сумматора 16. Количество и частота импульсов, поступающих с генератора 29 в счетчик 26 за время цикла коррекции Г,,, определяются величиной At/jr, крутизной характеристики преобразователя 28 и временем Т,;Если после данного цикла коррекции сигнал АС/ вновь достигает величины Af/г, то процесс коррекции программного компенсирующего сигнала f/n повторяется, т. е. новая пачка импульсов поступает на суммирующий ХОД реверсивного счетчика 26. Во время поступления пачки импульсов в счетчик логическое устройство не реагирует на сигналы порогового элемента 24.

Разрешение на очередное формирование линейно нарастающего сигнала дает импульс, поступающий с выхода сигнала окончания пачки импульсов счетчика 26 в устройство фиксации нуля 27.

Знак выдаваемого с преобразователя 28 сигнала f/к определяется по сигналу устройства фиксации нуля 27 и знаку сигнала Af/, формируемого в релейном элементе 23.

При изменении знака скорости изменения сигнала f/c знак Af/ с течением времени также изменяется, что фиксируется элементом 23, и при выполнении условия /Af// Af/g логический блок 25 разрещает прохождение импульсов уже на вычитающий вход реверсивного счетчика 26.

В момент равенства величины компенсирующего воздействия канала 2 величине f/n (п) логический блок 25 по сигналу элемента 24 и знаку Af/, определяемому в элементе 23, меняет знак выдаваемого с преобразователя 28 сигнала f/,; и изменяет условия прохождения импульсов с генератора 29 на суммирующий и вычитающий входы счетчика 26. Тепепь при отрицательном Af/ логический блок 25 разрешает прохождение нмпульсов на суммирующий, а при положительном Af/ - на вычитающий вход счетчика 26.

30

Предмет изобретения

1. Двухканальная следящая система, содержащая измеритель рассогласования, первый вход которого соединен через первый компенснрующий блок со входом первого ключа, второй вход - с датчиком обратной связи, а выход через второй ключ - с первым сумматором, связанным с третьим ключом, и пороговый элемент, выход которого подключен к управляющим входам ключей, а вход - к выходу датчика рассогласования, установленного на объекте, соединенном с силовым блоком системы, вход которого связан с выходом первого сумматора; первый вход второго сумматора подключен к выходу датчика рассогласования, второй через корректирующий блок - к выходу датчика обратной связи, установленного на выходном валу силового блока системы, а выход подключен ко второму компенсирующему блоку, связанному с третьим сумматором, отличающаяся тем, что. с целью повыщения качества и надежности системы, o}ia содержит запоминающий блок, вход которого соединен с выходом

первого ключа, а выход - со входами первого и третьего сумматоров, четвертый сумматор, первый вход которого подключен к выходу датчика рассогласования, а выход - ко входу третьего ключа, четвертый ключ и формирователь скоростного корректирующего сигнала, выход которого связан со входами третьего и четвертого сумматоров, а вход соединен с выходом третьего сумматора через четвертый ключ, управляющий вход которого

связан с выходом порогового элемента.

2. Система по п. 1, отличающаяся тем, что формирователь скоростного корректирующего сигнала содержит выпрямитель и релейный элемент на входе и на выходе преобразователь «цифра - напряжение, первый вход которого соединен с первым выходом реверсивного счетчика, второй выход KOj торого подключен к фиксатору нуля; первый вход логического блока соединен через пороговый элемент с выходом выпрямителя, второй и третий входы - с выходами релейного элемента, четвертый и пятый входы связаны с выходом фиксатора нуля, щестой вход - с реверсивным счетчиком, седьмой - с генератором импульсов, а выходы логического блока соединены с соответствующими входами реверсивного счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дфухканальная следящая система | 1980 |

|

SU954923A2 |

| Цифровой демодулятор сигналов фазоразностной модуляции второго порядка | 1989 |

|

SU1716616A1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2003 |

|

RU2241273C1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1990 |

|

SU1707723A1 |

| Преобразователь перемещения в код | 1988 |

|

SU1531221A1 |

| Устройство управления гелиостатом | 1983 |

|

SU1291925A1 |

| Преобразователь перемещения в код | 1980 |

|

SU888162A1 |

| Способ управления многофазным инвертором и устройство для его осуществления | 1984 |

|

SU1458951A1 |

| Дискретный электропривод | 1977 |

|

SU809055A1 |

| Способ преобразования угла поворота вала в код и устройство для его осуществления | 1989 |

|

SU1713103A1 |

Авторы

Даты

1975-10-05—Публикация

1974-03-29—Подача