(54) ДВУХКАНАЛЬНАЯ СЛЕДЯЩАЯ СИСТЕМА

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухканальная следящая система | 1974 |

|

SU487375A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ТЕХНИЧЕСКОГО СОСТОЯНИЯ ДВИГАТЕЛЕЙ ВНУТРЕННЕГО СГОРАНИЯ И ЭКСПЕРТНАЯ СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2175120C2 |

| Двухканальная следящая система | 1973 |

|

SU470785A1 |

| Следящая система | 1983 |

|

SU1105858A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1990 |

|

SU1707723A1 |

| Электронный регулятор расхода воздуха стенда для поверки и настройки шахтных сигнализаторов метана | 1985 |

|

SU1305404A1 |

| Система управления | 1976 |

|

SU714350A1 |

| Устройство для контроля сигналов с импульсной модуляцией | 1984 |

|

SU1239871A1 |

| Следящая система | 1987 |

|

SU1499315A1 |

| Система стабилизации объекта с присоединенным упругим элементом переменной жесткости | 1988 |

|

SU1603340A1 |

Изобретение относится к системам автоматического регулирования н может быть использовано для построения следящих систем радио и оптических тёйе- скопов, обеспечивающих управление одной общей нагрузкой от двух различных входных воздействий, одно Вз которых непосредственно измерить нельзя.

По основному авт. св. № 487375 известна двухканальная следящая система, содержащая измеритель рассогласования, первый вход которого соединен через первый ксалпенсврующий блок с входом первого ключа, второй вход - с датчиком обратной связи, а выход через второй ключ - с первым сумматоре, связанным с третьим ключом, и пороговый элемент, выход которо1Ч подключен к управляющим входам ключей, а вход к выходу датчика рассогласования, установленнсяч) на объекте, соединенном с силовым блоком системы, вход которотю связан с выходом первого сумматора, первый вход второго сумматора подключен к выходу датчика рассогласования, второй через корректирующий блок - к выходу датчика обратной связи, установленногчэ на выходном валу силового блока системы, а выход подключен к второму компенсирующему блоку, связанному с третьим сумматором, пертый запоминающий блок, вход которого соединен с выходом нового ключа, а выход - с входами первого и третьего сумматоров,

to четвертьй сумматор, первый вход которого подключен к выходу датчика рассогласоэания, а выход - к входу третьего ключа, четвертый ключ в формирователь скоростного корректтфуюодего сигнала,

15 выход которого связан с входами третьего н четвертого сумматоров, а вход соединен с выходом третьего сумматора через четвертый ключ, управляюошй вход которого связан с выходом порогового

20 элемента.

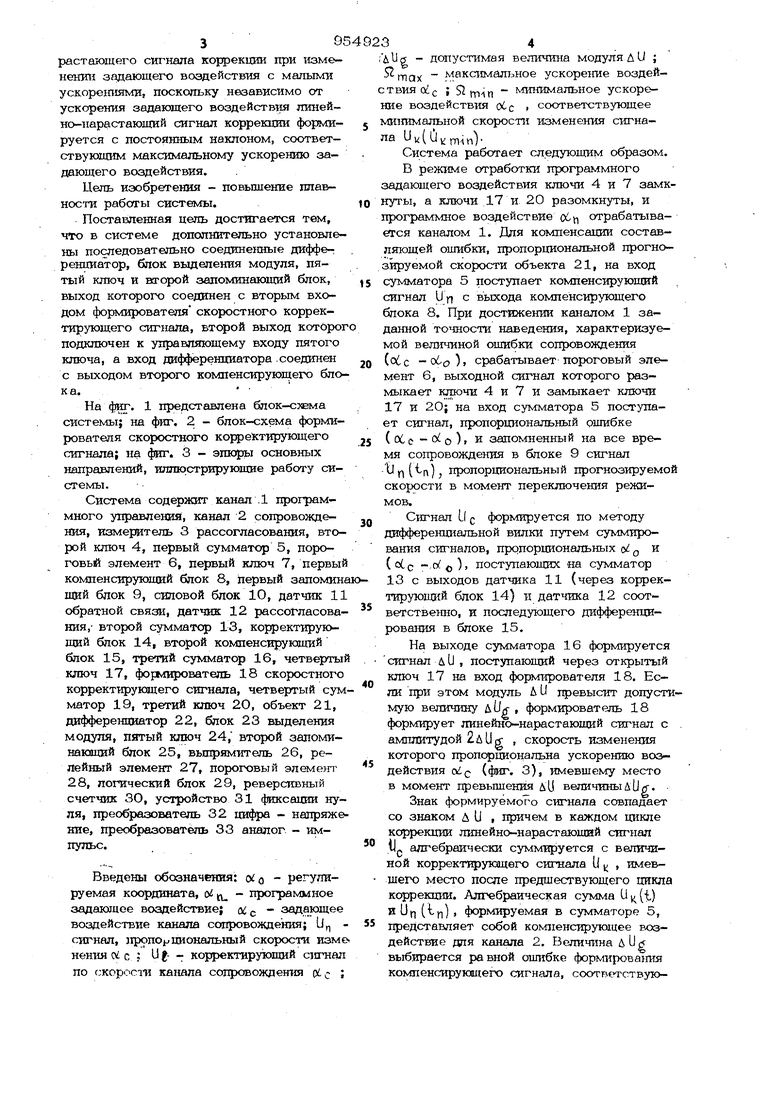

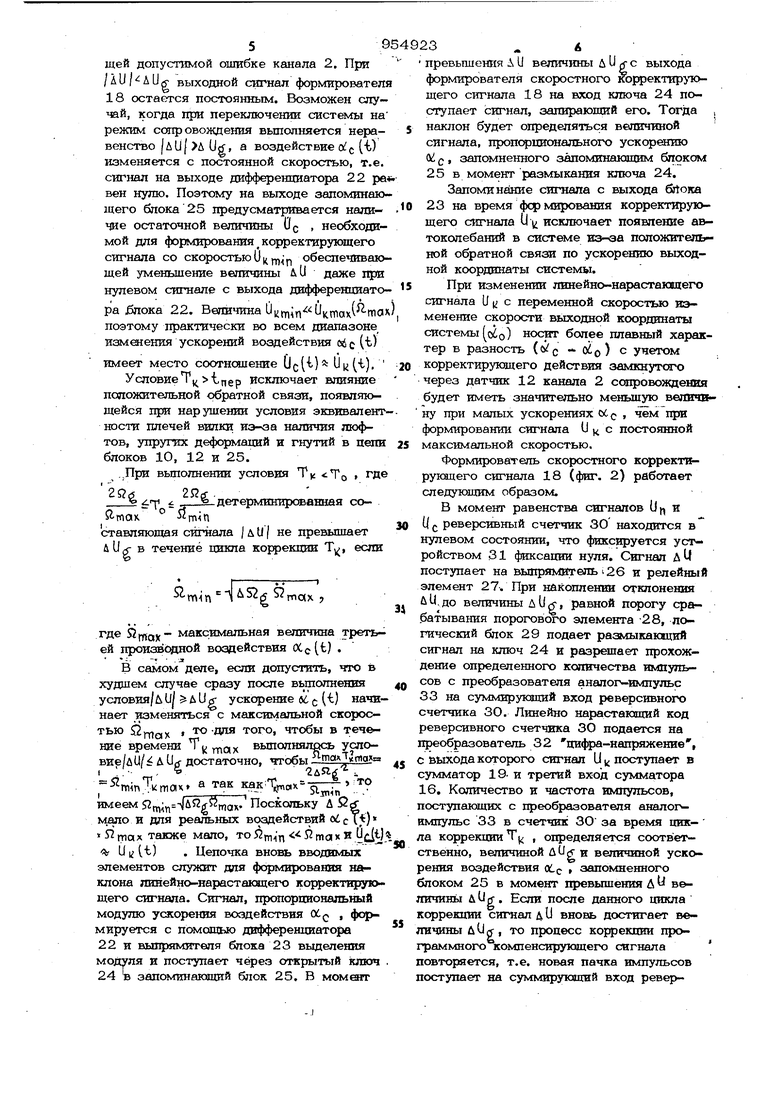

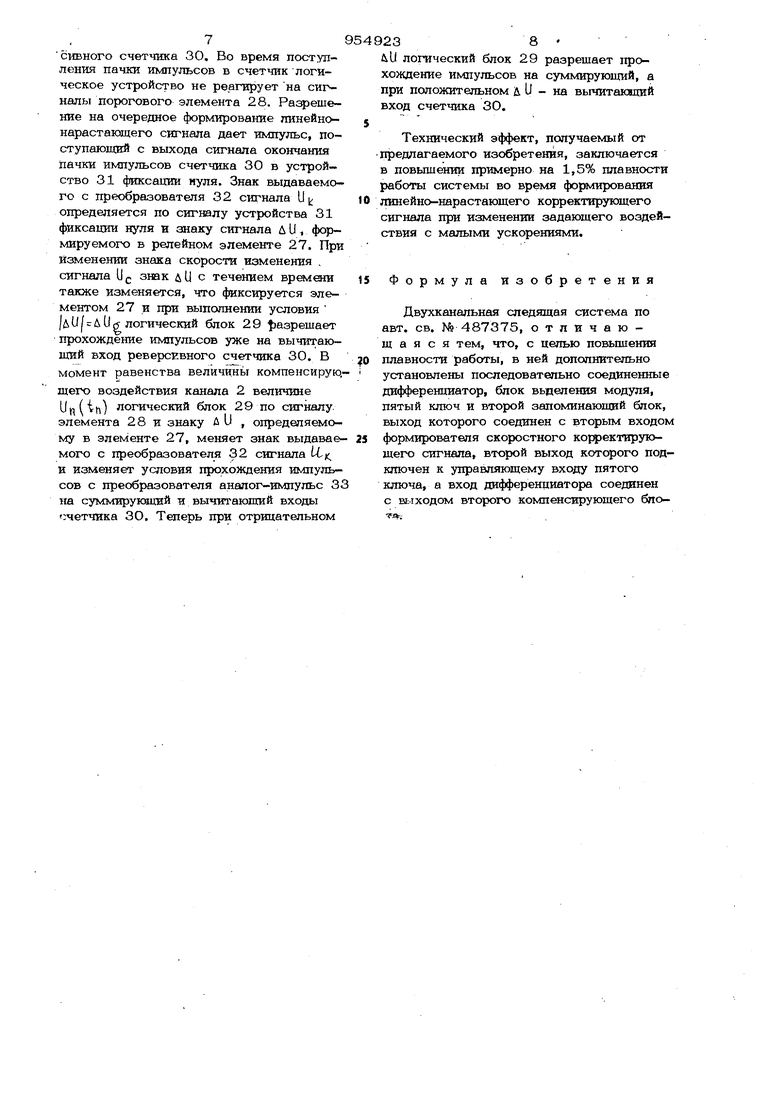

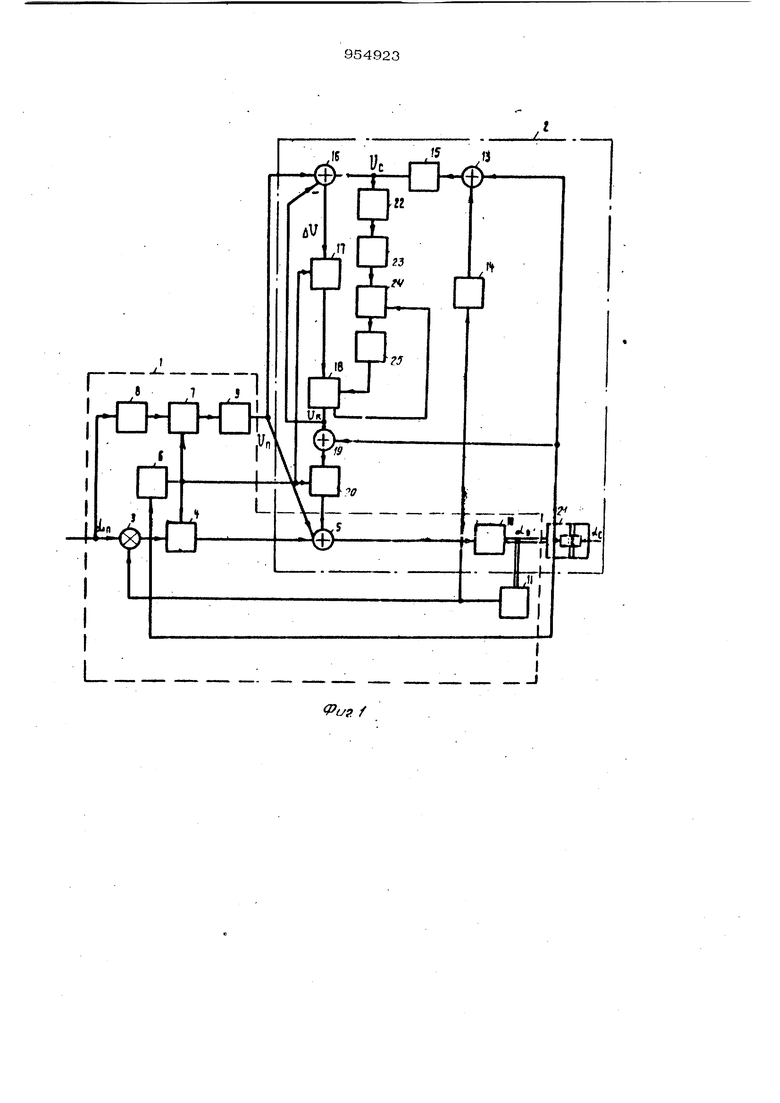

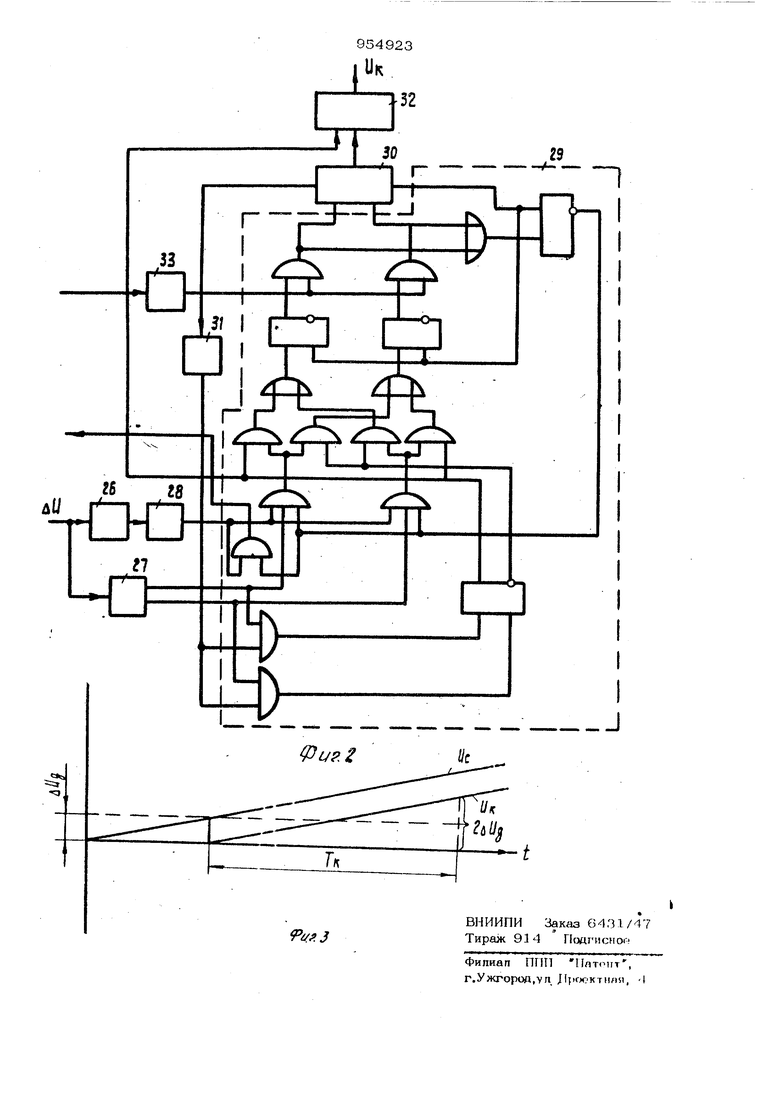

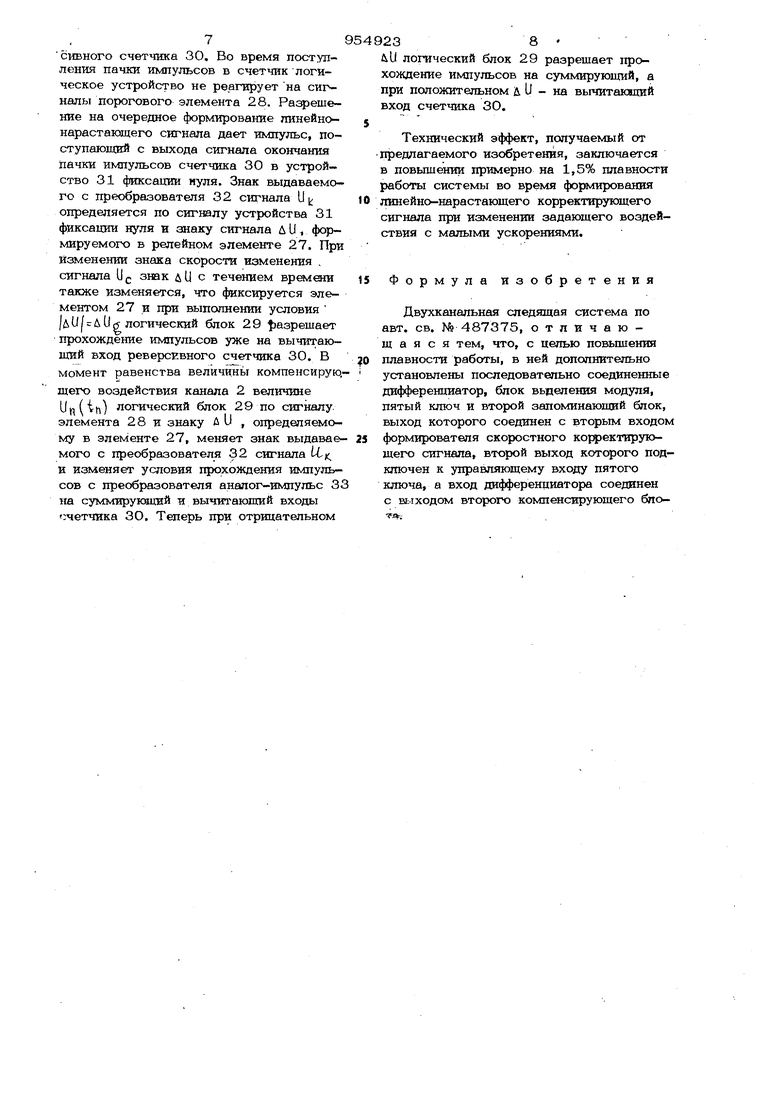

Недостатком известной системы является значительная неппавность ее работы во время формирования линейно-на9растающего сигнала кодзекции при тюмененки задающего воздействия с малыми ускорешюми, поскольку независимо от ускорения задающего воздействтш линейно-нарастающий сигнал коррекции формируется с постоянным наклоном, соответствующим максимальному ускорению задающего воздействия. Цель изобретения - повышение плавности работы системы. Поставленная цель достигается тем, что в системе дополнительно установлены последовательно соедине1шые диффе-; ренциатор, блок выделения модуля, пятый ключ и второй запоминающий блок, выход которого соединен с вторым входом формирователя скоростного корректирующего сигнала, второй выход которо подключен к управляющему входу пятого ключа, а вход дифференциатора .соединен с выходом второго компенсирующего бло ка. На фиг. 1 представлена блок-сжма системы; на фиг. 2 - блок-схема формирователя скоростного корректирующего сигнала; на фиг. 3 - эшорзы основных направлений, иллюстрирующие работу системы. Система содержит канал .1 программного управления, канал 2 сопровождения, измеритель 3 рассогласования, второй ключ 4, первый сумматор 5, пороговьй элемент 6, первый ключ 7, первы компенсирующий блок 8, первый запомин щий блок 9, силовой блок 10, датчик 11 обратной связи, датчик 12 рассогласовакия,- второй сумматор 13, корректирующий блок 14, второй компенсирующий блок 15, третий сумматор 16, четверты ключ 17, формирователь 18 скоростного корректирующего сигнала, четвертый сутл матор 19, третий ключ 20, объект 21, дифференциатор 22, блок 23 выделения модуля, пятый ключ 24, второй запоминающий блок 25, вьшрямитель 26, релейный элемент 27, пороговый элеме}П 28, логический блок 29, реверсивный счетчик 30, устройство 31 фиксации нуля, преобразователь 32 цифра - напряже ние, преобразователь 33 аналог - импульс. Введены обозначения: oiQ - регулируемая координата, о tv. программное задающее воздействие; с воздействие канала сопровождения; 11 сигнал, пррпо4 Ш1ональный скорости изм нения t с ; t- - корректирующий сигнал по скорости канала сопровождения pi ; 34 iUg - допустимая величина модуля ДУ ; гпах макслгмат ное ycKOpeirae воздейтвия с ; SZ , - мшшмальное ускорение воздействия обе соответствующее и тмальной скорости изменения сигнала U() Система работает следующим образом. В режиме отработки программного задающего воздействия ключи 4 и 7 замкнуты, а ключи 17 и 20 разомкнуты, и программное воздействие o6j отрабатывается каналом 1. Для компенсации составляющей ошибки, пропорциональной прогнозируемой скорости объекта 21, на вход сумматора 5 поступает компенсирующий сигнал УП с выхода компенсирующего блока 8. При достижении каналом 1 заданной точности наведения, характеризуемой величиной ощибки сопровождения (обе -обо), срабатывает пороговый элемент 6, выходной сигнал которого размыкает ключи 4 и 7 и замыкает ключи 17 и 20; на вход сумматора 5 поступает сигнал, пропорциональный ошибке (обе-о о)и запомненный на все время сопровожде шя в блоке 9 сигнал u(tr), пропорциональный прогнозируемой скорости в момент переключения режимов. Сигнал U с формируется по методу дифференциальной вилки путем суммирования сигналов, пропорциональных oi и (оСс -df)}, поступающих на сумматор 13 с выходов датчика 11 (через корректирующий блок 14) и датчика 12 соответстве шо, и последующего дифференци- ровазшя в блоке 15. На выходе сумматора 16 формируется сигнал iU , поступающий через открытый ключ 17 на вход формирователя 18. Еспи при этом модуль Д U превысит допустимую величину uUrf- , формирователь 18 формирует линейно-нарастающий сигнал с . амплитудой 2л Ug , скорость изменения которого пропорциональна ускорению воздействия (фиг. 3), имевшему место в момент превышения д величиныuUл;. Знак формируемоТо сигнала совпадает со знаком Д и , причем в каждом цикле ксст ек1ШИ линейно-нарастающий сигнал Uj, алгебраически суммируется с величнной корректирующего сигнала U , имевшего место после предшествующего цикла коррекции. Алгебраическая сумма U (t) и УП (tfl) , формируемая в сумматоре 5, представляет собой компенсирующее воздействие для канала 2. Величина Д выбирается ра вной ошибке фop шpoвa}raя компенсирующего сигнала, соответствующей допустимой ошибке канала 2. При / Л и / А и g выходной сигнал формировател 18 остается постоянным. Возможен случай, когда при переключении системы на режим сопровождения вьшолняется неравенство |ди| Д Utf, а воздействие (i) изменяется с постоянной скоростью, т.е. сигнал на выходе дифференциатора 22 ре вен нулю. Поэтому на выходе запоминаю щего блока 25 предусматривается наличие остаточной величины Ос , необходимой для формирования корректирующего сигнала со скоростью О обеспечивающей уменьшение величины лУ даже при нулевом сигнале с выхода дифференциатора .блока 22. Величина ии(|,;,(та поэтому практически во всем диапазоне изменения ускорений воздействия ей с (t) имеет место соотнесение U(;(t) U|(i), УсловиеТ 1п5р исключает влияние положительной обратной связи, появляи щейся при нарушении условия эквивалент ности плечей вилки иэ-за наличия люфтов, упругих деформаций и гнутий в цепи блоков 10, 12 и 25. ..При вьшолнении условия Tjd :То где ,14: детерминированная . ставляющая сигнала | д U ( не превышает Л и х- в течение цикла коррекции Т,, если где максимальная величина третьей производной воздействия C,o(.t) . В самом деле, если допустить, что в худшем случае сразу после вьшолнения условия/Л и| Д Ug ускорение 6i,((i} начинает изменяться с максимальной скоростью , то-для того, чтобы в тече-iTiaxние времени 1 д выполнялось услоk max вие/ди/ Д Urf достаточно, чтобы Яшзг i : L- 2д5г г- ., min Tii max Дтаккак-Т;гпс«х -51 Н. : имеем (. Поскольку Д S2rf мало и для реальных воздействий oicT) max также мало, то 5Jniin ma к и ) % и i; (.t) . Цепочка вновь вводимых элементов служит для формирования наклона линейно-нарастающего корректнрук щего сигнала. Сигнал, пропорциональный модулю усжорения воздействия 06 , фо1 мируется с помоплью дифференциатора 22 и выпрямителя блока 23 выделения модуля и поступает через открытый ключ 24 в запоминающий блок 25. В MOMestrr 9 23.« превышения Л U величш1ы Д U л- с выхода формирователя скоростного корректир тощего сигнала 18 на вход ключа 24 поступает сигнал, запирающий его. Тогда , наклон будет определяться величиной сигнала, пропорционального ускорению Oti f., запомненного запоминающим блоком 25 в момент размыкания ключа 24. Запоминйние сигнала с выхода блока 23 на время ффмирования корректирующего сигнала U | исключает появление автоколебаний в системе иэ-за положительной обратной связи по ускорению выходной координаты системы. При изменении линейно-нарастающего сигнала U t; с переменной скоростью изменение скорости выходной координаты системы (oio) носит более плавный характер в разность (с ) с учетом корректирующего действия замкнутого через датчик 12 канала 2 сопровождения будет иметь значительно меньшую ввпвчвну при малых ускорениях , чем при формировании сигнала U с постоянной максимальной скоростью. Формирователь скоростного корректирующего сигнала 18 (фиг. 2) работает следующим образом. В момент равенства сигналов Uj и Ц j реверсивный счетчик 30 находится в нулевом состоянии, что фиксируется устройством 31 фиксации нуля. Сигнал Д U поступает на выпрямитель v 26 и релейный элемент 27. При накоплении отклонения Ли.до величины Д, равной порогу срабатывания порогового элемента -28, логический блок 29 подает размыкающий сигнал на ключ 24 и разрешает прохождение определенного количества импульсов с преобразователя аналог-импульс 33 на суммирующий вход реверсивного счетчика ЗО. Линейно нарастающий код реверсивного счетчика 30 подается на преобразователь 32 цифра-напряжение, с выхода которого сигнал U | поступает в сумматор 19- и третий вход сумматора 16. Количество и частота импульсов, поступающих с преобразователя аналогимпульс 33 в счетчик 30 за время цикла коррекции I ц , определяется соответственно, величиной uUg и величиной ускорения воздействия об , запомненного блоком 25 в момент превьппения Д веичины AJg. Если после данного цикла коррекции сигнал д U вновь достигает веичины uUg, то процесс коррекции программного компенсирующего сигнала повторяется, т.е. новая пачка импульсов поступает на суммирующий вход реверСИБНОГО счетчика 30. Во время поступления пачки импульсов в счетчик логическое устройство не реагирует на сигналы порогового элемента 28. Разрешение на очередное формирование линейнонарастающего сигнала дает импульс, поступающий с выхода сигнала окончания пачки импульсов счетчика 30 в устройство 31 фиксации нуля. Знак выдаваемого с преобразователя 32 сигнала U i/ определяется по сигналу устройства 31 фиксации нуля н знаку сигнала Д U, формируемого в релейном элементе 27. При изменении знака скорости изменения , сигнала Uc знак дЦ с течением времени также изменяется, что фиксируется элементом 27 и при выполнении условия |ди| Л Оологический блок 29 разрешает прохождение импульсов уже на вычитающий вход реверсивного счетчика 30. В момент равенства величины компенсирую щего воздействия канала 2 величине U(tt,) логический блок 29 по сигналу, элемента 28 к знаку Л U , определяемому в элементе 27, меняет знак выдавае мого с преобразователя 32 сигнала IL и изменяет условия прохождения импульсов с преобразователя аналог-импульс 3 1Ш суммирующий и вычитающий входы счетчика ЗО. Теперь 1фи отрицательном

ЛК логический блок 29 разрешает прохождение импульсов на суммирующий, а при положительном Д U - на вьпштаклций вход счетчика ЗО.

Технический эффект, получаемый от предлагаемого изобретения, заключается в повышении примерно на 1,5% плавности работы системы во время формирования линейно-нарастающего корректирующего сигнала при изменении задающего воздействия с малыми ускорениями.

Формула изобретения

Двухканальная следящая система по авт. св. № 487375, отличающаяся тем, что, с целью повьпиения плавности работы, в ней дополнительно установлены последовательно соединенные дифференциатор, блок вьделения модуля, пятый ключ и второй запоминающий блок, выход которого соединен с вторым входом формирователя скоростного корректирующего сигнала, второй выход которого подкгаочен к управл5пощему входу пятого ключа, а вход дифференциатора соединен с вь.ходом второго компенсирующего бпоГ , Г,1

i.f

I

Авторы

Даты

1982-08-30—Публикация

1980-04-03—Подача