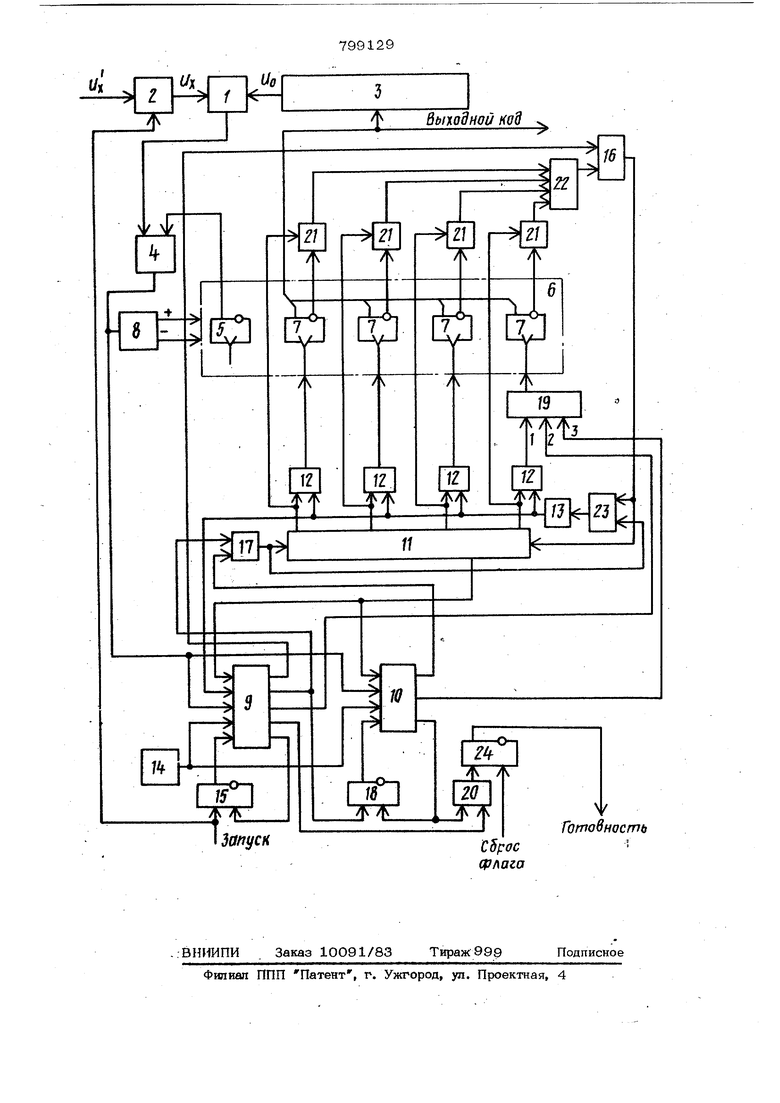

ля импульсов, а выходы соединены с6 сч ными входами соответствующих .разря/цов реверсивного счетчика; введены два допопнитепьных логических блока, два триггера, триггер флага, дополнительная группа элементов И, пять элементов ИЛИ, элемент И и блок поиска г.огшиапазона, выход бпока сравнения соединен с первым вхЬдшг первого дополнительного логического бпока, второй Вход которого соединен с выходом дополнительного старшего разряда реверсивного счетчика выход первого дополнительного логического бпока соединен со входом логического блока, с пе{Еым входом блока поиска поддиапазона и со вторым входом второго допопнительного логического блока, второй вход бпока поиска поддиапазона соединен со вторым входом второго допопнительного логического блока и с единичным выходом младшего разряда распределителя импульсов, третий вход блока поиска-поддиапазона соединен со вто{я 1ми входами И первой группы и с выходом линии задержки,четвертый вход бпока поиска поддиапазона соединен с третьим входом второго допопнительного логического бпока и с выхоаом генератора тактовых импупьссж, а пятый вход соединен с единичным выходом первого триггера, первый выход бпока поиска поцдиапазсжа соединен с первы входом элемента И, второй выход соединен с первым входом первого эпемента ИЛИ и с единичным входом второго триггера, третий выход соединен с первым входом второго элемента ИЛИ, четвертый выход соединен с первым входом третьего элемента ИЛИ, пятый выход соединен с нулевым входом первого триггера чётвертый вход второго дополнительного логического блока соединен с единичным вы ходом второго триггера, а первый выход соейинен со вторым входом первого эле мента ИЛИ, второй выход соединен со вторым входсии второго элемента ИЛИ, а третий выход соединен с нулевым входом второго триггера и со вторым вход .третьего эпемента ИЛИ; выходы триггеров веех разрядов реверсивного . счетчика, кроме дополнительного старшего разряда, соединены с первыми входами элементов И дополнительной группы, вторые лкоды которых соединены с выходами соответствующих разрядов распреде лителя импульсов, выходы элементов И дополнительной группы соединены с соот ветствующими входами четвертого элемен та ИЛИ, выход которого соединен со вто рым входом элемента И, выход которого соединен с первым входом пятого эпементта ИЛИ и со входом сдвига влево распределителя импульсов, второй вход пятого элемента ИЛИ соединен со входом сдвига вправо распределителя импульсов и с выходом первого элемента ИЛИ, выход пятого элемента ИЛИ соединен со входом линии задержки, выход младшего элемента И первой группы соединен с третьим входом второго эпемента ИЛИ, выход которого соединен со счётным входом триггера мпадшего разряда реверсивного счетчика; выход третьего элемента ИЛИ соединен с единичным входом триггера флага, нуле- вой вход которого соединен с шиной Сброс флага , а единичный выход соединен с шиной Готовность, единичный вход первого триггера соединен с управляющим; входом анапогового запоминающего устройсттва и с шиной Запуск. Структурная электрическая устройств а «приведена на чертеже. След51щий аналого-цифровой преобразователь содержит блок 1 сравнения, вход котхэрой соединен с выходом аналогового запоминающего устройства 2, на вход которого поступает сходной сигнал, второй вход блока 1 соединен с выходом цифроанапогового преобразователя 3, выход бпока 2 соединен с первым входом логического блока 4, второй вход которого соединен с единичным выходом триггера 5 дополнительного старшего разряда реверсивного счетчика 6, состоящего из триггерюв 5 и 7, выходы триггеров 7 всех разрядов ршерсивного счетчика 6, кроме дополнительного старшего разряда триггера 5, соединены с цифровыми входами нифроанапогеюого преобразователя 3, выход логического блока 4 соединен со входом логического блока 8, выходы которого соединены со входами установки режима реверсивного счетчика 6 и с третьюл входом бпока 9 поиска поддиапазона и вторым входом логического блока 1О, первый вход блока 9 соединен с первым входом логического блока 10 и с единичным выходом младшего разряда распределителя 11 импульсов, второй вход блока 9 - с первыми входами элементов И 12 первой группь и с выходом линии 13 задержки четвертый - с третьим входом логического блока 10 и с выходом генератора 14 тактовых импульсов, пятый с единичным выходом триггера 15; первый выход блока 9 соединен с первым входом эпемента И 16, второй выход блока 9 - с первым входом эпемента ИЛИ

17 и с единичным входом триггера 18, третий выход блока 9 - со вторым входом элемента ИЛИ 19, четвертый выход блока 9 - с первым входом эпеманта ИЛИ 20, пятый выход блока 9 - с нулевым входом триггера 15; четвертый вход логического блока 10 соединен с единичным выходом триггера 18, первьШ выход логического блока 10 -со вторым входом элемента ИЛИ 1 7,второй выход логичес- . кого блока 10 - с третьим входом эпемента ИЛИ 19, а третий выход логического блока 10 - с нулевым входсал трит гера 18 и со вторым входом элеметтта ИЛИ 2О, нулевые выходы триггеров 7 всех разр5 дов реверсивного счетчика 6, кроме дополнительного 5 старшего разряда, соединены с первыми входами элемента И 21 второй группы, вторые входы которых соединены с выходами соодаетствующих разрядов распределителя 11 импульсов и со вторыми входами соответствующих элементов И 12 первой группы, выходы элементов И 21 второй группы соединены с соответствующими входами элемента ИЛИ 22, выход которого соединен со вторым входсш элемента И 16, выход которого соединен с первым вхои- дом энемента ИЛИ 23, триггер 24 флага

Устройство работает следующим обрааам.

Перёд началом работы сигнал начапьной установки устанавливает триггеры 15 18 и 24 в нулевое состояние, распределитель 11 импульсов в состояние О...01, а реверсивный счетчик 6 может быть устансжлен в любое состояние с обнуленным старшим разрядом триггера 5.

С приходом сигнала Запуск триггер 15 устанавливается в I, а аналоговое запоминающее устройство 2 запоминает текущее значение сигнала. Триггер 15 разрешает работу блока 9 нахождения сигнала, который вначале проверяет, не нахо« дится ли сигнал в верхнем или нижнем кванте, примыкающем к образцовому уровню, зафиксированному на преобразователе, для этого блок 9 выдает сигнал (после поступления сигнала от генератора 14 тактЭвых импупьссв) на третьем выходу который, пройдя через элемент ИЛИ 1б, прибавит или вычтет единицу из реве| явного счетчика 6 в зависимости от ответа блока 2, устанавливающего с помощью логического блока 8 режим работы реверсивного счетчика 6 (так как :вначале и при дальнейшей нормальной работе триггер 5 дополнительного старшего разряда реверсивного счетчика 6 находится в О

состоянии, то логический бпок 4 пропус- , кает на свой выход ответ блока.2 без инвертирования). Если ответ блока 2 после этого (с приходом второго сигна.ла от

генератора 14) меняется на противоположный, то это означает, что сигнал найден, и при этом с минимальной погрешностью, (один квант), и поэтому преобразование заканчивается (тек самьп значительно

сокращается время преобразования). Для этого блок 9 выдает на четвертом и пятом выходах, которые соответственно устанавливают триггер 24 в , а триггер 15 в О состояние. При этом, (так как обычно преобразователи указывают на нижнюю границ кванта содержащего сигнал), если образцовый урсжень превышает входной сигнал ( N/Q 7/ X ) т. е, блок выдает сигнал S, то логичес кий блок 8 устанавливает режим вычитания на реверсивном счетчике 6, а блок 9 выдает сигнал, который произведет вычитание единицы из младшего разряда р ерсивного счетчика 6, Если же ответ блока 9 после этого (с приходом второго сигнала от генератора 14 тактовых имг ьсов) не меняется то, следовательно, значение входного сигнала не находится в данном кванте и блок 9 продолжает поиск поддиапазона, для этого он; до смены от вета блока 1 будет выдавать сигнал на первом выходе, который, при условии нахождения в нулевом состоянии разряда реверсивдюго счетчика 6, на который указывает распределитель 11 импульсов, пройдет через элемент И 16 и произведет сдвиг влево содержимого распределителя 11 импульсов, тем самым удвоит шаг квантования и, пройдя через линию 13 задержки, добавит или вычтет (в зависимости от ответа блока 1) единицу из разряда реверсивного счетчика 6, на который указьшает распределитель 11. Как только ответ блока 1 изменится на противополонсный (что сигнализирует о тсял, что поддиапазон нахождения сигнала найден ), так блок 9 выдаст сигнал, который устанавливает в 1 триггер 18 и начинает поразрядное преобразование проходя через элемент ИЛИ 17, сдвигая вправо на один разряд содержимое распределителя Ц (уменьшая в два раза шаг квантования). Пройдя через линию 13 задержки этот сигнал добавляет или вычитает единицу из разряда реверсивного счетчика 6, на который указьшает распределитель 11. При этом бпок 9 также выдает сигнал, который устанавливает в Отриггер .15, тем самым прекращается работа блока 9. Дальнейшим поразрядным преобразованием сиг нала внутри найденного поддиапазона управляет логический блок 10, который до появления единицы в последнем (младшем). ..разряде распределителя 11 будет выдават сигнал на своем первом выходе, который проходя через элемент ИЛИ 1 7 будет производить сдвиг вправо содержимого распределителя 11с последующим добавлением или вычитанием единицы из соот ветствующего разряда реверсивного счетчика 6. С появлением единицы в последнем разряде распределителя 11 логичес кий блок 10 выдает сигнал, который заканчивает преобразование; устанавливая в О триггер 18 ив 1 триггер- 24, при этом если VQ V , то появляется стенал на втором выходе логического бл ка 10, который вычтет единицу из младшего разряда реверсивного счетчика 6, тем самым во всех случаях будет указана нижняя граница кванта, содержащего сигнал. Если же из-за близости сигнала к вер ней границе диапазона возможных значений сигнала при поиске поддиапазона происходит переполнение реверсивного счетчика 6, т. е. устанавливается код 10.,. О {кодов 10... О быть не может из-за используемого правила формирсжа- ния кодов}, то из-за единичного положени триггера 5 дополнительного старшего раз ряда реверсивного счетчика 6 логический блок 4 передает на свой выход проинвертированный сигнал блока 1, в результате чего прекращается поиск поддиапазона и начинается поразрядное преобразование сигнала внутри найденного поддиапазона. Формула изобретения Следящий аналого-цифровой,преобразователь, содержащий генератор тактовых . импульсов, линию задержки, блок сравнения, первый вход которого соединен с выходом аналогового запоминающего устройс ва, вход которого соединен с источнлком входного сигнала второй вход соединен с выходом цифроаналогового преобразователя, цифровые входы которого соединены с выходам(р разрядов ршерсивного счетчика, выходы логического блока соединены со входами режима реверси ного счетчика, -первые входы элементов И группы соединены с выходами соответствующих разряде распределителя импульсов, а выходы соединены со счетными входами соответствующих разрядов р ерсивного счетчика, отличаю -

щийся тем, что, с целью повышения быстродействия и достоверности преобразовавиЯувведены два дополнительных логических блока, два триггера, триггер.флага. Дополнительная группа элементов И, пять элементов ИЛИ, элемент И и блок поиска поддиапазона, причем выход блока сравнения соединен с первым входом первого дополнительного логического блока, второй вход которого соединен с выходом дополнительного старшего разряда реверсивного счетчика выход дополнительного логического блока сЬединен со входом логического блока, с первым входам блока поиска поддиапазона и со вторым входом второго дополнительного логического блока, второй вход блока поиска поддиапазона соединен, со вторым входом второго дополнительного логическогоблока и с единичным выходом младшего разряда распределителя импульсов, третий вход блока поиска поддиапазона соединен со вторыми входами элементов И пе{жой группы и с выходом задержки; четвертый вход блока поиска поддиапазона соединен с третьим входом второго дополнительного логического блока и с выходом генератора тактевых импульсов, а пятый вход соединен с единичным в,1ходом первого триггера первый выход блока поиска поддиапазона соединен с первым входом элемента И, второй выход соединен с первым входом пегого элемента ИЛИ и с единичным входом второго триггера, третий выход соединен с первым входом второго элемента ИЛИ, четвертый выход соединен с первым входом третьего элемента ИЛИ, а пятый выход соединен с нулевым входом первого триггера; четвертый вход второго дополнительного логического блока соединен с единичньтм выходом второго триггера; первый выход сое- ДИВО со вторым входом первого элемента ИЛИ, второй выход соединен со вторым входом втюрого элемента ИЛИ, а третий выход соединен с нулевым входом второго триггера и со вторым входом третьего элемента ИЛИ, нулевые выходы триггёров всех разряде реверсивного счетчика, кроме дополнительного старшего разряда, соединены с первыми входами элементов И дополнительной группы, вторые входы которых соединены с выходами соответствуюших разряде ра:пределителя импульсов, выходы элементов И дополнительной группы соединены с сое)тветствующими входаМИ четвертого элемента ИЛИ, выход которого соединен со вторым входом элемента И, выход которого соединен с первым входом пятого элемента ИЛИ и со входом сдвига влево распределителя импульсов, .

второй вход пятого элемента ИЛИ соединен со входом сдвига вправо распределителя импульсов и с выходом первого элемента ИЛИ, выход пятого элемента ИЛИ соединен со входом пинии задержки, вы- 5 ход младшего элемента И первой -группы соединен с третьим входом второго элемента ИЛИ, выход которого соединен с сч&т ным входом триггера младшего разряда реверсивного счетчика, выход третьего ю элемента ИЛИ соединен с единичным вхо- дом триггера фпага, нулевой вход которого соединен с шиной Сброс флага , а единичный выход соедив-ен с шиной Готовность, единичный вход пе{дарго триггера cdteOTHeH с управляющим входом аналогеюого запоминаюшего устройства -и с шиной Запуск.

Источники информации, принятые во внимание при экспертизе

1.Смолсж В. Б., Смирнов Е. А. и др, Полупрсводниковые кодирующие и декодирующие преобразсжатё™ напряжения. Л.,. Энергия, 1967, с. 135.

2.Авторское свидетельство СССР № 324639, кп. Н 03 К 13/02, 1968 (прототип). I Jtf/7 CK

гп СЬрос флага Y Готовность

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU892702A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU900437A2 |

| Следящий аналого-цифровой преобразователь | 1988 |

|

SU1594691A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU744968A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| Следящий аналого-цифровой преобразователь | 1984 |

|

SU1179538A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU900438A2 |

| Следящий аналого-цифровой преобразователь | 1984 |

|

SU1184090A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU805489A1 |

| Генератор циклов | 1981 |

|

SU964616A1 |

Авторы

Даты

1981-01-23—Публикация

1979-03-26—Подача