Изобретение относится к радиотехнике и предназначено для деления входной частоты на 3,5.

Известно устройство, которое содержит триггеры на потенциальных элементах и элементы И-НЕ 1.

Однако, данное устройство осуществляет деление частоты только на целое число.

Известно также устройство, которое яв.тяется более совершенным и содержит три разряда, каждый из которых состоит из триггера иамяти, элемента И-НЕ и коммутационного триггера, нулевой выход которого соединен с единичным входом триггера памяти, единичный выход которого соединен с единичным входом коммутационного тритгера, при этом в третьем разряде содержится доиолннтельный коммутационный триггер, нулевой вход которого соединен с единичным выходом коммутационного триггера, а единичный выход-с нулевым входом коммутационного триггера и с .нулевым входом триггера памяти 2.

С целью упрощения устройства в предлагаемом делителе частоты в каждом ив двух первых разрядов единичный выход коммутационного триггера соединен с первым входом элемента И-НЕ, второй вход которого подключен к нулевому входу коммутационного триггера своего разряда и к единичному входу коммутационного триггера следующего разряда, а выход к единичному входу коммутационного триггера следующего разряда, иричем второй вход элемента И-НЕ второго разряда соединен также с нулевыми входами триггера памяти и коммутационного триггера первого разряда, при этом единичный выход донолнительного коммутацнонного триггера соединен с нулевыми входамн коммутациониого триггера и триггера памяти второго разряда, нулевой выход коммутационного триггера третьего разряда подключен ко второму входу элемента И-НЕ этого же разряда, а нулевые входы ко-ммутациоиных триггеров всех разрядов и единичный вход дополннтельного коммутационного триггера иодключены к щине тактирующего сигнала.

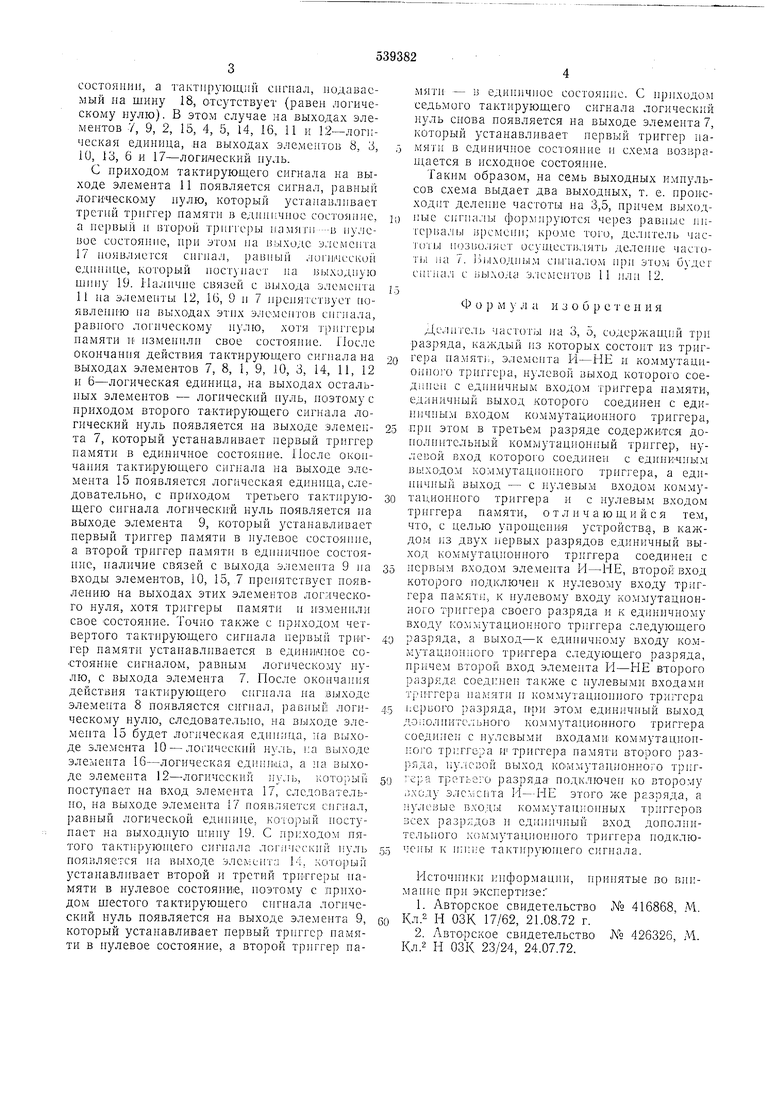

На чертеже показана структурная электрическая схема предлагаемого дел)1теля частоты на 3,5.

Устройство содерл Н1Т триггеры памяти на элемеитах 1-6, коммутационные триггеры на элементах 7-12, дополнительный коммутационный трнггер на элементах 13 н 14 и элементы И-НЕ 15-17, шину 18 тактирующего сигнала, ши-ну 19 выходного сигнала.

Устройство работает следующнм образом. В исходном состоянии иервый и второй триггеры иамяти иа,ходятся в единичном соСТОЯНИИ, третий триггер памяти-в иулевом

состоянии, а тактирующий сигнал, нодавасмый на шину 18, отсутствует (равен логическому нулю). В этом случае на выходах элементов 7, 9, 2, 15, 4, 5, 14, 16, И и 12-логическая единица, на выходах элеме1ггов 8, , 10, 13, 6 и 17-логический пуль.

С нриходом тактирующего сигнала на выходе элемента И иоявляется сигнал, равный логическо-му нулю, который устанавливает третий триггер памяти в ед11ц|;чпос состояние, а первый и второй триггеры памяти---в пулевое состояние, ири этом на выхо;1,е э.лсмеита 17 появляется сигнал, равный логн1чсской единице, который иостуиает на выходную шину 19. Наличие связей с выхода элемента И иа элементы 12, 16, 9 п 7 иреиятстнует tioявлепиЮ па выходах этих элемептов снгиала, равного логическому пулю, хотя трнпсрв памяти и- изменили свое состояние. После окончаппя действИ:Я тактирующего сигнала на выходах элементов 7, 8, I, 9, 10, 3, 14, 11, 12 и 6-логическая единица, на выходах остальных элементов - логический пуль, поэтому с приходом второго таа тп-рующего сигнала логический нуль появляется на выходе элемепта 7, который устанавливает первый триггер памяти в единнчиое состояние. После окончания тактИ|рующего сигнала на выходе элемента 15 появляется логическая единица,следовательно, с приходом третьего тактирующего сигнала логическ гй нуль иоявляется иа выходе элемента 9, который устанавливает иервый триггер памяти в нулевое состОЯине, а второй триггер иамяти в единичное состояиие, иаличие связей с выхода элемеита 9 на входы элементов, 10, 15, 7 иреиятствует иоявлению на выходах этих элементов логического нуля, хотя триггеры намяти п измеиили свое состояние. Точно также с приходом четвертого тактирующего сигнала пе)вый триггер памяти устанавливается в едининное состояние сигналом, равиым логическому иулю, с выхода элемеита 7. После окончания действия тактирующего сигнала иа выходе элемеита 8 появляется сигнал, равный лотческому нулю, следовательно, иа выходе элемента 15 будет логическая еднпица, на выходе элемента 10 - логический , ка выходе элемента 16-логическая еди11Н|Ца, а иа выходе элемента 12-логический , котор ый иоетуиает па вход элемента 17, следовательно, на выходе элемента 17 появляется сигнал, равный логичеекой единице, коюрый ностуиает на выходную шину 19. С пргходом иятого тактируюнтего сигиала логический нуль появляется иа выходе элемента М. .чоторы устанавливает второй и третий триггеры иамяти в нулевое состояние, иоэтому с приходом щестого тактируюндего сигнала логический нуль появляется иа выходе элемента 9, который устаиавливает первый триггер иамяти в нулевое состояние, а второй триггер иамяти - в едииичиое состояиие. С приходом седьмого тактирующего сигнала логический нуль спова иоявляется иа выходе элемеита 7, который устанавливает иервый триггер иамяти в едиипчное состояиие и схема возв|5аИ1,ается в исходное состояние.

Таким образом, па семь выходных импульсов схема выдает два выходных, т. е. происходит деление частоты на 3,5, причем выходные сигналы формируются через равные интервалы прсмени; кро.ме Toio, дел)ггель частоты 11()31 оляет ,сст)(.лять делеи1 е частоФ о р м у л а и J о б р е т е н и я

Дс;11Г1е,ль частоты иа 3, 5, содержащий три разряда, каждый из которых состоит из тригге 5а памяти, элемента И-ПЕ и ко.ммутациоиного триггера, нулевой выход которого соединен с единичным входом триггера намяти, единичный выход которого соедииеи с единичным входом коммутациоиного триггера, при этом в третьем разряде еодержится дополнительный коммутационный триггер, пулевой вход которого соедииеи с единичным выходом коммутацнонного триггера, а едиппчиый выход - с нулевым входом коммутациоиного триггера и с нулевым входом триггера памяти, отличающийея тем, что, с целью упрощеиия устройства, в каждом из двух первых разрядов единичный выход коммутационного триггера соедипеи с иервым входом элемеита И-НЕ, второй вход которого подключеи к нулевому входу триггера иамяти, к пулевому входу коммутацпонного триггера своего разряда и к единичному входу коммутационного тр)1ггера следующего разряда, а выход-к единичному входу коммутационного триггера следующего разряда, иричем второй вход элемеита П-НЕ второго |)азряда еоедипен также с нулевыми входами трИГгера памяти и ко.ммутациоиного триггера iicpuoro разряда, при этом единичный выход Д01:олиите.1ьного ко.vi мутационного триггера соедииеи с иулевыми входами коммутациоипого триггера № триггера памяти второго раз1)яда, нулевой выход к0ммутаи,ионного триггера третьего разряда подключеи ко второму эле:у С 1та И-НЕ этого же разряда, а ;1улевые входы коммутационных тритгеров всех разр;:дов н единичный вход донолнительпого коммутационного триггера подключены к ьщне тактируюптего сигнала.

Источники )-;11формапии, принятые во виимаиие при экспертизе:

1.Авторское свидетельство ° 416868, М. Кл.2 Н ОЗК 17/62, 21.08.72 г.

2.Авторекое свидетельство N° 426326, М. Кл.2 Н ОЗК 23/24, 24.07.72.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоично-десятичный счетчик | 1974 |

|

SU506131A1 |

| Быстродействующий счетчик | 1971 |

|

SU444330A1 |

| Делитель на 5 | 1976 |

|

SU558405A1 |

| Делитель частоты следования импульсов на 5,5 | 1978 |

|

SU746945A1 |

| Многопрограмный делитель частоты | 1976 |

|

SU641658A1 |

| Реверсивный счетчик | 1973 |

|

SU476687A1 |

| Разряд счетчика по модулю три | 1971 |

|

SU445989A1 |

| Делитель частоты на шесть | 1976 |

|

SU617846A1 |

| Делитель на 7 | 1976 |

|

SU576662A1 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

Авторы

Даты

1976-12-15—Публикация

1975-06-09—Подача