Изобретение очносится к вычислительной технике.

По основному авт. св. № 519709 известен сумматор, содержащий в каждом разряде счетный триггер, выполненный на элементах И-НЕ и дополнительные элементы И-НЕ, причем в счетпом триггере первые входы первого и второго элементов И-НЕ подключены к тактовой шипе, а выходы - к первым входам третьего и четвертого элементов И- НЕ соответствепно, второй вход третьего элемента И-НЕ соединен с выходом четвертого элемента И-НЕ, а второй вход четвертого- с выходом третьего п первым входом пятого элемепта И-НЕ, второй вход которого подключеп к выходу первого, а выход- к первому входу шестого элемепта Н-НЕ, второй вход шестого элемента И-НЕ подключен к выходу второго, а выход-к второму входу второго и входу седьмого элементов И-НЕ, выход седьмого элемента И-НЕ соединен с вторым входом первого элемента Н-НЕ, шина слагаемого и шина переноса пз младшего разряда подключепы к входам первого дополнптельного элемепта Н-НЕ, а шины пнверсии слагаемого и инверсии переноса из младшего разряда подключены к входам второго дополпнтельного элемента И-НЕ, а выходы дополнительных элементов И-НЕ подключены к третьим входам соответствен2

но второго и шестого и первого п пя1ого элементов Н-НЕ, выходы шестого п седьмого элементов И-НЕ являются выходами переноса и инверспп перепоса в старший разряд.

Известный сумматор не позволяет после сложения осуш,ествпть сдвиг информации.

Пелью изобретения является расширение функциональных возможностей устройства.

Это достигается тем, что в каждый разряд предлагаемого сумматора введены два элемента И-НЕ, первые входы которых объедннены и подключены к шине разрешения переноса, вторые входы подключены соответственно к шппам инверсии переноса и переноса из младшего разряда, а выходы соедппепы с четвертыми входами первого п второго элементов Н-НЕ, входяших в состав счетного триггера, а третьп входы дополпительных элементов Н-НЕ объединены и подключены к шине разрешения сложения.

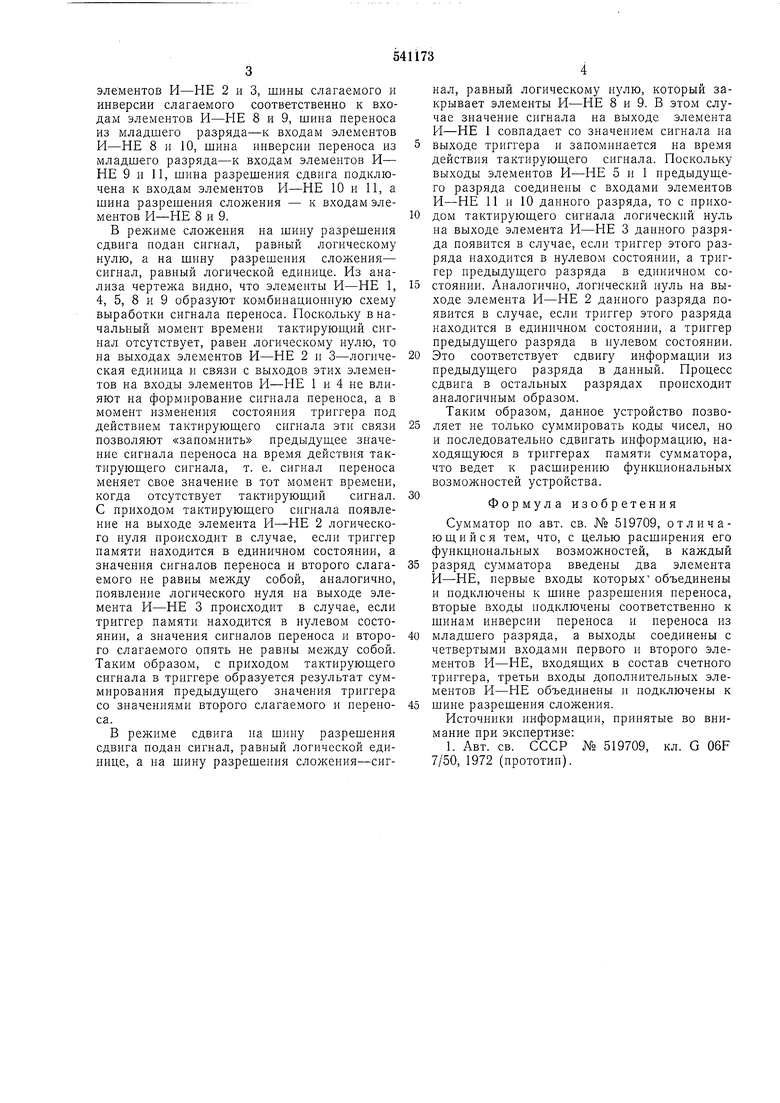

На чертеже изображена функциональная схема 1-го разряда сумматора.

Элементы И-НЕ 1-7 образуют счетный триггер; 8, 9-дополнительные элементы П- НЕ; 10, 11-вновь введенные элементы И- НЕ.

Выходы элементов И-НЕ 7, 1 и 5 являются выходами суммы перепоса н инверсии переноса в старший разряд пз данного разряда. Тактовая шнна подключена к входам

элементов И-НЕ 2 и 3, шины слагаемого и инверсии слагаемого соответственно к входам элементов И-НЕ 8 и 9, шина переноса из младшего разряда-к входам элементов И-НЕ 8 и 10, шина инверсии переноса из младшего разряда-к входам элементов И- НЕ 9 и И, шина разрешения сдвига подключена к входам элементов И-НЕ 10 н 11, а шина разрешения сложения - к входам элементов И-НЕ 8 и 9.

В режиме сложения на шину разрешения сдвига подан сигнал, равный логическому нулю, а на шину разрешения сложения- сигнал, равный логической единице. Из анализа чертежа видно, что элементы И-НЕ 1, 4, 5, 8 и 9 образуют комбинационную схему выработки сигнала переноса. Поскольку в начальный момент времени тактирующий сигиал отсутствует, равен логическому нулю, то на выходах элементов И-НЕ 2 н 3-логическая единица и связи с выходов этих элементов на входы элементов И-НЕ 1 и 4 не влияют на формирование сигнала переноса, а в момент изменения состояния триггера под действием тактирующего сигнала эти связи позволяют «запомнить предыдущее значение сигнала переноса на время действия тактирующего сигнала, т. е. сигнал переноса меняет свое значение в тот момент времени, когда отсутствует тактирующий сигнал. С приходом тактирующего сигнала появление на выходе элемента Н-НЕ 2 логического нуля происходит в случае, если триггер памяти находится в единичном состоянии, а значения сигналов переноса и второго слагаемого не равны между собой, аналогично, появление логического нуля на выходе элемента Н-НЕ 3 происходит в случае, если триггер памяти находится в нулевом состоянии, а значения сигиалов переноса и второго слагаемого опять не равны между собой. Таким образом, с приходом тактирующего сигнала в триггере образуется результат суммирования предыдущего значения триггера со значениями второго слагаемого и переиоса.

В режиме сдвига на шину разрешення сдвига подай сигнал, равный логической единице, а на шину разрешения сложения-сигнал, равный логическому нулю, который закрывает элементы Н-НЕ 8 и 9. В этом случае значение сигнала на выходе элемента И-НЕ 1 совпадает со значением сигнала на 5 выходе триггера и запоминается на время действия тактирующего сигнала. Поскольку выходы элементов Н-НЕ 5 и 1 предыдущего разряда соединены с входами элементов Н-НЕ 11 и 10 данного разряда, то с ирихо0 дом тактирующего сигнала логический нуль на выходе элемента Н-НЕ 3 данного разряда появится в случае, если триггер этого разряда находится в нулевом состоянии, а триггер предыдущего разряда в едииичиом состоянии. Диалогично, логический иуль на выходе элемента Н-НЕ 2 данного разряда появится в случае, если триггер этого разряда находится в единнчном состоянии, а триггер предыдущего разряда в нулевом состоянии.

0 Это соответствует сдвигу информации из

предыдущего разряда в данный. Процесс

сдвига в остальных разрядах происходит

аналогичным образом.

Таким образом, данное устройство позволяет не только суммировать коды чисел, но и последовательно сдвигать информацию, находящуюся в триггерах памяти сумматора, что ведет к расширению функциональных возможностей устройства.

0.

Формула изобретения

Сумматор по авт. св. № 519709, отличающийся тем, что, с целью расширения его функциональных возможностей, в каждый

5 разряд сумматора введены два элемента Н-НЕ, первые входы которых объединены и подключены к шине разрешения переноса, вторые входы подключены соответственно к шинам инверсии переноса и переноса нз

0 младшего разряда, а выходы соединены с четвертыми входами первого и второго элементов И-НЕ, входяших в состав счетного триггера, третьи входы дополнительных элементов И-НЕ объединены и подключены к

5 шине разрешения сложения.

Источники информации, принятые во внимание при экспертизе:

1. Авт. св. СССР № 519709, кл. G 06F 7/50, 1972 (прототип).

о

Слежение

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор | 1974 |

|

SU541172A2 |

| Сумматор | 1972 |

|

SU519709A1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| Функциональный преобразователь | 1987 |

|

SU1481750A1 |

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2264646C2 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2288501C1 |

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

Авторы

Даты

1976-12-30—Публикация

1974-10-11—Подача