1

Изобретение относится к системам передачи данных и телеуправления и может использоваться для синхронного запуска приемной аппаратуры.

Известно устройство для выделения рекуррентного синхросигнала, содержащее последовательно соединенные анализатор рекуррентной последовательности с блоком исправления ошибок и селектор со счетчиком числа ошибок. Однако такое устройство из-за наличия эффекта размножения и пропуска ошибок недостаточно помехоустойчиво.

Для повышения помехоустойчивости в предлагаемом устройстве к информационному входу анализатора рекуррентной последовательности подключен переключатель, к управляющим входам которого подключены выходы селектора, счетчика числа ошибок и анализатора реккурентной последовательности, причем один из выходов анализатора рекуррентной последовательности подключен к соответствущему входу селектора, а выход блока исправления ошибок - к входу счетчика числа ошибок.

Блок исправления ошибок выполнен на регистре сдвига с сумматором в цепи обратной связи, причем между выходом сумматора и входом регистра сдвига включен управляемый вентиль.

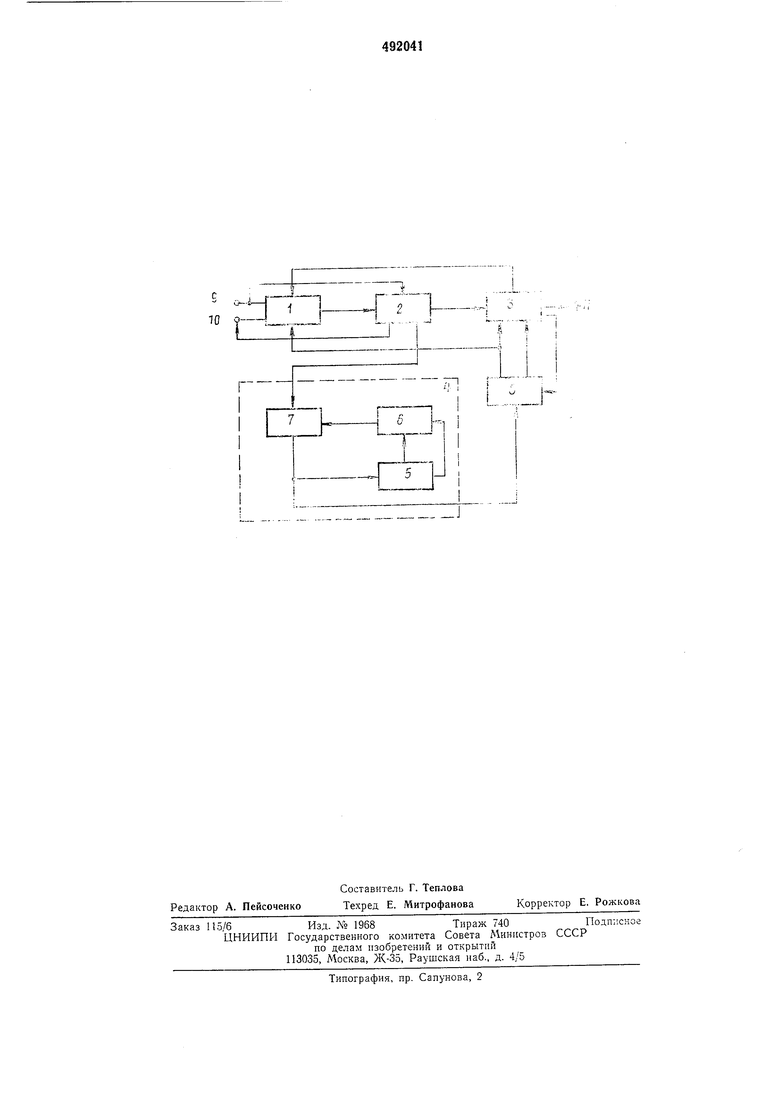

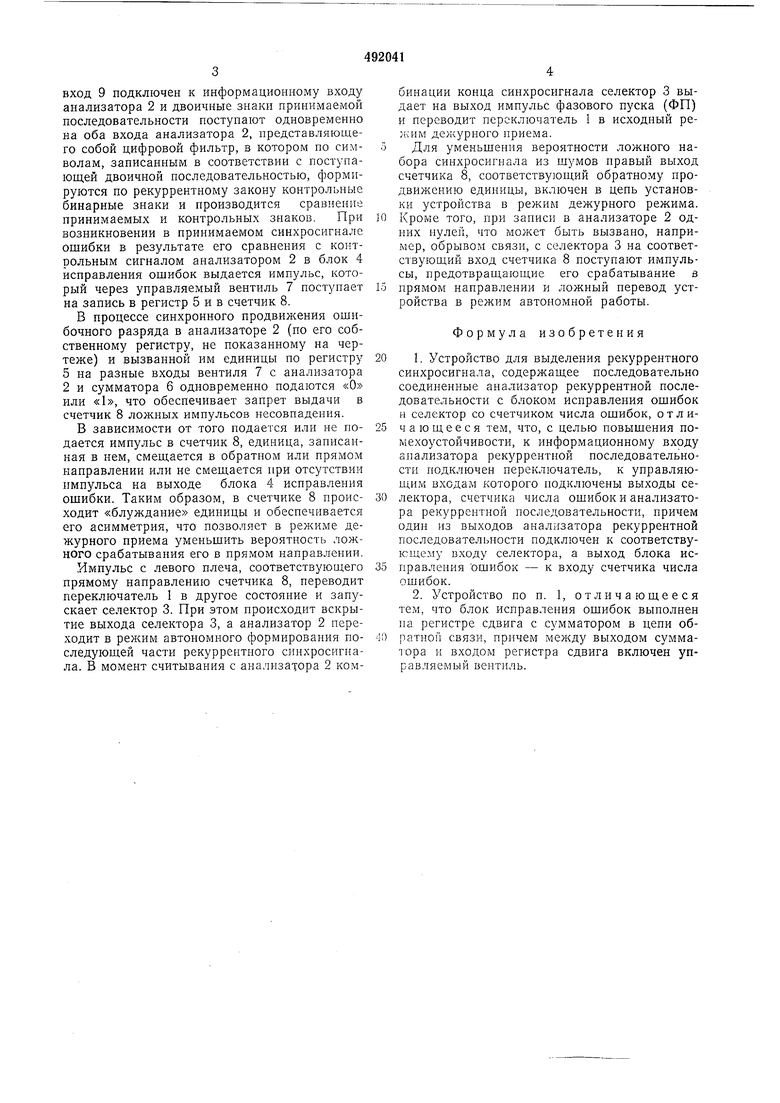

На чертеже лана структурная схема описываемого устройства.

Выход переключателя 1 устройства подключен к информационному входу анализатора 2 рекуррентной последовательности, один из выходов которого соединен с соответствующим входом селектора 3, а другой выход - с входом блока 4 исправления ошибок. Блок исправления ошибок выполнен на регистре 5 сдвига с сумматором 6 в цепи обратной связи, а между выходом сумматора и входом регистра сдвига включен управляемый вентиль 7. Выход блока 4 соединен с входом счетчика 8 числа ошибок. Переключатель 1 представляет собой блок коммутации одного из двух входов 9 и 10 на один общий выход с двумя управляющими входами, один из которых соединен с одним из выходов селектора 3, а другой - с одним из выходов счетчика 8, объединенным с соответствующим входом селектора. Вход 9 переключателя 1 соединен с другим входом анализатора 2, а вход 10 - с одним из его выхолТ.ов. Другой выход счетчика 8 соединен с третьим входом селектора 3, выход которого является выходом устройства, а дополнительный выход его соединен с соответствующим входом счетчика.

Устройство работает следующим образом.

В режиме дежурного приема переключатель 1 находится в таком положении, что его

вход 9 подключен к информационному входу анализатора 2 и двоичные знаки принимаемой последовательности поступают одновременно на оба входа анализатора 2, представляющего собой цифровой фильтр, в котором по символам, записанным в соответствии с поступающей двоичной последовательностью, формируются по рекуррентному закону контрольные бинарные знаки и производится сравнение принимаемых и контрольных знаков. При возникновении в принимаемом синхросигнале ошибки в результате его сравнения с контрольным сигналом анализатором 2 в блок 4 исправления ошибок выдается импульс, который через управляемый вентиль 7 поступает на запись в регистр бив счетчик 8.

В процессе синхронного продвижения ошибочного разряда в анализаторе 2 (по его собственному регистру, не показанному на чертеже) и вызванной им единицы по регистру 5 на разные входы вентиля 7 с анализатора 2 и сумматора 6 одновременно подаются «О или «1, что обеспечивает запрет выдачи в счетчик 8 ложных импульсов несовпадения.

В зависимости от того подается или не подается импульс в счетчик 8, единица, записанная в нем, смещается в обратном или прямом направлении или не смещается при отсутствии импульса на выходе блока 4 исправления ошибки. Таким образом, в счетчике 8 происходит «блуждание единицы и обеспечивается его асимметрия, что позволяет в режиме дежурного приема уменьшить вероятность ложного срабатывания его в прямом направлении.

Импульс с левого плеча, соответствующего прямому направлению счетчика 8, переводит переключатель 1 в другое состояние и запускает селектор 3. При этом происходит вскрытие выхода селектора 3, а анализатор 2 переходит в автономного формирования последующей части рекуррентного синхросрннала. В момент считывания с анализатора 2 комбинации конца синхросигнала селектор 3 выдает на выход импульс фазового пуска (ФП) и переводит переключатель I в исходный режим дежурного приема.

Для уменьшения вероятности ложного набора синхросигнала из шумов правый выход счетчика 8, соответствующий обратному продвижению единицы, включен в цепь установки устройства в режим дежурного режима.

Кроме того, при заниси в анализаторе 2 одних нулей, что может быть вызвано, например, обрывом связи, с селектора 3 на соответствующий вход счетчика 8 поступают импульсы, предотвращающие его срабатывание в

прямом направлении и ложный неревод устройства в режим автономной работы.

Формула изобретения

1. Устройство для выделения рекуррентного синхросигнала, содержащее последовательно соединенные анализатор рекуррентной последовательности с блоком исправления ошибок и селектор со счетчиком числа ошибок, о т л ичающееся тем, что, с целью повышения помехоустойчивости, к информационному входу анализатора рекуррентной последовательности подключен переключатель, к управляющим входам которого подключены выходы селектора, счетчика числа ошибок и анализатора рекуррентной последовательности, причем один из выходов анализатора рекуррентной последовательности подключен к соответствующему входу селектора, а выход блока исправления ошибок - к входу счетчика числа ошибок.

2. Устройство по п. 1, отличающееся тем, что блок исправления ошибок выполнен па регистре сдвига с сумматором в цени обратноп связи, причем между выходом сумматора и входом регистра сдвига включен управляемый вентиль.

--Fs c..

10 9..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения рекуррентного синхросигнала | 1978 |

|

SU758549A2 |

| Устройство выделения рекуррентного сигнала с обнаружением ошибок | 1986 |

|

SU1327308A2 |

| Устройство для выделения рекуррентоного синхросигнала с исправлением ошибок | 1976 |

|

SU618859A1 |

| Устройство для выделения рекуррентного синхросигнала | 1983 |

|

SU1116547A1 |

| Устройство выделения рекуррентного синхросигнала с исправлением ошибок | 1976 |

|

SU582578A1 |

| Устройство выделения рекурентного сигнала с обнаружением ошибок | 1978 |

|

SU758552A1 |

| Устройство для выделения рекуррентного синхросигнала с обнаружением ошибок | 1988 |

|

SU1518905A2 |

| УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ РЕКУРРЕНТНОГО СИНХРОСИГНАЛА С ИСПРАВЛЕНИЕМ ОШИБОК | 1970 |

|

SU262942A1 |

| Устройство выделения рекуррентного синхросигнала с обнаружением ошибок | 1976 |

|

SU604173A2 |

| Устройство для выделения рекуррентного синхросигнала с обнаружением ошибок | 1986 |

|

SU1363510A1 |

Авторы

Даты

1975-11-15—Публикация

1973-04-27—Подача