Предлагаемое устройство относится к системам для передачи данных и может быть использовано для выделения сигналов фазового пуска в системах, имеющих релсим дежурного приема информации.

Известны устройства для групповой синхронизации систем передачи данных, которые применяют (Передачу сосредоточенных рекуррентных посылок оинхронизации. Выделение фазирующих сигналов из таких посылок обычно производится в том случае, когда закон аистроения рекуррентного кода удовлетворяется определенным числом знаков посылок синхронизации, что увеличивает время .вхождения в синхронизм. Кроме того, такая система синхронизации подвержена влиянию помех в канале связи.

Предлагаемое устройство отличается от известных тем, что выделение фазирующих сигналовпроизводится после исправления ошибок в рекуррентных посылках синхронизации. Для этого выход узла анализа рекуррентной последовательности соединен с узлом исправления ошибок и одновременно с входом счетчика числа ошибок, а в качестве счетчика числа ошибок применен реверсивный счетчик.

Счетчик связан с одним из входов логической схемы «И, на второй вход которой подключен селектор, находящийся в одной цепи с накопителем исправленных знаков, который

входом соединен с узлом исправленных ошибок.

Исправление ошибок позволяет повысить вероятность травильного приема селектируемого

участка посылок синхронизации в каналах связи с помехами. В то же время применение реверсивного счетчика повышает быстродейст1вие устройства.

Предлагаемое устройство для выделения рекуррентного синхросигнала не требует введения разделительных знаков или других ограничений на передаваемую случайную последовательность знаков информации.

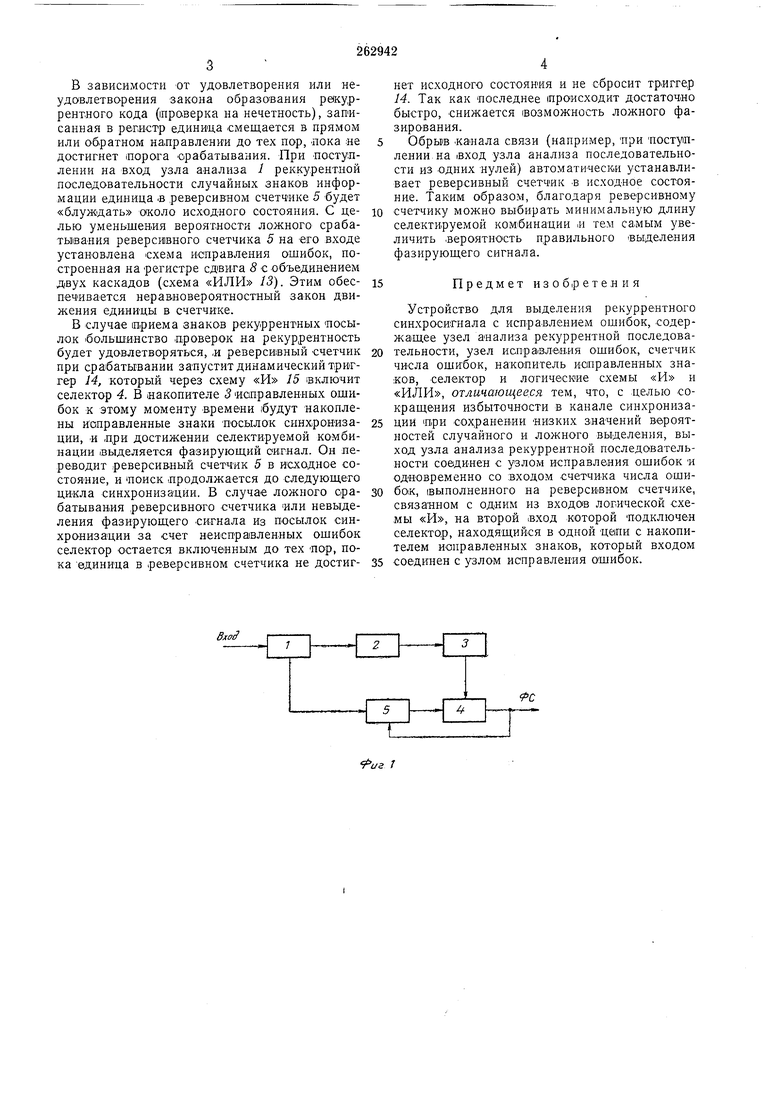

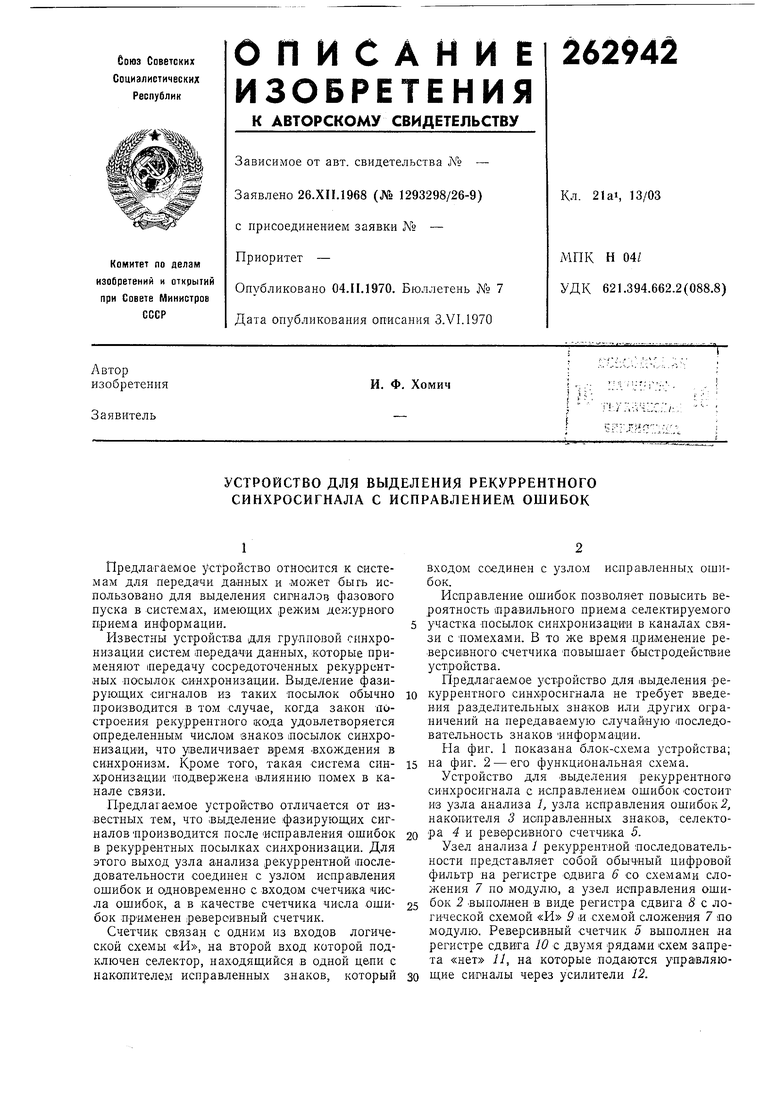

На фиг. 1 показана блок-схема устройства;

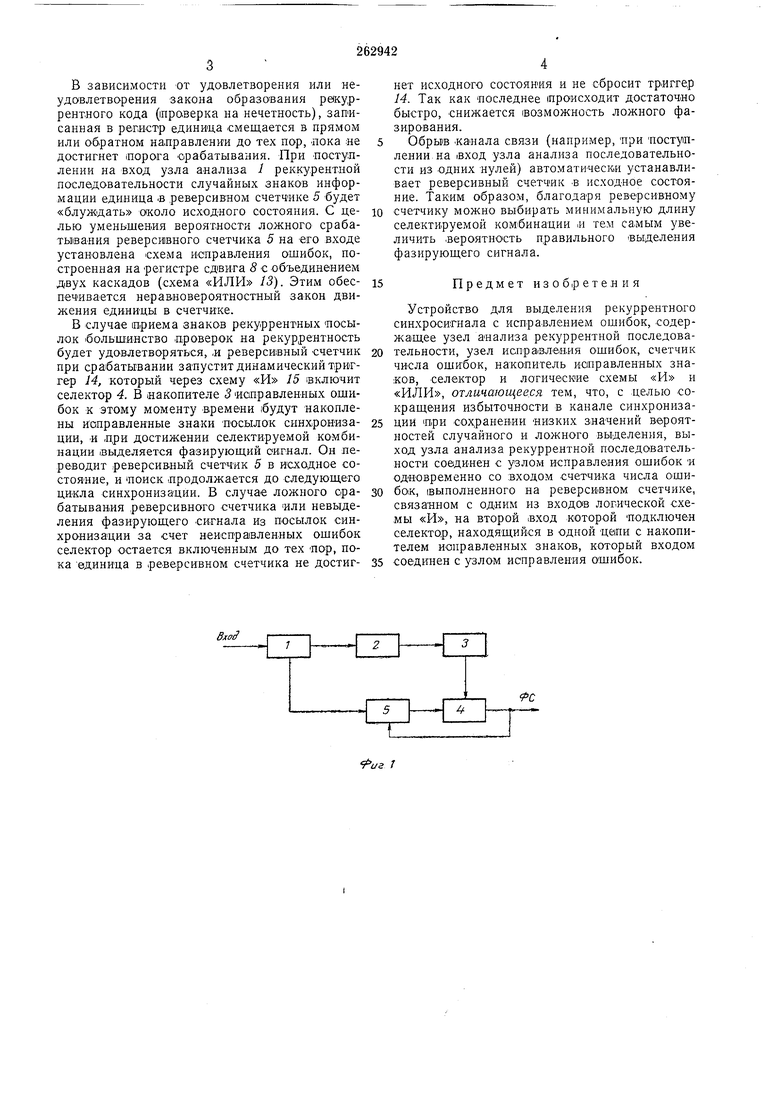

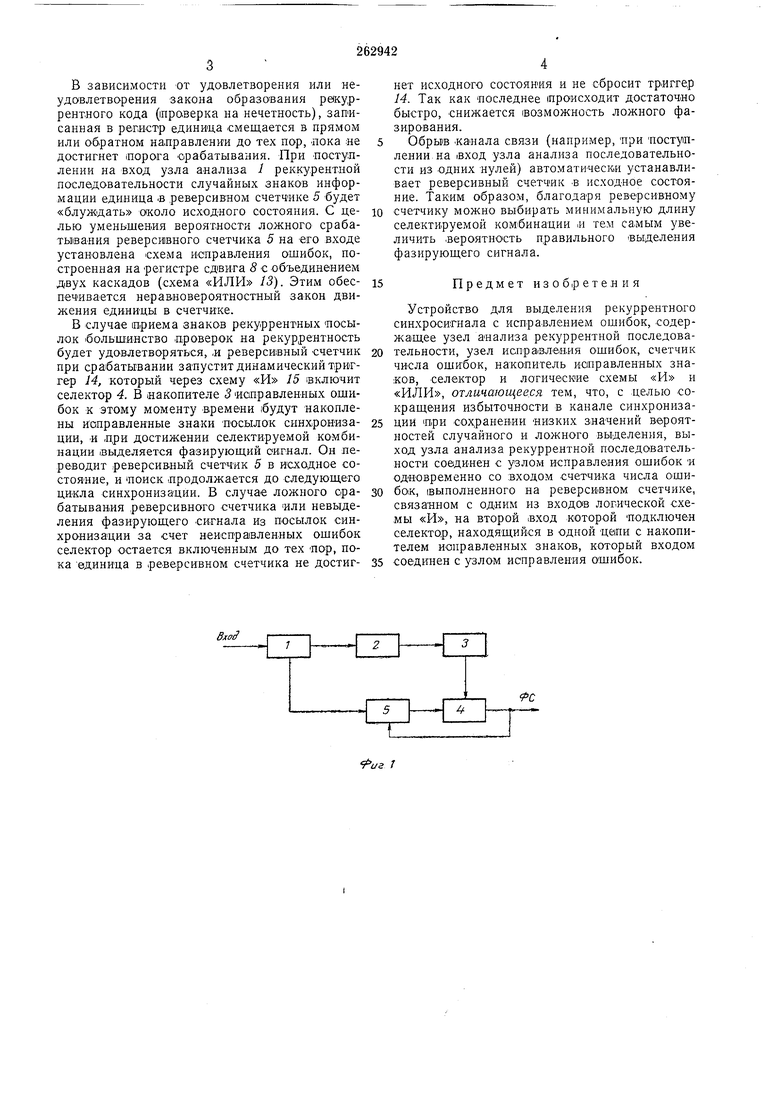

на фиг. 2 - его функциональная схема.

Устройство для выделения рекуррентного синхросигнала с исправлением ошибок состоит из узла анализа 1, узла исправления ошибок2, накопителя 3 исправленных знаков, селектора 4 и реверсивного счетчика 5.

Узел анализа / рекуррентной последовательности представляет собой обычный цифровой фильтр на регистре сдвига 6 со схемами сложения 7 по модулю, а узел исправления ошибок 2 выполнен в виде регистра сдвига 8 с логической схемой «И 9 и схемой сложения 7 по модулю. Реверсивный счетчик 5 выполнен на регистре сдвига 10 с двумя рядами схем запрета «нет 11, на которые подаются управляюВ зависимости от удовлетворения или неудовлетворения закона образования рекуррентного кода (|про,верка на нечетность), записанная в регистр единица смещается в прямом или обратном направлении до тех пор, лока яе достигнет гоорога орабатывания. При лостуллении на вход узла анализа / рекку.рентной последовательности случайных знаков информации единица .в .реверсивном счетчике 5 будет «блуждать около исходного состояния. С целью уменьшения вероятности ложного срабатывания реверси1вного счетчика 5 на его входе установлена схема исправления ошибок, построенная на регистре сдвига 8 с объединением двух каскадов (схема «ИЛИ /5). Этим обеспечивается нераановероятностный закон движения единицы в счетчике.

В случае приема знаков рекуррентных посылок большинство проверок на рекуррентность будет удовлетворяться, ,и реверсивный счетчик при срабатывании запустит динамический триггер 14, который через схему «И 15 включит селектор 4. В накопителе 5исправленных ошкбок к этому моменту времени (будут накоплены исправленные знаки посылок синхронизации, И ,при достижении селектируемой комбинации выделяется фазирующий сигнал. Он переводит реверсивный счетчик 5 в исходное состояние, и ПОИСК .продолжается до следующего цИКла синхронизации. В случае ложного срабатывания реверсивного счетчика или невыделения фазирующего сигнала из посылок синхронизации за счет неисправленных ошибок селектор остается включенным до тех лор, пока единица в реверсивном счетчика не достигнет исходного состояния и не сбросит тр.иггер 14. Так как последнее происходит достаточно быстро, снижается (возможность ложного фазирования.

Обрыв .канала связи (например, при поступлении, на вход узла анализа последовательности из одних нулей) автоматически устанавливает реверсивный счетчик в исходное состояние. Таким образом, благодаря реверсивному счетчику можно выбирать минимальную длину селектируемой ком бинации и тел самым увеличить вероятность правильного выделения фазирующего сигнала.

Предмет изобретения

Устройство для выделения рекуррентного синхросигнала с исправлением ошибок, содержащее узел анализа рекуррентной последовательности, узел исправления ошибок, счетчик числа ошибок, накопитель направленных знаков, селектор и логические схемы «И и «ИЛИ, отличающееся тем, что, с целью сокращения избыточности в канале синхронизации при сохранении низких значений вероятностей случайного и ложного выделения, выход узла анализа рекуррентной последовательности соединен с узлом исправления ошибок И одНОвременно со входом счетчика числа оши6oiK, (выполненного на реверсивном счетчике, связанном с одним из входов логической схемы «И, на второй вход которой подключен селектор, находящийся в одной цапи с накопителем исправленных знаков, который входом

соединен с узлом исправления ошибок.

f e/ eoo a

fioнoл связи

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выделения рекуррентного синхросигнала с обнаружением ошибок | 1983 |

|

SU1102050A2 |

| Устройство выделения рекурентного сигнала с обнаружением ошибок | 1978 |

|

SU758552A1 |

| Устройство выделения рекуррентного сигнала с обнаружением ошибок | 1986 |

|

SU1327308A2 |

| Устройство выделения рекуррентного синхросигнала с обнаружением ошибок | 1976 |

|

SU604173A2 |

| Устройство выделения рекуррентного синхросигнала с обнаружением ошибок | 1973 |

|

SU475744A1 |

| Устройство для выделения рекуррентного синхросигнала | 1973 |

|

SU492041A1 |

| Устройство для выделения рекуррентного синхросигнала с обнаружением ошибок | 1988 |

|

SU1518905A2 |

| Устройство для выделения рекуррентного синхросигнала | 1978 |

|

SU758549A2 |

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

| Приемное устройство цикловой синхронизации | 1976 |

|

SU578670A1 |

CSpoc-

Даты

1970-01-01—Публикация