(54) УСТРОЙСТВО ДЛЯ ВЫЧИТАНИЯ ДВОИЧНЫХ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИТАНИЯ ДВОИЧНЫХ ЧИСЕЛ | 1972 |

|

SU328454A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Параллельно-последовательный сумматор-вычитатель старшими разрядами вперед на нейронах | 2019 |

|

RU2708501C1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

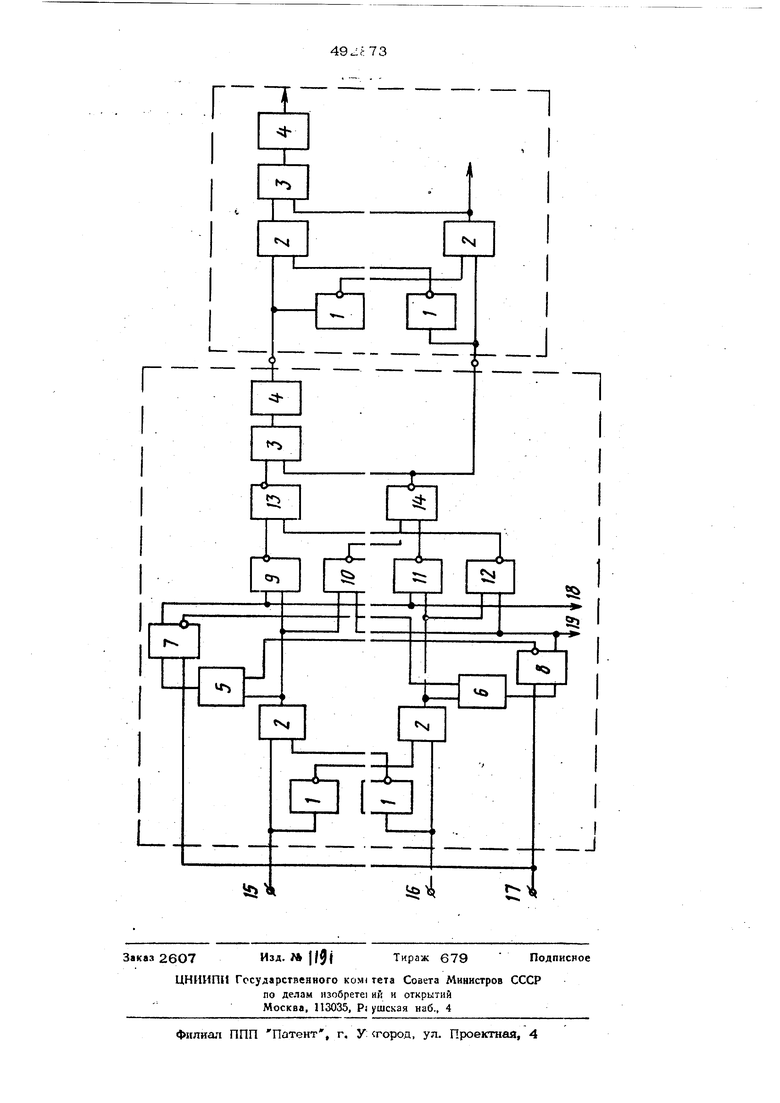

Изобретеиие относится к вычислительной технике и предназначено для вычитания дво-. ичных чисел, следующих старшими разрядами вперед в последовательном коде. Известно устройство для вычитания дво-. ичиых чисел по-авт. св. № 328454, представленных последовательными кодами, начиная со старших разрядов, содержащее . последовательно соединенные логические уэч« лы, каждый из которых выполнен на двух схемах И, двух инверторах, схеме ИЛИ и элементе задержки. Это устройство ВИЛЬНО функционирует лишь при определенном ограничеиии на числа А и В, над ко торыми Иагполняется операция вычитания (А В) и выдает информацию только о разности А-В. Цель изобретения расширение области применения устройства ддя вычитания двоичг ных чисел за счет исключения указанного ограничения (А В), а также за счет то. го, что устройстве выдает разности А-В и В-А и результаты сравнения чисел (. А В). Достигается ето благогаря тому, что 1ервый логический узел содержит третью и четвертую схемы И, триггеры и схемы И-НЕ, выход первой схемы И этого логического узла соединен со входами третье ей схемы И, первой и второй схем VUHEf Выход второй схемы И соединен со вход ми четвертой схемы И, третьей и четвер той схем Н-НЕ. Выходы третьей и четвер той схем И соединены с единичными вхо дами первого и второго триггеров соответ ственно. Единичга 1й выход первого триггера соединен со входами первой и третьей схем VWHE, единичный выход второго триггера соединен со входами второй и четвертой схем tWiE, нулевые выходы первого и второго триггеров соединены со входами 4eTw вертой и третьей схем И-НЕ соответст« венно. Выходы пятой схемы Vt-HE соедим нены с выходами первой н четвертой схем Vt-HE, входы шестой схемы И-НЕ сое динены с выходами второй и третьей схем VWiE, выходы и шестой схем VUHE соедин ны -со входами схемы ИЛИ того же логического узла, выход шестой схе мы И-НЕ соединен с выходом логичес го узла. На чертеже дана схема первого и вт( го логических узлов устройства, Осталы логические углы ицентичны второму лоп скому уэпу. При вычитании П -разрад двоичных чисел устройство содержит п логических узлов. Каждый логический- узел содержит инверторы i, схемы И 2, схему ИЛИ i элемент задержки 4. Логический узел ее держит, кроме того, схемы И 5 и 6, триггеры 7 и 8, схемы И-НЕ 9-14. . ла А и В подаются через входы 15 и К соответственно. Вход 17 служит для уст новки в О триггеров 7 и 8. С выxoдo 18 и 10 снимаются сигналы А В и А В соответственно. Принцип л iHCTEiiH устройства основан на использовании таких преобразований над уменьшаемым и вычитаемым, в результате которых оба числа изменяются одинаковую величину, а искомая разность в процессе этих преобразований остается неизменной. При выполнении этих iipeo6p зований из уменьшаемого образуется чис равное разности двух исходных чисел, а i вычитаемого - нуль. Пусть иьеются дв двоичных числа В 45 и А 42. 32 16 8 4 2 1 В ., 101101 А 1О1010 42, следующих старшими разрядами вперед, в соответствии с обозначенным fetcoM кая дого разряда. Требуется найти разность (т. е. 45-4; #3)..Назовем одноименные разряды, содер жащие единицы, равносильными. Если исключить единицы в равносильных разр дах обоих чисел, т. е. заменить их нулями, иначе говоря - уменьшить каждое из исходных чисел на U1000 40, то ра; ность между числами не изменится. Преобразование по замене единиц в ра носильных разрядах на нули, не приводящее к изме1:знию разности, для сокрашеяш в дальнейшем будем именовать просто исключение. В результате выполнения первого преоб разования исключения получаем два пр образованных числа В и А, В « oodroi 5, А 00001О 2, уже не имаюших равносильных разрядов. Прибавляем к числам В и А по один ковой величине, например по 2. Прлучаем новые преобразованные числа В 7 и А 4, в которых Тпоявдяется равносил ный разряд, вследствие чего оказывается возможным второе преобразование исключение. В 000111 5 + 2 7 А 000100 2 + 000011 3 А ОООООО О. Рассматривая полученный результат можно заметить, что второе преобразова1гаое число А обратилось в нуль, а первое преобразованное число В оказалось равным искомой разности. Число В определяем путем сложения чисел В и А , т. е. В В + А . Процесс сложения здесь может быть за енен операцией дизъюнкции, которую дальнейшем будем называть объединение. Число А можно получить путем сдвига числа А на один разряд в сторону старших разрядов, т. е. А ОООО1О 2, А ООО1ОО 4. Нахождение разности двоичных чисел сводится к последовательному выполнению трех простых преобразований: исключение, объединение и сдвиг. Перед поступлением двоичных чисел А и В на входы 15 и 16 триггеры 7 и 8 устанавливаются в состояние ОГ. Двоичные числа, поступающие на входы 15 и 16, подаются на схемы И 2 непосредственно и через инверторы 1. При одноврел{енном посту1Шении единиц на входы 15 и 16, благодаря инверторам на входы схем И наряду с единицами подаются инвертированные значения А и В, в данном случае нули. Вследствие этого на выхода:; схем И 2 единица отсутствует. При разноименных символах на входах 15 и 16, единица появляется на выходе той из схем И 2, на вход которой она потупает непосредственно, и через схему И 5 или 6 устанавливает триггер 7 или в единичное состояние. Допустим, число А, при этом первым в единичное сотояние устанавливается 8, котоый свслм инверсным сигналом закрывает хему И 5, выход которой связан триг- i ером 7; кроме того, высоким потенциалом единично о выхода триггера 8 открыватся схемы ИгНЕ 1О и 12. Единицы с ь;ходов схем И 2 проходят на схему ИЛИ 3 через схемы И-НН Ю, 14 ... единицы числа А) и через схемы И-НЕ 2, 13 (единицы числа В). С единичного выхода триггера 8 через ыход 19 снимается высокий потенциал.

который говорит о том, что число в А, причем эта информация формируется при первом же несовпадении значений одноименных разрядов чисел А и В.

Операция ; объединение фактически оэкачает сложение таких двух двоичных чисел, у которых отсутствуют единицы в одноименных разрядах. Эта операция реализуется с помощью схемы ИЛИ 3. На ее выходе появляется единица, которая поступила на один из ее входов, Операция сдвиг осуществляется с помошью элемента задержки 4. Все разряды посту пающих на его вход чисел на выходе залер- жиьаются на один такт. Одновременно с поступлением на вход схемы ИЛИ 3 число с выхода схемы И-НЕ 14 вьщается непосредственно на выход первого логического узла.

В каждом из последующих логических узлов реализуется, так же как и в первом, три операции: исключение, объединение и сдвиг Операция исключение реализуется при помоши инверторов 1 и схем И 2, операция объединение реализуется при помощи схем ИЛИ 3, а операция сдвиг - при помощи элементов задержки 4.

Если число А В, то первым в единичное состояние устанавливается триггер 7, который своим инверсным сигналом за- крывает схему И 6, выход которой связан с триггером 8; кроме того, высоким потенциалом единичного выхода триггера 7 открываются схемы И-НЕ 9 и 11. Теперь уже единицы с выходов схем И 2 проходят на схему ИЛИ 3 через схемы И-НЕ9 13(единицы числа А) и через схемы ИЛЕ и 14 (единицы числа В),С единичного выхода

триггера 7 через выход 18 снимается- вы-сокий потенциал, который говорит о том, что число Ар В.

Формула изобретения

Устройство для вычитания двоичных по авт. св. № 328454, о т л и ч а ющ е е с я тем, гтг, с целью расширения области применения, первый логический узел содержит третью и четвертую схемы И, триггеры и схемы И-НЕ, выход первой схемы И этого логического узла соединен со входом третьей схемы И, первой и второй схем И-НЕ, выход второй схемы И соединен со входами четвертой схемы И, третьей и четвертой схем И-НЕ, выходы третьей и четвертой схем И соединены с единичными входами первого и второго триггеров соответственно, единичный выход первого триггера соединен со входами первой и треть схем И-НЕ, единичный выход второго триггера соединен со входами второй и четвертой схем

И-НЕ, нулевые выходы первого и второго триггеров соединены со входами четвертой и третьей схем И-НЕ соответственно, входы пятой схемы И-НЕ соединенъ с выходами первой и четвертой схем И-НЕ, входы щестой схемы И-НЕ соединены с выходами второй и третьей схем И-НЕ, в 1ходы пятой и шестой схем И-НЕ соединены со входами схемы ИЛИ того же логического узла, выход шестой схемы И-НЕ соединен с выходом логичесвого узла..

Авторы

Даты

1975-11-25—Публикация

1974-01-02—Подача