Изобретение относится к области вычислительной техники.

Известны устройства для определения разности чисел, следующих старшими разрядами вперед в последовательном коде, в которых про.изводится предварительное реверсирование чисел.

Целью изобретения является создание простого устройства и повышение его быстродействия.

Это достигается тем, что устройство для вычитания двоичных чисел содержит п последовательно соединенных логических узлов, в каждом из которых первый вход непосредственно соединен с первым входом первой схемы «И и через инвертор с первым входом второй схемы i«H, а второй вход узла-с вторым входом второй схемы «И и через инвертор с вторым входом первой схемы «И. При этом выходы первой и второй схем И связаны с соответствующими входами схемы «ИЛИ, выход которой через элемент задержки соединен с первым входом следующего узла, а выход второй схемы «И - с .вторым входом следующего узла.

Принцип действия устройства основан на использовании таких преобразований над уменьшаемым и вычитаемым, в результате которых оба числа изменяются на одинаковую величину, а искомая .разность в процессе этих

преобразований остается неизменной. Прн выполнении указанных преобразований от уменьшаемого остается число, равное разности двух исходных чисел, а от вычитаемого - нуль.

Пусть имеются два двоичных числа Л 45 и В 23,

32 16 8 4

А О 1

46,

О 1 1 О

:23,

следующих старшим разрядами вперед, в соответствии с обозначенным «весом каждого разряда. Требуется найти разность (т. е. 45-23 22).

Назовем одноименные разряды, содержащие единицы, «равносильными.

В приведенном примере в каждом из чисел имеется по два «равносильных разряда (обведены Пунктиром).

Если исключить единицы в «равносильных разрядах обоих чисел, т. е. заменить их нулями, иначе говоря уменьшить каждое из исходных чисел на 000101 5, то разность .между числами не изменится.

В результате выполнения первого преобразования «исключение получаем два преобразованных чисел Л и В,

0100 , 8 0 1 00 1 ,

уже не имеющих «равносильных разрядов, причем абсолютная величина каждого из них меньше исходных чисел Л и S.

Преобразование «исключение быть применено вновь и для получения чисел Л и Б1.

Для того, чтобы вновь выполнить преобразование «исключение, прибавляем вначале к числам Л и В по одинаковой величине, например по 18. Получаем новые преобразованные числа Л11 58 и , в которых появляется «равносильный разряд, вследствие чего оказывается возможным второе преобразование «исключение.

А

1 1 О 1 0-40 + 18 58, О О 1 О О г 18-f 18 36. Л

После второго преобразования «исключение получаем новые преобразованные числа дш л дш jjg имеющие «равносильных разрядов.

Л™ 0 1101 , 0010 .

Для того, чтобы к преобразованным числам дт JJ п снова применить «исключение, прибавляем к ним по 4.

Получаем новые преобразованные числа Л и fiiv.

1

1 1 О 26 + 4 30, О О О + 4 8,

вновь имеющие «равносильный разряд.

Снова применяем преобразование «исключение. Получаем новые преобразованные числа Л и В.

Л 0 1011 , B Q 0000 .

Рассматривая полученный результат, можно заметить, что второе преобразованное число jS обратилось в нуль, а первое преобразованное число Л оказалось равным искомой разности.

Процесс получения последующих преобразованных чисел например Л и В из предыдущих Л и Б, фаа тически происходит следующим образом.

Число Л определяем путем чисел Л1 и В т. е. + 5.

Процесс сложения здесь упрощается, так как в каждом из разрядов суммируемых чисел складываются только «О и «1 или «О и «О. При таком упрощении сложения чисел отпадает необходимость в переносе «1 из разряда в разряд, поэтому сложение может быть заменено операцией дизъюнкции, которую в дальнейщем мы будем называть - «объединение.

Число В получить путем сдвига числа В на один разряд в сторону старших разрядов, т. е.

56 0 1001 ,

0010 0 36.

В соответствии с рассмотренным примером все последующие преобразования числа

Q Л, В™-В получим также путем преобразований: «исключение «объедиршние и «сдвиг.

Таким образом, нахождение разности двоичных чисел сводится к последовательному выполнению трех простых преобразований: «исключение, «объединение и «сдвиг, в результате которых оказывается возмол ным простым путем получить разность для чисел, следующих старшими разрядами вперед в послеQ довательном коде.

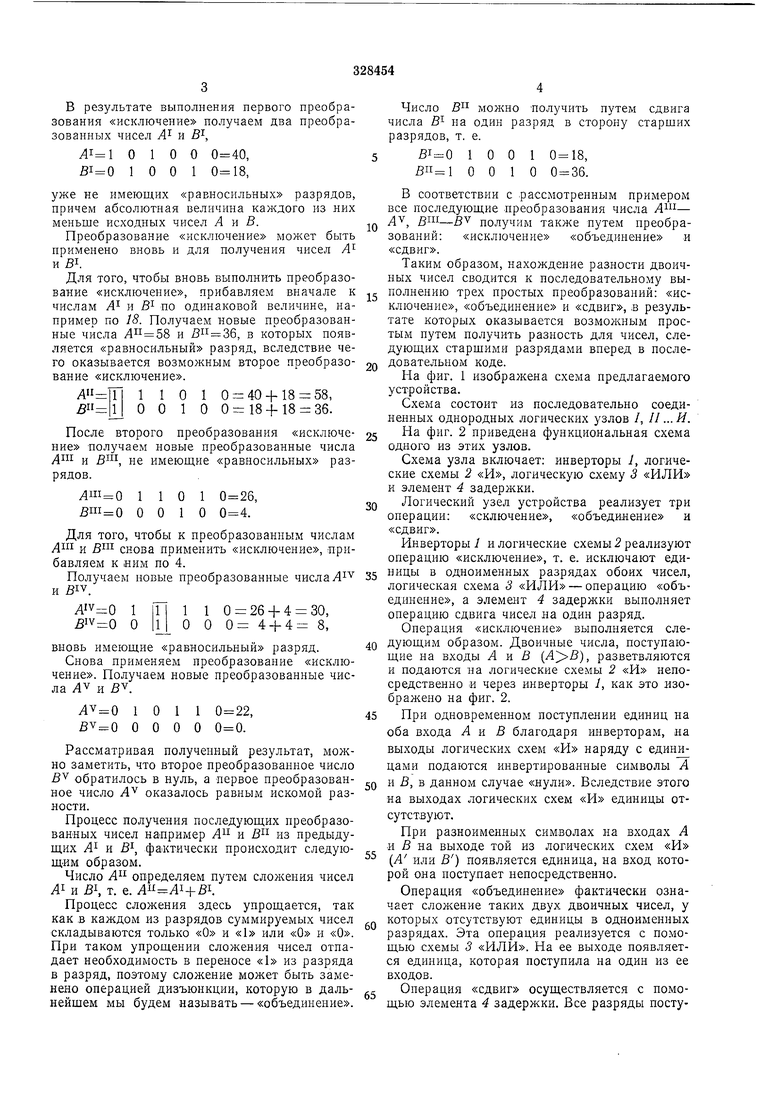

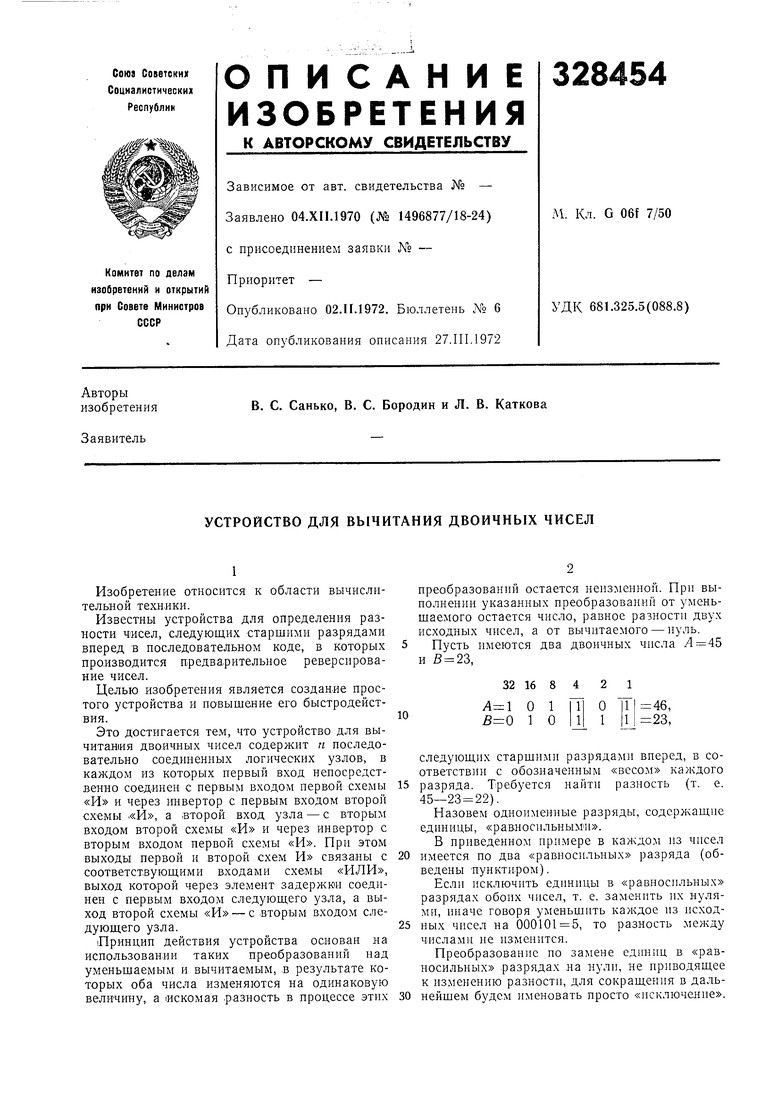

Па фиг. 1 изображена схема предлагаемого устройства.

Схема состоит из последовательно соединенных однородных логических узлов /, //... И.

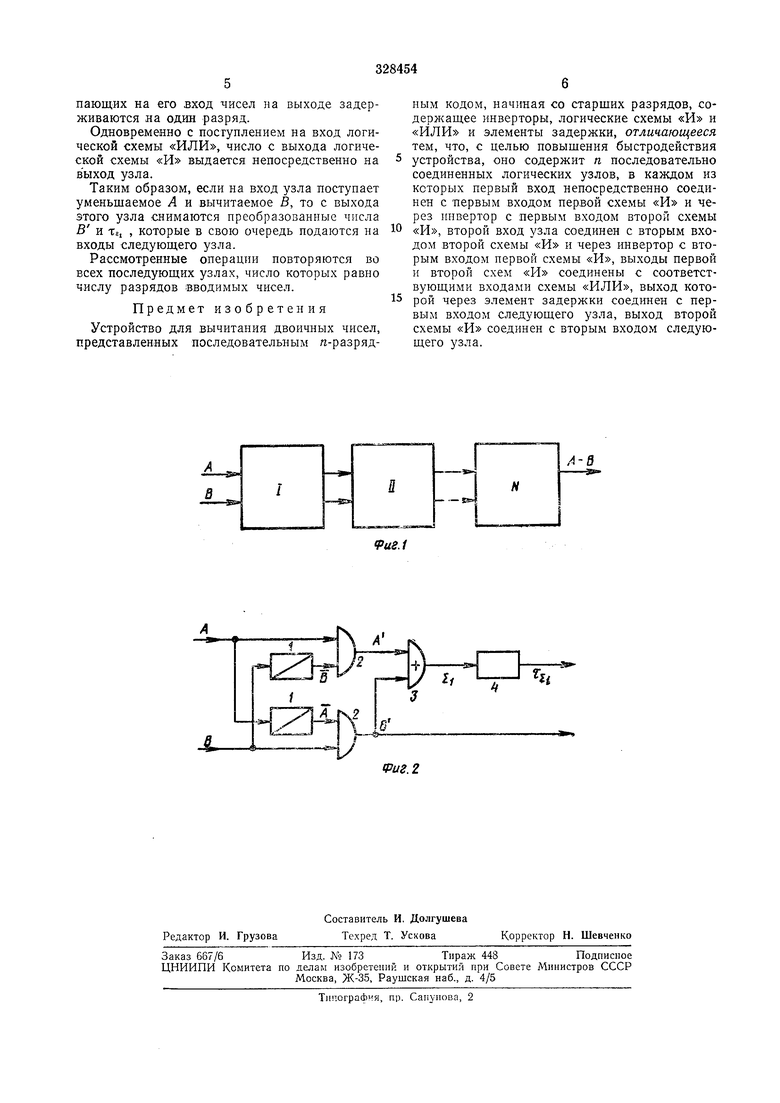

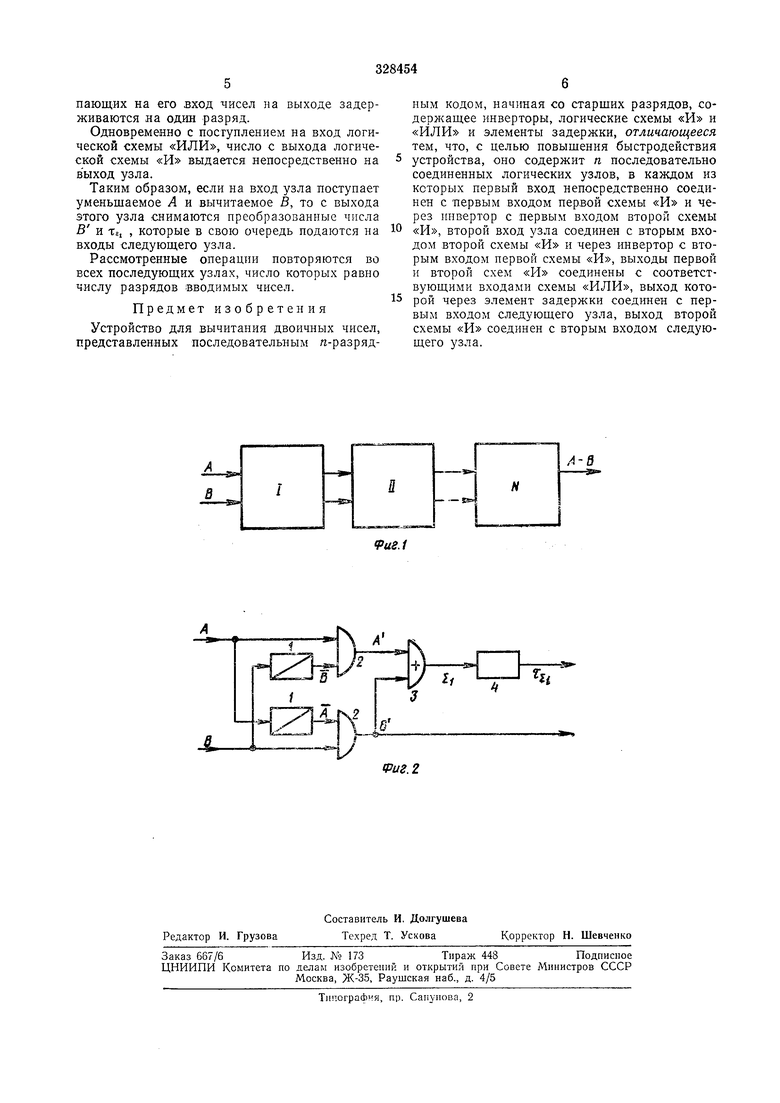

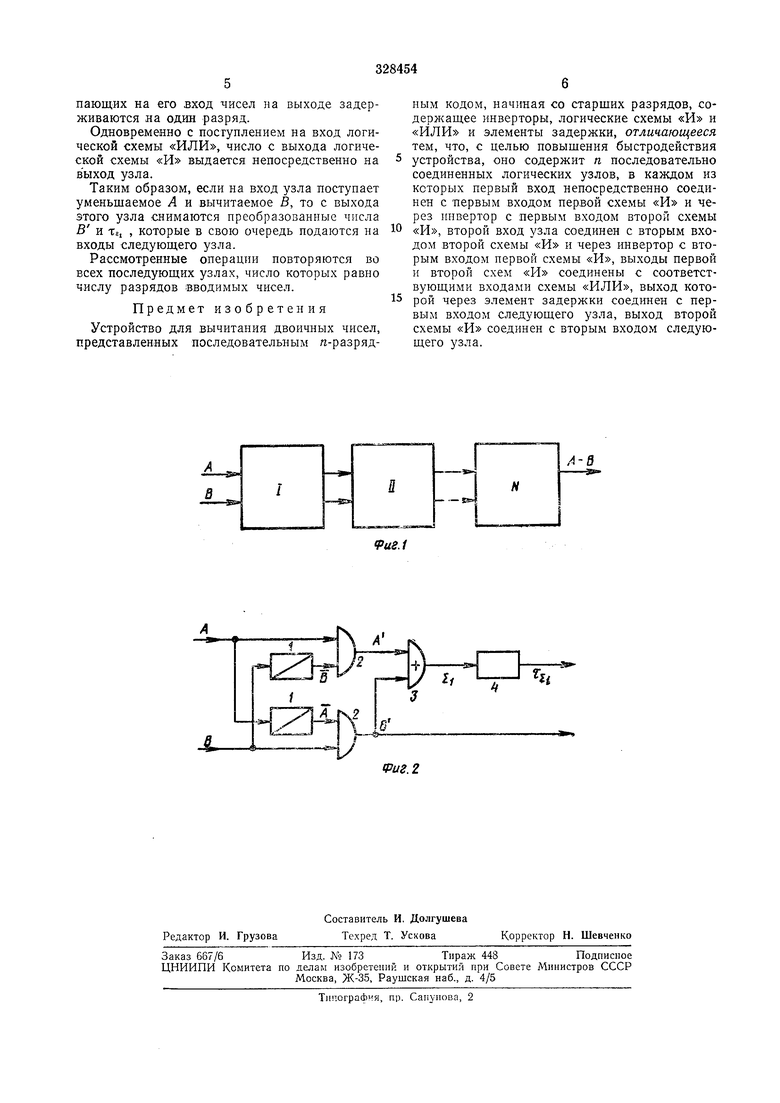

5 На фиг. 2 приведена функциональная схема одного из этих узлов.

Схема узла включает: инверторы 1, логические схемы 2 «И, логическую схему 3 «ИЛИ и элемент 4 задержки.

0 Логический узел устройства реализует три операции: «сключение, «объединение и «сдвиг.

Инверторы / алогические схемы2реализуют операцию «исключение, т. е. исключают еди5 ницы в одноименных разрядах обоих чисел, логическая схема 3 «ИЛИ - операцию «объединение, а элемент 4 задержки выполняет операцию сдвига чисел на один разряд. Онерация «исключение выполняется следующим образом. Двоичные числа, поступающие на входы А н В (), разветвляются и подаются на логические схемы 2 «И непосредственно и через инверторы 1, как это изображено на фиг. 2.

5 При одновременном поступлении единиц на оба входа Л и В благодаря инверторам, на выходы логических схем «И наряду с цами подаются инвертированные символы Л

0 и В, в данном случае «нули. Вследствие этого на выходах логических схем «И единицы отсутствуют.

При разноименных символах на входах Л и В на выходе той из логических схем «И

(Л или В ) появляется единица, на вход которой она поступает непосредственно.

Операция «объединение фактически означает таких двух двоичных чисел, у

„ которых отсутствуют единицы в одноименных разрядах. Эта операция реализуется с помощью схемы 3 «ИЛИ. На ее выходе появляется единица, которая поступила на один из ее входов.

лающих на его вход чисел на выходе задерживаются на один разряд.

Одновременно с поступлением на вход логической схемы «ИЛИ, число с выхода логической схемы «И выдается непосредственно на выход узла.

Таким образом, если на вход узла поступает уменьшаемое А и вычитаемое В, то с выхода этого узла снимаются преобразованные числа В и Тг, , которые в свою очередь подаются на входы следующего узла.

Рассмотренные операции повторяются во всех последующих узлах, число которых равно числу разрядов вводимых чисел.

Предмет изобретения

Устройство для вычитания двоичных чисел, представленных последовательным л-разрядньш кодом, начиная со старших разрядов, содержащее инверторы, логические схемы «И и «ИЛИ и элементы задержки, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит п последовательно соединенных логических узлов, в каждом из которых первый вход непосредственно соединен с первым входом первой схемы «И и через инвертор с первым входом второй схемы «И, второй вход узла соединен с вторым входом второй схемы «И и через инвертор с вторым входом первой схемы «И, выходы первой и второй схем «И соединены с соответствующими входами схемы «ИЛИ, выход которой через элемент задержки соединен с первым входом следующего узла, выход второй схемы «И соединен с вторым входом следующего узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания двоичных чисел | 1974 |

|

SU492873A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР С ПЕРЕКЛЮЧАЕМОЙЛОГИКОЙ | 1969 |

|

SU256014A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВОИЧПО- ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ | 1969 |

|

SU237461A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ЧИСЛОВЫХ ВЕЛИЧИН | 1965 |

|

SU167366A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАИБОЛЬШЕЙ РАЗНОСТИ | 1967 |

|

SU204021A1 |

| Устройство для сравнивания чисел | 1984 |

|

SU1221649A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

Даты

1972-01-01—Публикация