(54) АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1972 |

|

SU493163A1 |

| Ассоциативное запоминающее устройство | 1972 |

|

SU499762A1 |

| Ассоциативное запоминающее устройсво | 1971 |

|

SU493165A1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU576608A1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU604033A1 |

| Устройство для поиска информации в ассоциативной памяти | 1988 |

|

SU1617460A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1429169A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| Ассоциативное запоминающее устройство | 1971 |

|

SU493162A1 |

| Ассоциативное запоминающее устройство | 1978 |

|

SU701349A1 |

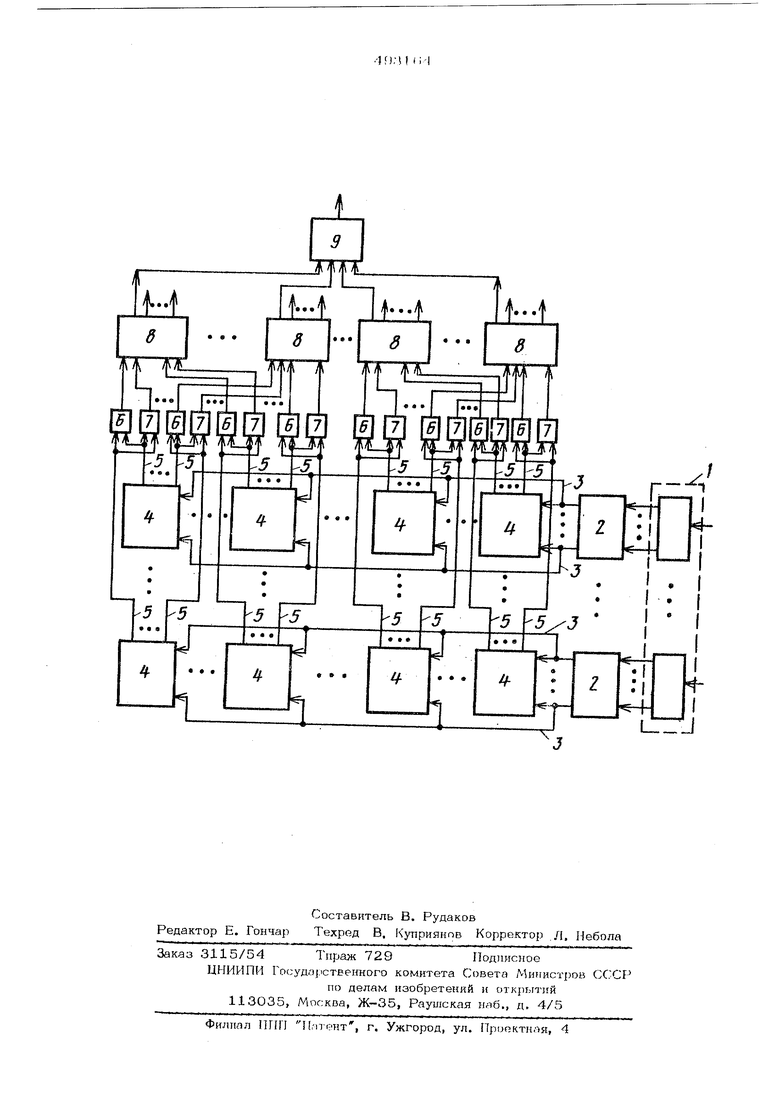

Изобретение относится к запоминающим устройствам. Известно ассоциативное запоминающее устройство (АЗУ), содержащее группы адресных запоминающих модулей, общие адрес ные щины которых подключены к выходам соответствующих дещифраторов опроса. Однако известное устройство имеет больг шое количество оборудования, вызванное неэффективным использованием адресных запоминающих модулей при большой емкости этих модулей. Неэффективность известного устройства обусловлена тем, что количество адресных щкн, необходимых для записи к - к разрядного кода признаков, равно 2 , так как этот код записывается в элементы ра; рядной линии, связанной с соответствующим детектором, в виде единицы на фоне нулей (в каждом модуле). При этом, номер адресной линии, по которой записывасэтся едини- да , определяется кодом соответствующего ассоциативного слова. Цель изобретения - сокращение количеств оборудования. Описываемое АЗУ отличаете я от известн го тем, что оно содержит выходные дешиф раторы, входы которых через схемы совпадения подключены к соответствующим одно именным разрядным -иинам адресных запоминающих модулей каж.аой группы, а первые выходы выходных дешифраторов подсоединены к введенной ; устройство приоритетной схеме. На чертеже приведена блок-схема устройства. Устройство состоит из регистра опро са, выходы которого соединены через дешифраторы 2 опроса с адресными шинами 3 соответствующих адресных запоминающих модулей 4, объедине}:;1ых общими шинами 3 в группы. Разрядные шины 5 модулей одной группы, связанных с различными дешифраторами 2 опроса, через схемы 6 и 7 совпадения по нулям и единицам подсоединены ко входам выходных дешифраторов 8, выполняюи их функцию детекторов. К первым выходам дешифраторов 8 подключена приоритетная схема Э. Работа устройства заключается в следук щем. Перед записью нового ассоциативного (..чова гщредсляется ш.гходной пепшфратор 8, ;поаи «ншчй с модулями 4, у которых по ore элементы, cBflr.vnftiif ie с вь1бранпым11 ад{есными шянпмй 3, пулевой код. Код ассоциптившпо слове поступает на регистр 1 опроса и п соответствии с этим кодом воабуждяется по одной адресной тине 3 на к 1ждый дешифрато}) 2 опроса. Е:;сли в каком-либо наборе модулей 4, связанных с идлим выходным дешифратором 8, во всех элементах на возбужденных адресных шинах 3 записаны нули, то FTO выходах всех схем 6 совпадения, соединенных с этим дещиф™ ратором, появл$потся сигналы совпадения, в роэультате чего возбуждается первый выход йешифратора 8. В ячейке модуля 4, соединенной с этим выходом, указываются все свободные Р -разрядные признаковые комбинации (либо одна гранич)1ая комбинация). В соответствии с одной из этих комбинаций возбуждаются разрядные ШШ1Ы 5, связанные с выбранным дешифратором 8, и элементы н пересечении выбранных адресных и разрядных шин записываются единичные коды. После этого данная комбинация исключается из числа свободных, т. е. записываются нули в ооотЬетствующие элементы ячейки модуля Если свободных выходных дешифраторов 8 несколько, то ячейка для записи (и соответствующий дешифратор 8) определяются с помощью схемы 9 приоритета, выполне№ной любым известным способом, аналогично схемам установления приоритета прк многозначной выборке. При опросе возбуждается по одной адрес ной шине 3 на каждый дешифратор 2 опроса . в соответствии с кодом опроса на регистре 1. Если в кaкo -либo наборе модулей 4, соединенных С одним дешифратором 8, совпадают комбинации, записанные в модулях, которые соответствуют различным дешифраторам 2, то в соответствии с этой комби нацией возбуждается ровно половина схем 6 и 7 совпадения данного дешифратора 8. В результате, на выходе выбранного дешифр тора 8 появляется сигнал совпадения, приче номер выхода определяется выбранной комбинацией. Так как выборка иди м11/1Ч11.чч, т. . и ЛЗУ запислны тольк) р.юлкчякициегя слоем, то п остальных де1)птф)1Я1 прлх 8 вопбуждло - ся меньше г оловипы схем 6 и 7 совппдсшпя. Следоввтельно, как минимум, в одном из разрядов признаковог о кодл не воз(3уждаюг- ся как схема 6 совпадения, так и схема 7 совпадения, т. е. у невыбракных дец ифратг ров ле может быть возбужден ни оди}1 вьнход. В режиме опроса первые выхоль) дсч- шифраторов 8 блокируются, так как свободные ячейки могут дать паразитный сигнал совпадения. Если при записи оказывается, что все ячейки АЗУ за)1яты, то сначала О1гределяется местоположение ассоциативног-о слова, которое может быть стерто, и запоминается соответствующая признаковая комбинация, Так как для записи ассоциативных признаков используется не более половины всех запоминающих элементов, то далее производится проверка, может ли новое слово быть записано в АЗУ. Если проверка оказывается успешной, то на пересечении выбранных адресных и разрядных шин записывается освободившаяся признаковая комбинация, В противном случае процедура перезаписи продолжается до тех пор, когда можно будет записать новое слово. Формула изобретения Ассоциативное запоминающее устройство, содержащее группы адресных запоминающих модулей, общие адресные шины которых подключены к выходам соответствующих де шифраторов опроса, входы которых подсоединены к соответствующим выходам регист- ра опроса, отличающееся тем, что, с целью сокращения количества оборудования, оно содержит выходные дещифраторы, входы которых через схемы совпадения подключены к соответствующим одноименным разрядным шинам адресных запоминающих модулей каждой группы, а первые выходы выходных дещифраторов подсоединены к введенной в устройство приоритетной схеме.

i m mmmmm mmmmmmmi;

Авторы

Даты

1977-08-25—Публикация

1971-10-18—Подача