(54) АССОЦИАТИВНОЕЗАПОМИНАЮЩЕЕ УСТРС СТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1978 |

|

SU701349A1 |

| Ассоциативное запоминающее устройство | 1974 |

|

SU588561A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Ассоциативное запоминающее устройство | 1971 |

|

SU493162A1 |

| Ассоциативное запоминающее устройство | 1972 |

|

SU499762A1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU576608A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| Ассоциативное запоминающее устройство | 1972 |

|

SU493163A1 |

| Вычислительное устройство | 1990 |

|

SU1784969A1 |

| Устройство таймеров | 1983 |

|

SU1163309A1 |

1

Изобретение относится к запоминающим устройствам.

Известно ассоциативное запоминающее устройство, которое содержит адресные запоминающие блоки, детекторы, дещифраторы опроса, регистр опроса 1.

Недостатком известного устройства является неэффективное использование оборудования устройства.

Наиболее близким техническим решением к предлагаемому изобретению является ассоциативное запоминающее устройство, содержащее группы адресных запоминающих блоков с адресными и выходными разрядными щинами, организованные в виде прямоугольной матрицы, дещифраторы опроса, выходы которых соединены с адресными щинами запоминающих блоков соответствующей строки матрицы, элементы ИЛИ, выходы которых подключены к входам соответствующих дещифраторов опроса, а входы - к соответствующим выходам триггеров регистра операнда и дещифратора операций, причем регистр операнда выполнен в виде нескольких регистров сдвига, а регистр маски - в виде нескольких кольцевых регистров сдвига по числу строк матрицы запоминающих блоков 2.

Однако быстродействие известного устройства при выполнении логических операций ограничено наличием в устройстве только одного выходного регистра.

Цель изобретения - увеличение быстродействия устройства.

Это достигается тем, что устройство содержит сумматоры по модулю два, выходные разрядные щины каждого адресного запоминающего блока в группе, состоящей из двух блоков, соединены с информационными входами сумматоров по модулю два, выходы которых подключены к одноименным разрядным щинам записи другого блока группы, а управляющие входы сумматоров, информационные входы и входы управления записью и выборкой запоминающих блоков подсоединены к соответствующим выходам дещифратора операций, входы которого подключены к выходам триггеров регистра операнда.

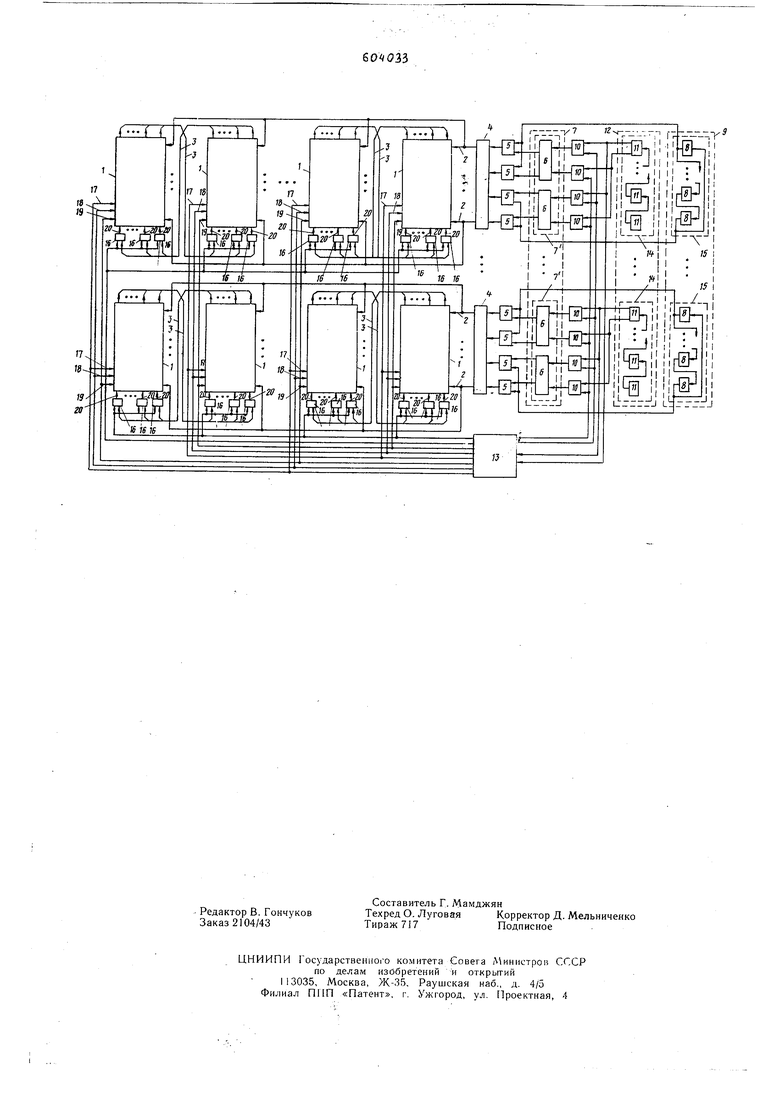

На чертеже приведена блок-схема устройства.

Оно содержит адресные запоминающие блоки 1 (выполненные, например в виде интегральных микросхем) с адресными щинами 2 и выходными разрядными щинами 3. Блоки 1 организованы в виде прямоугольной матрицы, число строк которой равно числу дешифраторов опроса 4. Выходы дешифраторов 4 соединены с соответствующими шинами 2 блоков 1. Входы указанных дешифраторов 4 соединены с выходами элементов ИЛИ 5, одни входы которых подключены к прямым или обратным выходам соответствуюш.их триггеров 6 регистра 7 опроса, а другие - к прямым выходам триггеров 8 регистра 9 маски. Устройство солержпт также элементы И 10, выходы которых присоединены к со6тветствуюи1им входам триггеров б регистра 7. Одни входы элементов И 10 соединены с соответствуюш.ими выходами триггеров 11 регистра 12 операнда, а другие- с управляющими выходами дешифратора операций 13. Регистр 12 выполнен в виде нескольких независимых регистров 14 сдвига, а регистр 9 - в виде нескольких кольцевых регистров 15 сдвига по числу строк матрицы из блоков 1. Устройство содержит также сумматоры 16 по модулю два. Каждый блок 1 имеет вход 17 управления записью, вход 18 управления выборкой, информационный вход 19 и разрядные шины 20 записи по числу шин 3. Блоки 1 каждой строки объединены в группы по два, шины 3 каждого блока в группе соединены с информационными входами сумматоров 16, выходы которых подключены к соответствующи-м шинам 20 другого блока 1 данной группы. Управляющие входы сумматоров 16 данной строки, а также вхоБлок 1.1 Выходы 0101 1пиныЗ дешифратора 4 шины На вход 17 блока 1.1 подается сигнал разрешения считывания (например логический «О), на вход 17 блока 1.2 - сигнал разрешения записи (например логическая «1), на входы 18 обоих блоков - сигнал разрешения выборки и на вход 19 блока 1.2 - сигнал «О. В результате на шинах 3 блока 1.1 появляются считанные сигналы 0101. На общий вход сумматоров 16 блока 1.2 подается сигнал «О, что приводит к появлению на шинах записи этого блока сигналов 0101 и записи кода «О на пересечении 2-й и 4-й разБлок 1 Выходы дешиф001 1 Ш ратора 4 ды 17, 18, 19 блоков 1 каждого столбца матрицы 1тодключены к соответствующим выходам дешифратора 13. Входы дешифратора 13 подсоединены к выходам соответствующих триггеров 11 регистра 12. Работу устройства проиллюстрируем на Примере выполнения логических операций в группе, составленной из двух запоминающих блоков 1.1 и 1.2 с восемью адресными шинами 2 и четырьмя выходными разрядными шинами 3 (на чертеже этот вариант не показан). Рассмотрим, например, последовательность действий при выполнении операции инвертирования массива чисел, хранящихся в блоке 1.1. Все запоминающие элементы блока 1.2 предварительно устанавливаются в состояние «1. В блоке 1.1 хранятся четыре числа 011, 010, 001, 000, записанные на четырех его разрядных линиях в коде «1 на фоне «О. На регистр 15, являющийся регистром маски этих блоков, заносится код ПО, на регистр 14 заносится код первого операнда 000. Код «О с выхода триггера 11 младщего разряда регистра 14, поступа1Ьщий на входы элементов И 10, используется для установки в «О триг-. герое 6 регистра 7. Код опроса 000 и код маски 110, поступая на входы элементов ИЛИ 5 обеспечивают возбуждение четных выходов - 000, 010, 100, 110 дешифратора 4 и соответствующих шин 2 обоих блоков. лок 1.2Блок 1.2 (до записи)(после записи) И1010 111111 il1010 111111 И1010 И1111 111010 и11Н , рядных линий и четных адресных шин блока 1.2 (запись производится по коду «1 на шине 20). В следующем такте обращения код на регистре 14 сдвигается на один шаг - 000, код на регистре 15 циклически сдвигается - 101, что приводит к возбуждению 000, 001, 100, 101 - выходов дешифратора 4. Запись «О в блок 1.2 производится также как в первом такте - в запоминающие элементы на нересечении возбужденных шин 2 и 20. Блок 1.2 Блок 1.2 {после записи) (дозаписи) 1000 1010 1111 1010 1111 1010 1111 1010 111 шины 20 ООП В третьем такте сдвиг кодов на регистре 14 -- 000 и регистре 15 - 011 приводит к возбуждению 000, 001, 010, 011 Блок 1.1

Выходы деши(|1ратора 4 1111 шины 3

0001 0010 0100 1000 0000

оооо

OfJOO

шины 20 0000

в четвертом такте на регистр 14 заносится код 111 (обратный коду 000), код на регистре 15 циклически сдвигается, - 110, при этом возбуждаются 001, 011, 101, 11.1 -, выходы дешифратора 4. В пятом такте возбуждаются выходы дешифратора - 010, 011, ПО, 111, в шестом такте - 100, 101, ПО. 111. В результате после выполнения inecToro такта блок 1.2 содержит следующую информацию:

оооо

0000

ОООО

ОООО

1000

0100

0010

0001,

которая в обычном позиционном коде эквивалентна 100. 101, ПО, 111, т. е. обратным кодам исходных чисел в блоке 1.1.

Операция перезаписи чисел в прямом коде из блока 1.1 в блок 1.2 выполняется аналогично за одним исключением на вторые входы сумматоров 16 блока 1.2 с выхода деишфратора 13 поступает код «1. ане«0. что приводит к инвертированию ин()ормации, поступаюпгей с шин 3 блока 1.1 на шины 20 блока 1.2.

Операции равнозначности и неравнозначности (суммирования по модулю два) кода первого операнда с содержимым блока 1.1 заменяются поразрядными операциями инвертирования и.ж перезаписи в пря.мо.м коде. Если прямой (обратный) код операнда на регистре 14 содержит «1 («О) в данном разряде, то при выполнении операции равнозначности производится перезапись в прямом коде, а при выполнении операции неравнозначности - поразрядное инвертирование содержимого блока 1.1.

Блок 1.2

Блок 1.2 (до записи) (после записи)

0000 0000 0000 ODOO 1000 1100 1010.

Замена «1 на «О приводит к за.мене операции перезаписи на инвертирование.

Формула изобретения

Ассоциативное заноминающее устройство, содержащее дешифраторы опроса, выходы которых соединены с адресными П1инами соответствующих адресных запоминающих блоков, объедипенных в группы, а входы дешп(;1р;п(1ров опроса соединены с выходами э.юмсп тов ИЛИ, входы которых подключены к соответствующим выходам регистров опроса и маски, э.чементы И, входы которых соедипоп, с соответствующими выходами регистра операнда и дешифратора операций, а выходы с входа.ми регистра опроса, отличающееся тем. что, с целью увеличения быстродействия устрой ства, оно содержит сумматоры по модулю д.ва. управляющие входы которых, а также информационные входы и входы управления записью и выборкой .запоминающих блоков соединены с соответствующими выходами дешифратора операций, входы которого подключены к выходам регистра операнда, выходные разряднр)1е шины каждого адресного запоминающего блока каждой группы подключены к информационным входам сумматоров по модулю два, выходы которых соединены с одноименными разрядными щинами записи другого адресного запоминающего блока данной группы.

Источники информации, принятые во внимание при экспертизе:

Авторы

Даты

1978-04-25—Публикация

1975-10-28—Подача