1

Известно ассоциативное запоминающее устройство, содержащее дешифраторы онроса, входы которых соединены с выходами соответствующих регистров опроса, а выходы - с адресными итинамн адресных заноминающих блоков, одноименные разрядные щины которых подключены к соответствующим детекторам. В известном устройстве избыточность нрн реализации ассоциативного поиска на адресных элементах быстро возрастает с увеличеиием числа адресных шин запоминаюищх блоков, т. е. с увеличением их информацнонной емкости.

Цель изобретения состоит в упрощении устройства. В оиисываемом устройстве это достигается тем, что оно содержит дополнительные регистр онроса и дешифратор онроса, выходы которого подключены к управляющим входам соответствующих детекторов, а входы - к выходам дополнительного регистра опроса, соединенным с управляющими входами других дешифраторов онроса.

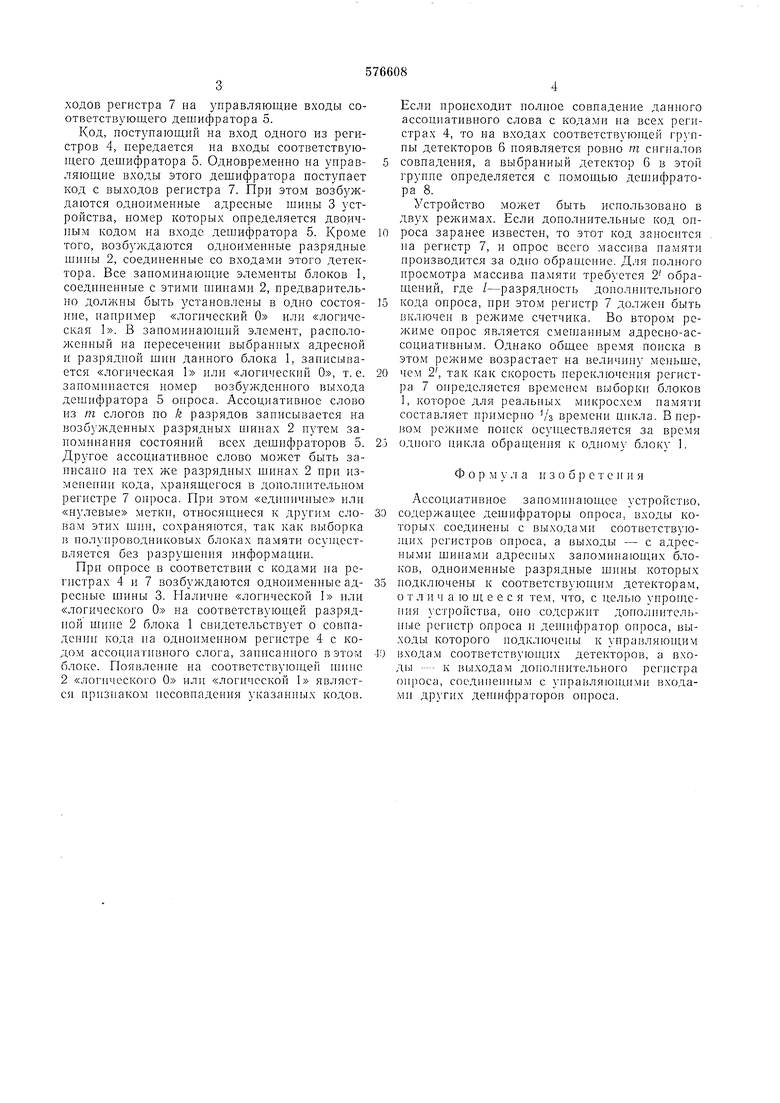

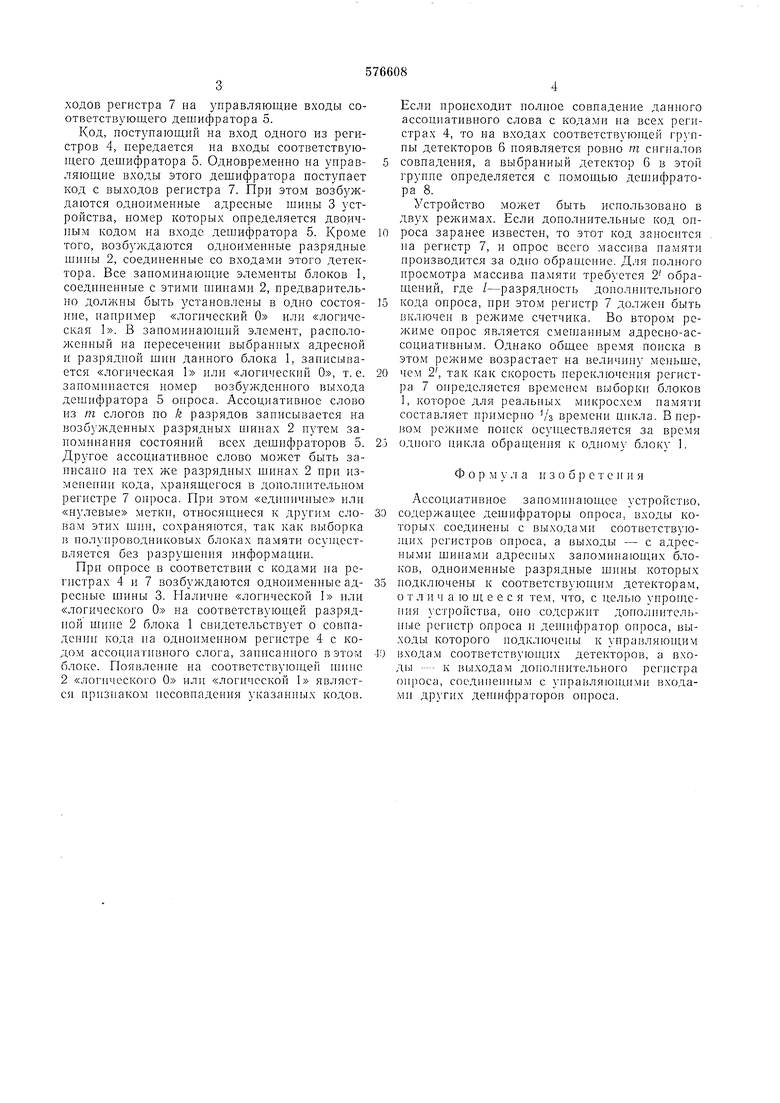

На чертеже приведена блок-схема описываемого устройства.

Оно содержит адресные запомннающие блоки 1 с разрядными шинами 2 и адресными шинами 3, регистры 4 онроса и дешифраторы 5 онроса. Входы дешифраторов 5 соединены с выходами соответствующих регистров 4, а выходы - с адресными шинями 3 соответствующих блоков 1. Устройство содержит также детекторы 6, которые выполнены в виде схем совпадения с числом входов, равным чнслу регистров 4 н дешнфраторов 5, донолннтельный регистр 7 опроса и дополнительный дешифратор 8 онроса. Входы детекторов 6 соедннены с одноименными шинами 2 блоков 1, подключенных к выходам различиых дешифраторов 5. К каждой груиие одиоименных uiiiH 2 блоков 1 нодключено несколько детекторов 6, управляющие входы которых присоединены к соответствующим выходам дешифратора 8. Выходы регистра 7 соединены с соответствующими входамн дешифратора 8 н уиравляюищми входами дешифраторов 5. Дешифраторы 5 и заноминающне блоки 1 могут быть объединены в едином иитегрально.м блоке памяти.

При записи новых ассоднативных ирнзнаков каждый блок 1 разбнвается па слоги, величина которых определяется как 2, где k - число триггеров в каждом регистре 4 опроса. Число таких слогов, размещенных в одноименных разрядных шинах одного блока I, определяется как 2, где с- число триггеров регистра 7, а 2-число выходов дешифратора 8. Выбор заданного слога в каждом блоке 1 осуществляется за счет нередачи двоичного

кода, онрелрляюшего номеп чтогп слога, с вы3

ходов регистра 7 на управляющие входы соответствующего дешифратора 5.

Код,, поступающий па вход одного из регистров 4, иередается па входы соответствуюnj,ero дещифратора 5. Одновременно на управляющие входы этого дещифратора поступает код с выходов регистра 7. При этом возбз ждаются одноименные адресные щипы 3 устройства, номер которых определяется двоичиым кодом на входе дешифратора 5. Кроме того, возбуждаются одноименные разрядные шипы 2, соединенные со входами этого детектора. Все запомипаюпще элементы блоков 1, соединенные с этими щинами 2, предварительно должны быть установлены в одно состояние, панример «логический О или «логическая 1. В запомпнаюи:ий элемент, расположенный на пересечении выбранных адресной и разрядной щии данного блока 1, записывается «логическая 1 или «логический О, т.е. заномииается номер возбужденного выхода дешифратора 5 опроса. Ассоциативное слово из т слогов по /г разрядов записывается на возбужденных разрядных шинах 2 нутем запомннання состояний всех дешифраторов 5. Другое ассоциативное слово может быть записано на тех же разрядных щинах 2 при нз лепеппи кода, хранящегося в дополнительном регистре 7 опроса. При этом «единичные или «нулевые метки, относящнеея к другим еловам этих шин, сохраняются, так как выборка в полупроводниковых блоках памяти осущестБляетея без разрушения информации.

При опросе в соответствпи с кодами па рег 1етрах 4 и 7 возбуждаютея одноимеииые адресные шины 3. Паличие «логической 1 или «логического О на соответствующей разрядной щнне 2 блока 1 свидетельствует о совпадении кода на одноименном регистре 4 с кодом ассоциативного слога, заннсаниого в этом блоке. Появление на соответствующей нлше 2 «логического О или «логической 1 является ирнзнаком несовнадения указанных кодов.

4

Еелн происходит полное совпадение данного ассоциативного слова с кодами па всех регистрах 4, то иа входах соответствуюи1ей группы детекторов 6 ноявляетея ровно m сигналов совпадения, а выбранный детектор 6 в этой группе определяется с помощью дешифратора 8.

Устройство может быть использовано в двух режимах. Если донолнптельные код онроса заранее извеетеи, то этот код заносится иа регистр 7, и опрос всего массива памяти производится за одио обрапдение. Для полного просмотра массива памяти требуется 2 обращений, где /-разрядиость донолинтельного кода оироеа, при этом регистр 7 должен быть включен в режиме счетчика. Во втором режиме оирос является смен:аииым адресио-ассоциативиым. Однако общее время поиска в этом режиме возрастает на величину мепьще, чем 2, так как екорость нереключення регистра 7 определяется в)еменем выборки блоков I, которое для реальиых микросхем памяти составляет примерио з времени цикла. В первом режиме попек осун;еетвляетея за время одного никла обраи1,ения к одному блоку 1.

Ф о р м у . а и 3 о б ) е т е и и я

Ассоциативное запоминающее устройство, содержаи;ее дещцфраторы опроса, входы которых соединены с выходамн соответствующих регистров опроса, а выходы - с адресными шииами адресных заиоминающих блоков, одноименные разрядные шнны которых нодключены к соответствуюнгим детекторам, о т л и ч а ю и е е с я тем, что, е целью унрон1еиия уст|)ойства, оно содержит дополпительные регистр опроса и деишфратор онроса, выходы которого иодключепы к управляюпи-1м в.ходам соответствуюнцьх детекторов, а входы -- к выходам дополнительного регистра oHjioca, соедииеиным с управляюихими входами других ден1ифраторов оироеа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1971 |

|

SU493162A1 |

| Ассоциативное запоминающее устройство | 1972 |

|

SU493163A1 |

| Ассоциативное запоминающее устройство | 1971 |

|

SU493164A1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU604033A1 |

| Ассоциативное запоминающее устройство | 1972 |

|

SU499762A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU310307A1 |

| Система для обмена данными между информационными процессорами | 1980 |

|

SU1001070A1 |

| ПРИОРИТЕТНОЕ УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1970 |

|

SU281901A1 |

| Ассоциативное запоминающее устройство | 1974 |

|

SU588561A1 |

Авторы

Даты

1977-10-15—Публикация

1975-02-13—Подача