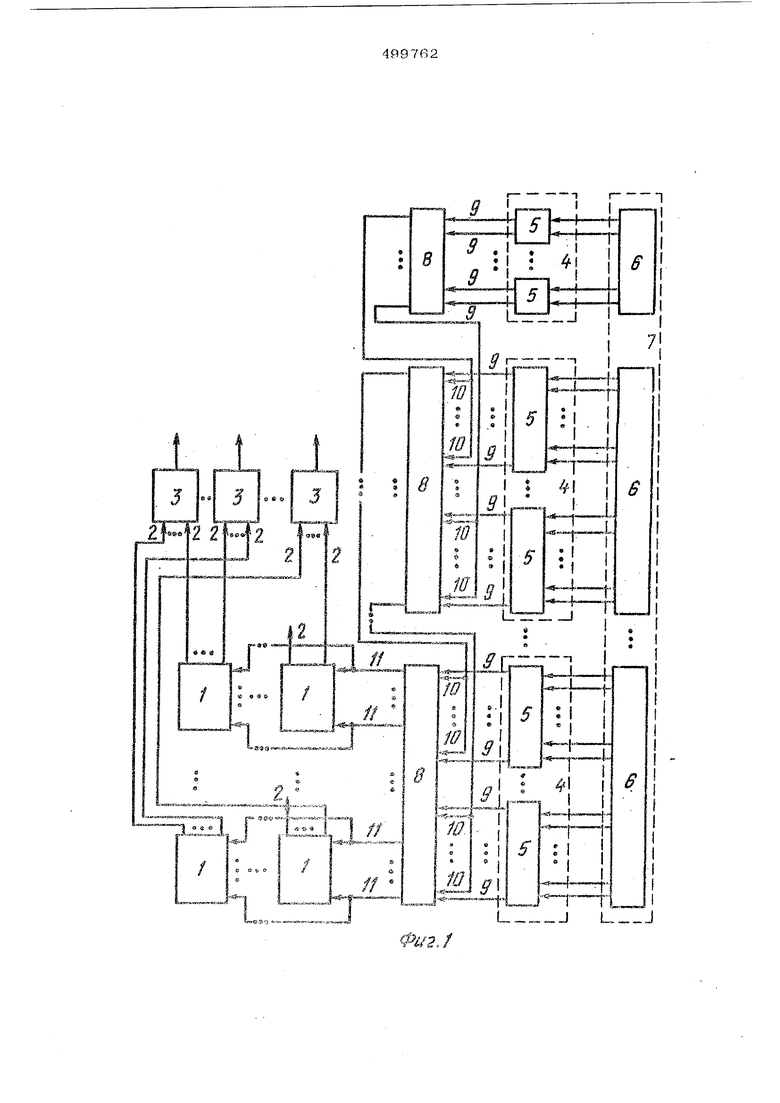

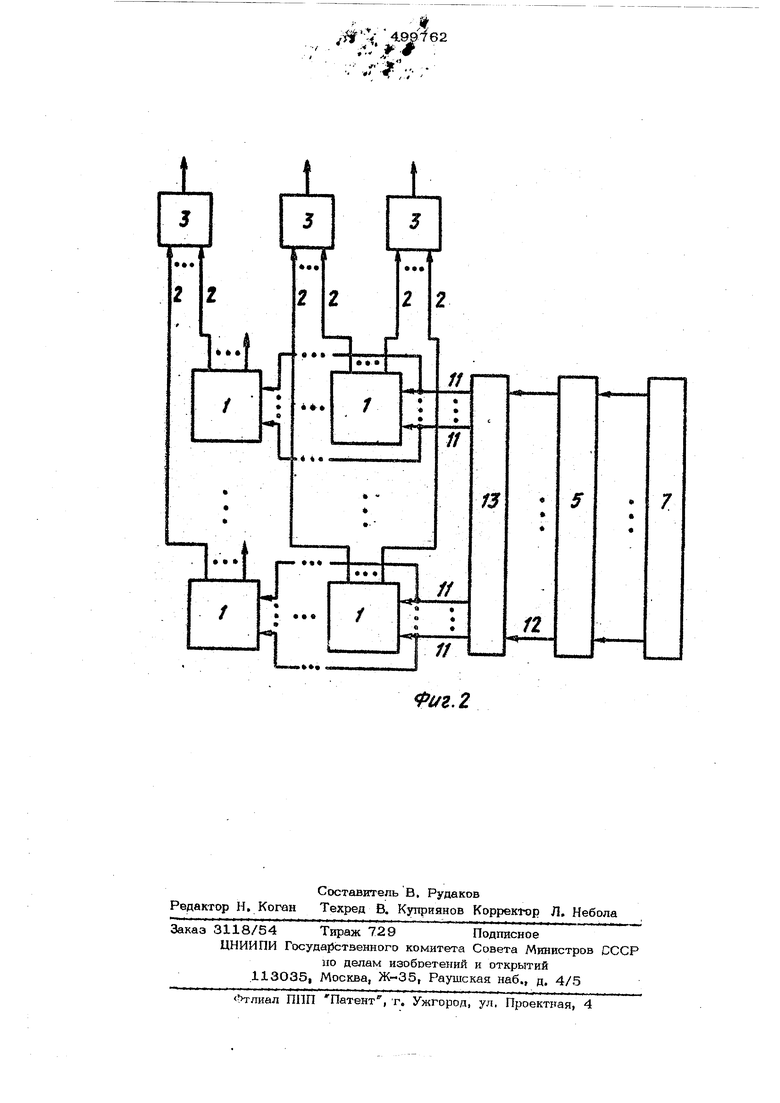

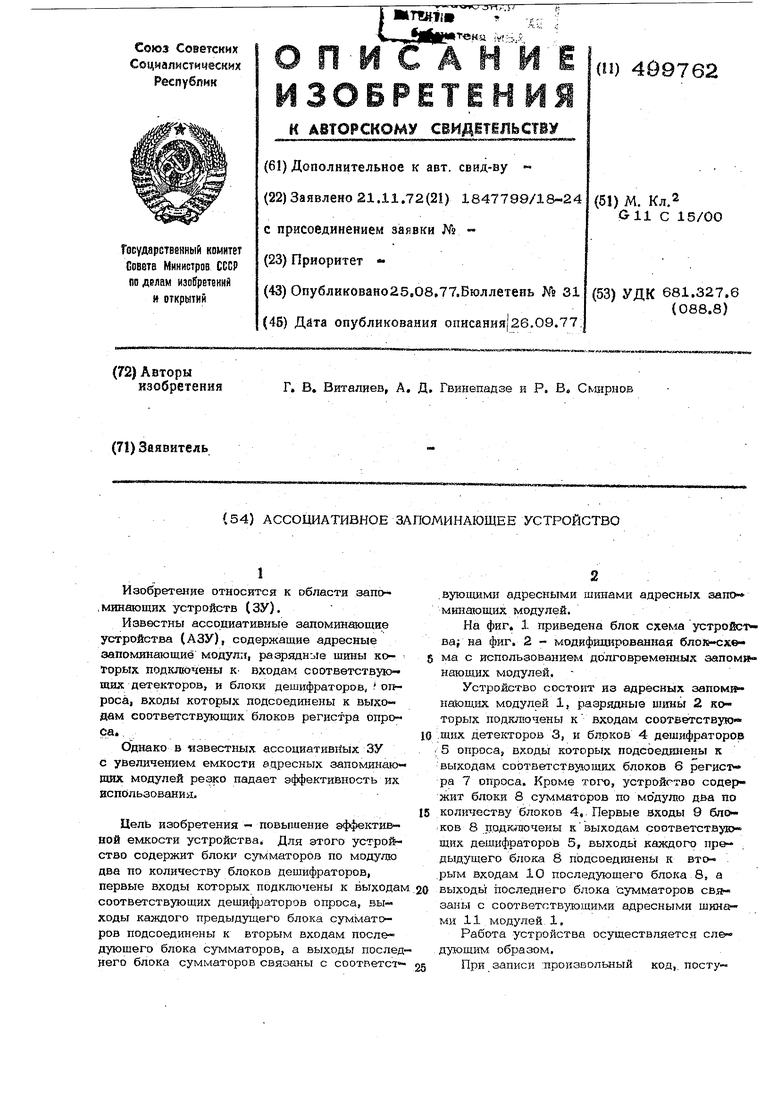

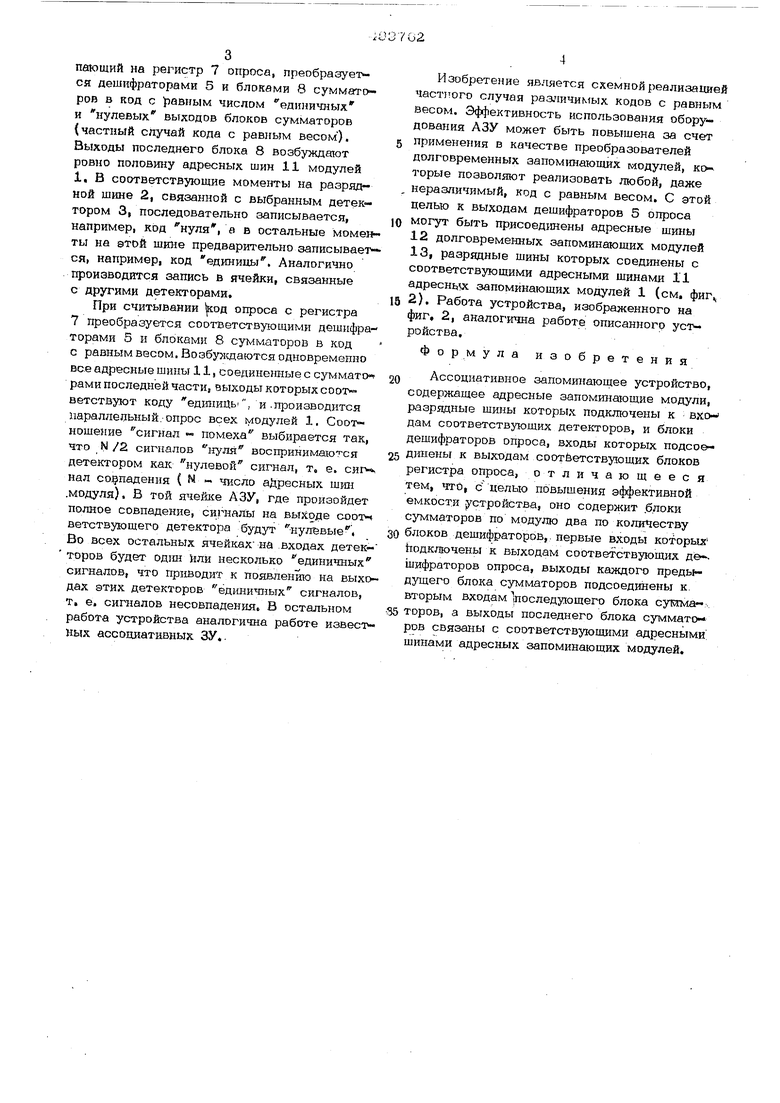

Изобретение относится к области запо , минающих устройств (ЗУ). Известны ассойиативные запоминающие Зстройства (АЗУ), содержащие адресные запоминающие модули, разрядные шины которых подключены К входам соответствую- щих детекторов, и блоки дешифраторов, f отброса, входы которых подсоединены к выхо дам соответствующих блоков регистра опро са.. .. . , Однако в известных ассоциативных ЗУ с увеличением емкости адресных заполшнающих модулей резко падает эффективность их использования. Цель изобретения - повышение эффективной емкости устройства. Для этого устройство содержит блоки сумматоров по модулю два по количеству блоков дешифраторов, первые входы которых подключены к выхода соответствующих дещифраторов опроса, выходы каждого предыдущего блока сумматоров подсоединены к вторым входам последующего блока сумматоров, а выходы послед него блока сумматоров связаны с соответст .вующими адресными шинами адресных эапо- минающих модулей.. На фиг, 1 приведена блок схема устройст ва; на фиг, 2 - модифихифованная блок-схема с использованием долговременных запоминающих модулей. Устройство состоит из адресных aanoMifнающих модулей 1, разрядные шины 2 которых подключены к входам соответствую .щих детекторов 3, и блоков 4 дещифраторов 5 опроса, входы которых подсоединены к выходам соответству1ощих блоков 6 региср ра 7 опроса. Кроме того, устройство содержит блоки 8 сумматоров по модулю два по количеству блоков 4, Первые входы 9 блоков 8 подключены квыходам соответств то щих дешифраторов 5, выходы каждого пре- . дыдущего блока 8 подсоединены к вто.рым входам 10 последующего блока.8, а выходы последнего блока сумматоров CBJJ заны с соответствующими адресными щинами 11 модулей. 1. Работа устройства осуществляется сле ДУ5ОЩИЛ1 образом. При записи произвольный код,, поступающий на регистр 7 опроса, преобразуется дешифраторами 5 и блоками 8 сумматоров в код с равным числом едиличных и нулевых выходов блоков сумматоров (частный случай кода с равным весом ). Выходы последнего блока 8 возбуждают ровно половину адресных шин 11 модулей 1, В соответствующие моменты на разрядной шине 2, связанной с выбранным детектором 3| последовательно записывается, например код нуля а в остальные моменты на этой шине предварительно записывается, например, код единицы . Аналогично производятся запись в ячейки, связанные с другими детекторами. При считывании од опроса с регистра 7 преобразуется соответствующими дешифраторами 5 и блоками 8 сумматоров в код с равным весом. Возбулшаются одновременно все адресные шины 11, соединегшые с сумматоп рами последней части, выходы которых соот- ветствуют коду едшшЦЬ, и.производится иараллеиьный.-опроо всех 1у1одулей 1. Соот ношение сигнал - помеха выбирается так, что N /2 сигналов нуля воспринимаются детектором как нулевой сигнал, т. е. сиг« нал совпадения ( N число адресных шин .модуля). В той ячейке АЗУ, где произойдет полное совпадение, сигналы на соответствуюшего детектора будут нулевые, Во всех остальных ячейках на .входах детекторов будет ОД1Ш или несколько единичных сигналов, что приводит к покозлению на выхо дах этих детекторов единичных сигналов, т. е. сигналов несовпадения. В остальном работа устройства аналогична работе извести вых ассоциативных ЗУ.. Изобретение является схемной реализацией частного случая раачичимых кодов с равным весом. Эффективность использования оборудования АЗУ может быть повышена за счет применения в качестве преобразователей долговременных запоминающих модулей, ко торые позволяют реализовать любой, даже неразличимый, код с равным весом. С этой целью к выходам дешифраторов 5 опроса могут быть присоедшены адресные шины 12 долговременных запоминающих модулей 13, разрядные шины которых соединены с соответствующими адресными шинами 11 адресньус запоминающих модулей 1 (см. фиг 2). Работа устройства, изображенного на фиг, 2, аналогична работе описанного усгройства. Формула изобретения Ассоциативное запоминающее устройство, содержащее адресные запоминающие модули, разрядные щинь которых подключены к вк.одам соответствующих детекторов, и блоки дешифраторов опроса, входы которых подсоедшгены к выходам соответствующих блоков регистра опроса, отличающееся тем, что, сцелью повышения эффективной емкости густройства, оно содержит .блоки сумматоров по модуадэ два по количеству блоков дешифраторов, первые входы которы1х подключены к выходам соответствующих д&. шифраторов опроса, выходы каждого предыдущего блока сумматоров подсоединены к. вторым входам последующего блока сутамаг-л, торов, а выходы последнего блока суммато ров связаны с соответствующими адресными шинами адресных запоминающих модулей.

J

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1972 |

|

SU493163A1 |

| Ассоциативное запоминающее устройство | 1971 |

|

SU493164A1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU604033A1 |

| Ассоциативное запоминающее устройсво | 1971 |

|

SU493165A1 |

| Ассоциативное запоминающее устройство | 1978 |

|

SU701349A1 |

| Ассоциативное запоминающее устройство | 1971 |

|

SU493162A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU310307A1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU576608A1 |

| АССОЦИАТИВНО-АДРЕСНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU336697A1 |

| Ассоциативное запоминающее устройство | 1974 |

|

SU588561A1 |

J.

,

fOMIiaffsao::«

.J

L.

...

1 , /

1/г.2

Авторы

Даты

1977-08-25—Публикация

1972-11-21—Подача