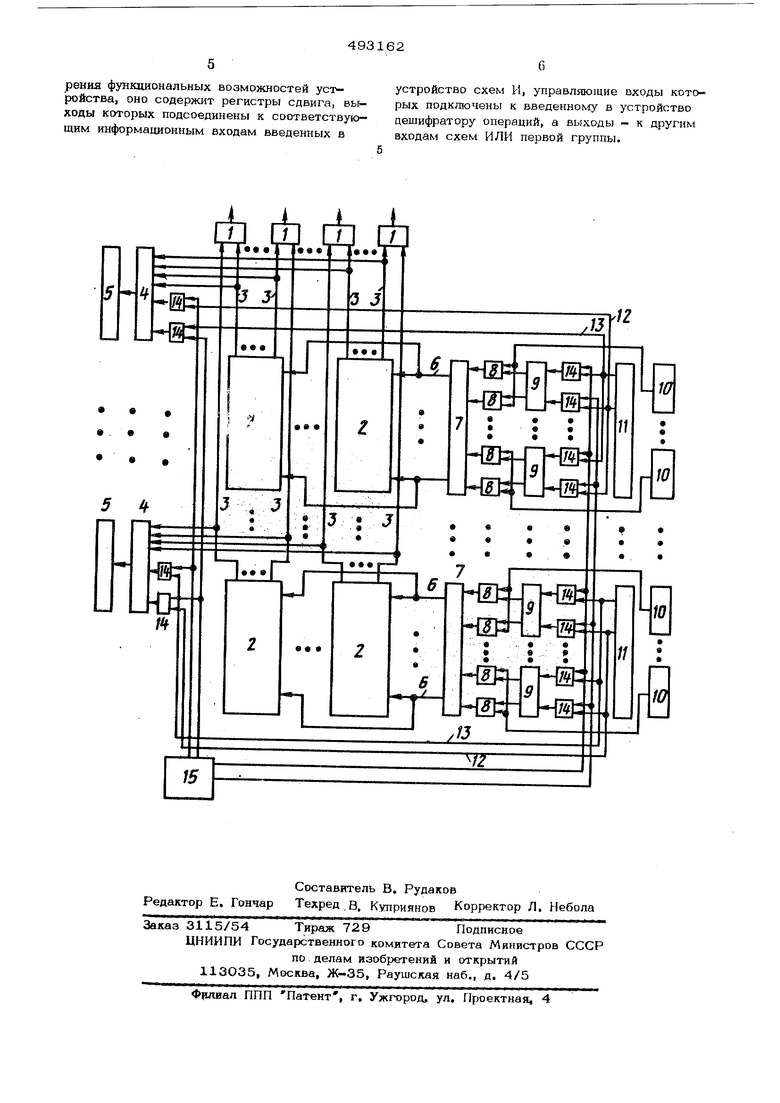

(54) АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО Аэ, суммирование по модулю два и операция равнозначности. 2,Операции логического сложения для четырех комбинаций из двух операндов в прямом и обратном коде. 3,Операции логического умножения для тех же четырех комбинаций. Операции первой группы сводятся к оп&раЦиям поразрядной выборки в прямом и обратном коде - в зависимости от типа oneрации и кода второго операнда. Рассмотрим более подробно выполнение операции сумм рования по модулю два. Подготовка первого операнда заключается в возбуждении шин 3, соединенных с детектором 1, соответствующим порядковому номеру (адресу) этого операнда. Отметим, что разрядные ишны модулей 2, соединенные с одним и тем е детектором,соответствуют номеру операнда, а адресные шины - его разрядам, причем, код этого операнда записывается в каждом модуле 2 в виде единицы на фоне нулей и единица записывается в той адресной шине, номер которой соответатбует двоичному коду записанного числа. Второй операнд поступает на регистр 11. Для повышения быстродействия регистр 11 разбит на нёоколько частей, причем количество разрядов в коде, хранящемся в .каждой такой части, с числом адресных шин модулей п связано 2 , Операция выполняется пара№К 1К Па лельно по слогам за к тактов регистра 11, Если в младщем разряде данной части регистра 11 находится нуль, то соответст вующий разряд кода первого операнда дол жен быть выбран в прямом коде. Для этого возбуждаются -все адресные шины нужного модуля с номерами, соответствующими двои ным кодам адресов, содержащих единицу в данном разряде, что достигается путем занесения кода 11...10 в соответствующую часть регистра 10 маски и кода 11...11 через схемы И 14 в соответствующую част регистра 9 опроса. Необходимые для этого схемы И 14 выбираются, с помощью деши(| ратора 15 операций. Если в младшем разряде находится код единицы, то выборка из АЗУ производится в обратном коде в соответствии с номерами кодов двоичных адресов, содержащих в данном разряде нуль. Для этого на регистр 1О маски заносится код 11...10, а на ре гистр 9 опроса - код 00...00. В следующем такте код на регистрах 5, 1О и 11 сдвига . ся на разряд, в регистре 1б циклически, и операция выполняется над вторыми разрядами слогов первого и второго операндов и т, д. Операция равнозначности выполняется подобным же образом, з« исключением того что наличие ед{шицы в данном разряде регистра 11 требует выборки из АЗУ в коде, а нуля - в обратном. Операция инвертирования эквивалента операции,осумм рования по модулю два с кодом второго операнда 11..1. Занесение на регистр 11 кода 00...О позболяет осуществить выбо{ ку из АЗУ в прямом коде. Группа операций логического суммирования выподаяется следующим ооразом. Если в данном разряде регистра 11 находится единица (или нуль для операций с о&ратным кодом второго операнда), то этот код передается через соответствующие схемы И 14 и схемы ИЛИ 4 на вход одноименной части выходного регистра 5. В противном случ1ае производится выборка из АЗУ в прямом или обратном коде, в соответствии с тем, в прямом или обратном коде участвует в операции первый операнд. Группа операций логического умножения требует обращения к АЗУ при наличии кода единицы в данном разряде части регис- ра 11 (или нуля для операций в обратном коде). Нулевой код передается непосредст;- венно на выходной регистр 5. Таким образом, для выполнения в данном АЗУ любой логической операции достаточно поразрядных операций: выборка в прямом коде, выборка в обратном коде (инвертирование) и передача кода операнда на выходной регистр 5. Если второй операнд также находится в АЗУ, то перед выполнением основной оп&рации он должен быть вьтбран на регистр 11. Результат операции может быть пер&дан за один такт с выходного регистра 5 на регистр 11 или записан в АЗУ по любому адресу. В асинхронном режиме операции логичеокого сложения и умножения могут быть уокорены примерно вдвое за счет того, что, в среднем, в половине случаев не требуется обращений к АЗУ, Используя в АЗУ полупроводниковые модули с к-1-4, можно получить результат любой логической операции, в среднем, за один-три такта обращения к АЗУ. Формула изобретения Ассоциативное запоминающее устройство, содержащее адресные запоминающие модули, разрядные щины которых подключены к соответствующим детекторам и одним входам схем ИЛИ первой группы, а адресные шины - к выходам дешифраторов опроса, входы которых подсоединрнь к соответствующим выходам схом ИЛИ второй группы, входы которых подключены к выходам регистра опроса и регистра маски, о т л tJчающееся тем, что, с целью расширения функциональных возмозкностей устройства, оно содержит регистры сдвига, выходы которых подсоединены к соответствую- щим информационным входам введенных в устройство схем И, управляющие входы которых подключены к введенному в устройство дешифратору операций, а выходы - к другим входам схем ИЛИ первой группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1978 |

|

SU701349A1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU604033A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Ассоциативное запоминающее устройство | 1974 |

|

SU588561A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Логическое запоминающее устройство | 1980 |

|

SU947910A2 |

| Ассоциативное запоминающее устройство | 1971 |

|

SU493164A1 |

Ж

Авторы

Даты

1977-08-25—Публикация

1971-11-22—Подача