1

Известно логическое запоминающее устройство, содержащее накопитель и логическую матрицу на магнитных сердечниках, прошитые двутля системами координатных шин записи и воспроизведения и системой диаго нальных шин, реверсивный дёш/.фратор адреса, выходы которого подключены к накопителю, усилители воспроизведения, входы которых под ключены к накопителю, а выходи к регистру регенерации, выходы которого подключены через формирователи к соответствующим входам накопителя.

С целью повышения надежности и упрощения устройства координатные шины воспроизведения логической матрицы включены последовательно, с разрядными шинами накопителя и соединены со входами усилителей воспроизведения, а координатные шины записи подключены непосредственно к выходам формироI вателей регистра регенерации, ди-

агональные шины. - к дополнительным выходам дешифратора адреса накопителя. ,

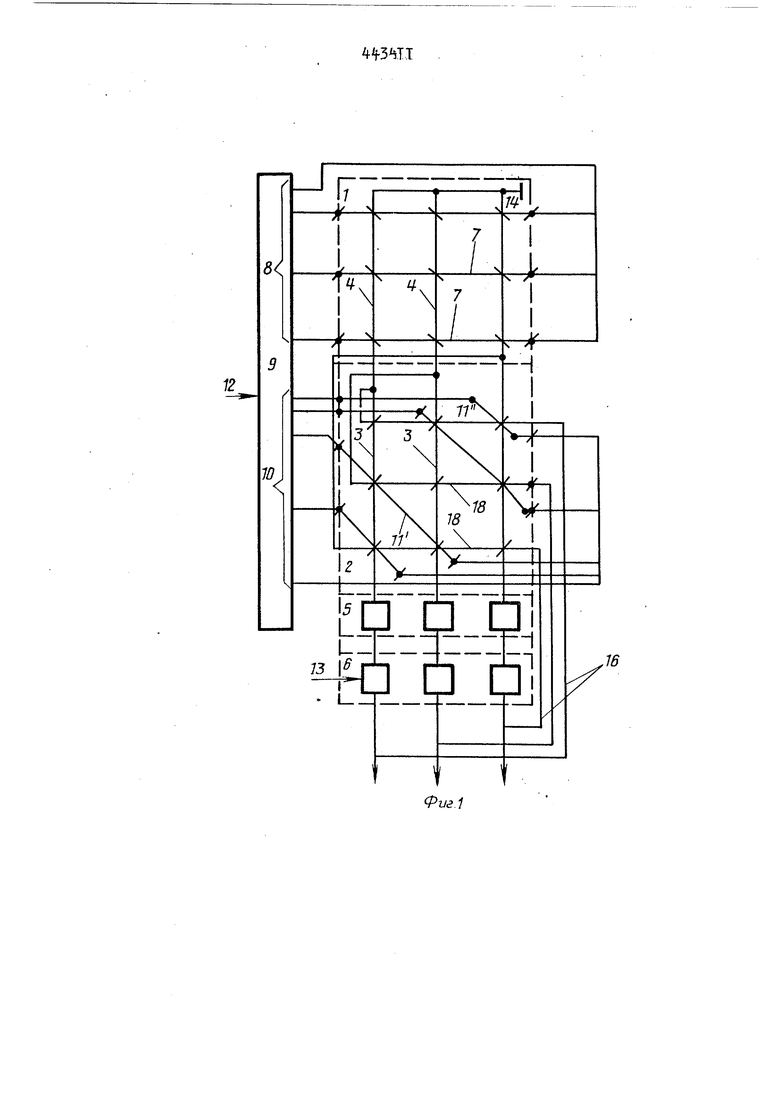

На фиг. I изображена структурная схема предлагаемого устройства; на фиг.2 - схема разрядной цепи одного разряда.

Логическое запомина ощее устройство (фиг.1) содержит накопитель I и логическую матрицу 2 на магнитных сердечниках, координатные шины 3 воспроиздедения которой включены последовательно с шинами 4 воспроизведения накопителя I и

соединены со входами усилителей 5 воспроизведения. Выходы последних подсоединены ко входам регистра регенерации 6.

Адресные шины 7 накопителя I

подключены к выходам 8 реверсивного деши(|)ратора 9 адреса, выходы 10 которого соединены с диагональными шинами II логической матрицы 2 (диагональные шины II, расположенные ниже главной диагонали. предназначены для сдвига влево, диагональные шины II, расположенные выше главной диагонали, предназначены для сдвига вправо). Главная диагональ матрицы 2 диагональной шины не имеет. Реверсивный даDiJ шины не ишсох. шитратор 9 адреса и регистр 6 реге , „д оеганерации соединены с устройством управления по cвязя 1 12 и 13 COOTTTTirxnTnTPHWH ни о JJJi-- - SSSbeHHO Разрядная цепь накопи,„„ р,,,,зпялняя цепь накопиветственни. га i по извест- ветственни. i ciojjjvj,--- -- теля (.:иг.2 выполнена по известной мостовой схеме. „ „ Два плеча моста, общей точкой 14 подключенные к одному полюсу источника питания, содержат разрядные шины 4 накопителя I ж выравнив вающие резисторы 15. Два других плеча общей точкой 16 подключены к форг.ярователя регистра 6 регенерации. Одно из этих плеч содержит диод Х7, а другое - диод и uimv JJ& записи логической маттзицы 2. Между анодами диодов 17 в диаго нальную цепь моста включена коорди натнатная шина 3 воспроизведения матрицы 2, соединенная со входом усилителя 5 воспроизведения. ь предлагаемом устройстве во, время передачи ин;1:ормации из накопителя I (фиг.1) в логическую iViaTрицу 2 и обратно производится сдвиг двоичного слова X на It-разря дов влево или вправо при условии, что k-i м, где м - количество разрядов в слове X. Сдвиг информации выполняется за четыре такта. В первом такте импульсогл тока -IflC выхода 8 по адресной шине 7, выбранной дешифратором 9, считывается ячейка накопителя I. Если в считанном слове X единица содерлсится только в t-ом разряде, то Э.Д.С., наводимая на разрядном шине 4, пост атает на вход усилител 5 БОСпроизБ.еяения разряда, с выхода которого осуществляется запись единицы в i -т разряд рбгистра 6 регенерации. Во втрром такте для сдвига слова на разрядов влево дешифратором 9 с выхода 10 возбтадается диагональная шина II, расположенная на фиг.1 ниже главной диагонали матрицы 2, и считываются формирователи регистра 6 регенерации. Импульсы тока в разрядных шинах 18 и 4 I -го разряда и Й-ой . диагональной шине 1г имеют величи ну +0,5 lo- Импульсы тока в других разрядных шинах для рассматриваемо го примера отсутствуют, так как во всех разрядах слова X, кроме t-ro, всех иа.ЗиЯДс1-Л. л, rvjjuwio «- i VX J находятся нули. В результате сов It ,.,11 и . j ото г тз падения полутоков в один из сердеч ИКОВ лигической матрицы 2, находящейся на пересечении возбуждещых ин IIи 18, записывается едйнкца. Все остальные сердечники матрицы 2 стаются в нулевом состоянии. В третьем такте осуществляетя считывание сердечников логической матрицы 2, для чего в шине II, возбуждавшейся во втором такте, форj-i WW J их,ж,ч,. .- --,.. - -,-,. J мируется импульс тока, величина оторого равна -Jo , при этом;, кптпппгп павка -7/, . пои этом сердечник,ншлагниченный во втором такте в единицу, перемагничиваатся в ноль. На шинах, пронизывающих сердечник, наводится Э.Д.С., при чем Э.Д.С., наведенная на шине 3 логической матрицы 2, поступает на вход усилителя воспроизведения ( i + K )-го разряда и производит запись единицы в (Ж)-й разряд регистра6 регенерации, а э.д.с., :наведенная на шине 18, включенной в разрядную цепь L -го разряда (фиг.), не поступает на вход соответствующего усилителя 5 во спроизведения, так как в цепи действия э.д.с. имеются два встречно включенных диода 17. В четвертом такте производится считывание формирователей 6 регистра регенерации (фигЛ) и фюрмирование тока записи в 7 накопителя I, как и при обычном МОЗУ. Шпульсы токов на выходах регистра 6 регенерации и на выходе 8 дешиф)ратора 9 имеют велргчину +0,51 о . Совпадением токов считывается слово. которое содержит единицу в ( разряде, записывается в ячейку накопителя I. Сдвиг вправо выполняется аналогично, шолько при этом возбуждается я-я шина IF, располсненная на фиг.1, выше главной диагонали логической матрицы 2. При использовании МОЗУ систе1мы 2,5 Д с выделенными шинами воспроизведения координатные шины 3 воспроизведения лЬгической матрицы 2 включаются последовательно с шинами 4 воспроизведения накопителя I, координатные шины 18 логической матрицы 2 подключаются ко входам формирователей разрядных токов записи до разветвления по адресно-разрядршм 1шнам, диагональные II подсоединяются к дополнительным выходам 10 дешифратора адреса 9. В режиме сдвига в такт считывания /1-й и 3-й такты/ в даюифрато-« -- /- - -..,-.«/ - ..-. тгп Tfi-UT-T тгатлг гпт: тзоглт: пп mrmr и гж ре должны действовать полутоки (-0,51о} в отличии от полного 1Ола

. -lo } в режшле считывания ячейки МОЗУ системы 2Д.

ПРадЖТ ИЗОБРЕТЕНИЯ

Логическое запоминающее устройство, содержащее накопитель и логическую матрицу на магнитных сердечня1;ах, прошитые двумя систеглшли координатных шин записи и вое

пролзвед.ения и системой диагональных шин, реверсивный дешифратор адреса, выходы которого подключены к накопителю, усилители воепроизведения, входы которых подключены к на копител1о, а выходы - к регистру регенерации, выходы которого ;:одключены через форми- . рователи к соответствующим входам накопителя, отличающееся тем, что, с целью упрощения ycTpoiicTsa и повышения его надежности, координатные шины воспроизведения логической матрицы включены последовательно с разрядными шинами накопителя и соединены со входами усилителей воспроизведения, а координа тные шины записи подключены непосредственно к выходам форми- рователей регистра регенерации, диагональные шины - к дополнительным выходам дешифратора адреса накопителя.

i;

.

ъ

/

/

/ 7

Ч

.

/

U

75

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| ВЫЧИСЛИТЕЛЬНО ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU337824A1 |

| ЦИФРОВОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА ПОЛНОТОЧНОМНАКОПИТЕЛЕ | 1971 |

|

SU289514A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| Управляющий автомат цифрового устройства числового управления | 1972 |

|

SU507153A1 |

| Накопитель магнитного оперативного запоминающего устройства | 1974 |

|

SU498647A1 |

| Цифровое устройство числового программного управления | 1971 |

|

SU441858A1 |

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯДВУХ ЧИСЕЛ | 1970 |

|

SU268498A1 |

| Устройство для параллельного суммирования двух чисел | 1974 |

|

SU523452A1 |

Авторы

Даты

1974-09-15—Публикация

1971-11-05—Подача