(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

входы iKOMiMyiaTopa подсоеди.неиы к выходам блока сравнения кодов, пятые входы коммутатора соединены с выходами накопителя, вторые входы .которого подключены .к одним из выходов Коммутатора, другие выходы которого соединены со входами усилителей оч1;тывания, третьи входы на-копителя подключены iKO вторы.м выходам дополнительного селектирующего блока, одни из входов -которого соединены с .выходами формирователей числового тока записи, другие входы дополнительного селектирующего блока подсоединены к третьим выходам селектирующего блока, четвертый выход селектирующего блока ч третий выход дололнительного селектирующего блока соединены со входами блочка сравнения кодов.

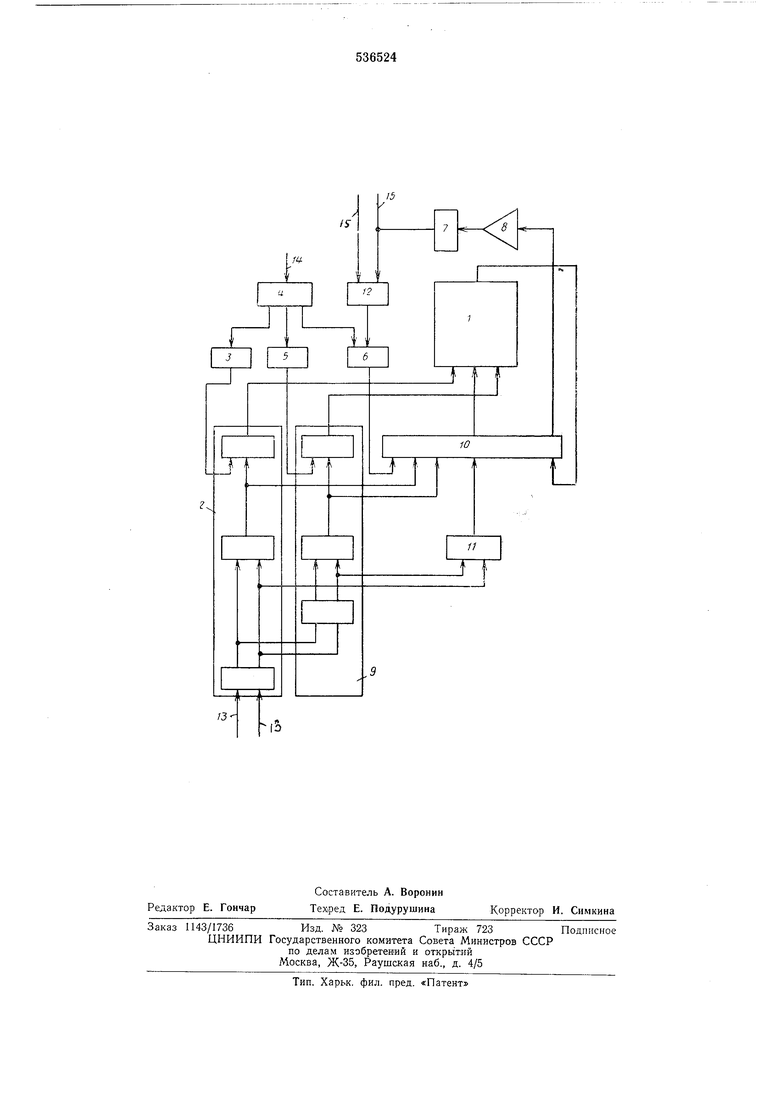

На чертеже представлена функциональная схема запоминающего устройства.

В запоминающее устройство входят накопитель /, селектирующий блок 2, формирователи 3 толса считы вания, которые своими .выхо дами соединены с входами селектирующего блока 2; блок управлепия 4, формирователи числового то«а записи 5; фор,мирователи разрядного TOiKa записи (J; регистр числа считывания 7j усилители считывания 8, дололнительный селектирующий бло:к 9, коммутатор 10, блок сравнения кодов 11, регистр ч,исла записи 12, шины адреса 13, шины управления 14, шины 15 числа.

Запоминающее устройство работает еледующим образом.

По шинам адреса 13 в регистр адреса считывания селектирующего блока 2 заносится 1К01Д адреса лервой ячейки, из которой необходимо выбрать информацию, а в блок управления 4 по шинам управления 14 поступает синхроимпульс «Пуск запоминающего устройства. В дешифраторе адреса происходит раздельная дешифрация кодов координатных проводов X и координатных проводов F. Адресные входы матрицы выборки считывания селектирующего блока 2 и адресные 1входы считывания коммутатора 10, определяющие выбранную ячейку, окажутся .выбранными. Блок управления 4 возбуждает формирователи 3 то,ка считывания и полный так считывания поступает в числовой провод, который (Выбран матрицей выборки считывания селектирующего блока 2.

При первом обращении к запоминающему устройству координатные провода X, пронизывающие запоминающие элементы первой ячейки и Пересекающие первый выбранный число вой Провод, окажутся подсоединенными коммутатором 10 к входам усилителей считывания 8, считанные сипналы возбудят усилители S и в регистр числа считы:ва.ния 7 постуЛИТ считанная информация. По шинам 15 числа и;н|формадия выводится из заломинающего уст|ройст1ва. Кроме того, считанная информация поступает и в регистр числа залиси 12 для регенерации в лервую ячейку памяти. Адрес первой лередается из регистра числа считыва.ния селектирующего блока 2 в регистр числа записи дополнительного селектирующего блока 9, и одноврсмекно 3 регистр адреса считывания селектирующего блока 2 по шинам адреса 13 заносится адрес второй ячейки, из которой необходимо выбрать информацию.

Снова, как и при первом обращении, ло шинам управления 14 поступает синхроимпульс «Пуск запоминающего устройства и в числовой провод второй ячейки поступает полный ток считывания, от .которого переключатся запоминающие элементы .на этом числовом проводе.

О:Дновременно дололнительный селектирующий блок выберет первый числовой провод и нолутО|К записи поступит от возбужденных формирователей тока за.писи 5 через селектирующий блок 9 iB первый числовой провод в обратном направлении по сравнению с первым обращением к запоминающему устройству. Полуток записи еще не .переключит запоминающие элементы и поэтому по координатным проводам X или У пронизывающие заломин.ающие элементы первого числового провода также подаются полутоки записи информащио.нной единицы. При этом регистр числа записи 12 возбуждает только формирователи то.ка записи, соответствующие разрядам накопителя 1, в которые необходимо записать (регенерировать) информационную единицу.

Блок сравнения кодов // сравнивает части адресных кодо.в, определяющие координатные провода X первой и второй ячеек и в случае их эквивалентности переключает коммутатор 10 на координатные провода Y.

Коммутатор 10 подключает координатные провода К, пронизывающие запоминающие элементы второй ячейки, к входам усилителей считывания 5, а координатные провода У, пронизывающие запоминающие элементы первой ячейки, - к выходам формирователей разрядного то:ка записи 6. При этом информация из второй ячейки поступает через усилитель считывания 8 Б регистр числа считывания 7, а в координатные провода У, пронизывающие 3 аломинающие элементы .первой ячейки, поступят лолутоки записи и произойдет регенерация информации в первую ячейку. Запись новой информации в ячейку паМяти осуществляется в два цикла: в первом цикле вьшолняется Считывание из заданной ячейки с лотерей информации и занесение но1вой в регистр числа ааписи 12 ло входным шинам числа 15, во втором цикле произойдет запись новой ил|ф.ормации в ячейку и считывание информ.ации со следующей, как олисано выше.

По сравнению с исполнением запоминающих устройств ПО системам 2Д, 2/2Д и ЗД предлагаемое решение повышает быстродействие запоминающих устройств, выполненных

на магнитных элементах, в два раза, а если учесть, что быстродействие электроино-вычислительных машин, ка.к правило, определяется быстродействием ЗУ, то предлагаемое реше,ние При.ведет к значительному повышению быстродействия ЭВМ в целом.

Формула изобретения

Заломинающее устройство, содержаш,ее на|колитель, первый вход которого подключен к первому выходу селектИ(руюш.его блока, одни входы которого соединены с шинами адреса, другие входы селектирующего блока подсоединены к выходам формирователей TOiKa считывания, входы которых соединены с первым выходом блОКа управления, второй выход .которого подключен ко входам форлшрователей числового тожа записи, третий выход блока управления соединен с одними входами формирователей разрядного Т0|ка залиси, регистр числа считывания, входы которого подключены .к выходам усилителей считывания, шины управления, соединенные со входами бло.ка управления, шины числа, соединенные с выходами регистра числа считывания, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены дополнительный селектирующий блок, (Коммутатор, блок сравнения кодов и регистр числа записи, входы которого подключены к шинам числа, выходы регистра

числа записи соединены с другими входами формирователей разрядного тока записи, выходы которых подсоединены к первым входам коммутатора, вторые и третьи входы которого соединены со вторыми и первыми выходами селектирующего и дополнительного селектирующего блоков соответственно, четвертые входы коммутатора подсоединены к выходам блО|Ка сра.внения .кодов, пятые .входы коммутатора соединены с выходами накопителя, вторые входы которого подключены к одним из выходов коммутатора, другие выходы которого соединены со входами усилителей считывания, третьи входы накопителя подключены ко вторым выходам дополнительного селектирующего блока, одни из входов которого соединены с выходами формирователей числового то.ка записи, другие входы дополнительного селектирующего блока подсоединены к третьим выходам селектирующего блока, четвертый выход селектирующего блока и третий выход дополнительного селектирующего блока соединены со вхо.дами блока сравнения кодов.

Источники информации, принятые во внимание при экспе|ртизе изобретения:

1. Катцан Г. «Вычислительные мащи.ны системы 370, М,, «Мир, 1974 г., стр. 23.

2. Крайзер Л. П. «Устройство для хранения дискретной информации. Л., «Энергия, 1969 г., стр. 123.

3

13

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения записи информации в память ЭВМ | 1983 |

|

SU1153340A1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| Оперативное запоминающее устройство | 1974 |

|

SU495712A1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Магнитное оперативное запоминающее устройство | 1976 |

|

SU647742A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Логическое запоминающее устройство | 1971 |

|

SU443411A1 |

| Накопитель магнитного оперативного запоминающего устройства | 1974 |

|

SU498647A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Оперативное запоминающее устройство с самоконтролем | 1974 |

|

SU562007A1 |

Авторы

Даты

1976-11-25—Публикация

1974-02-26—Подача