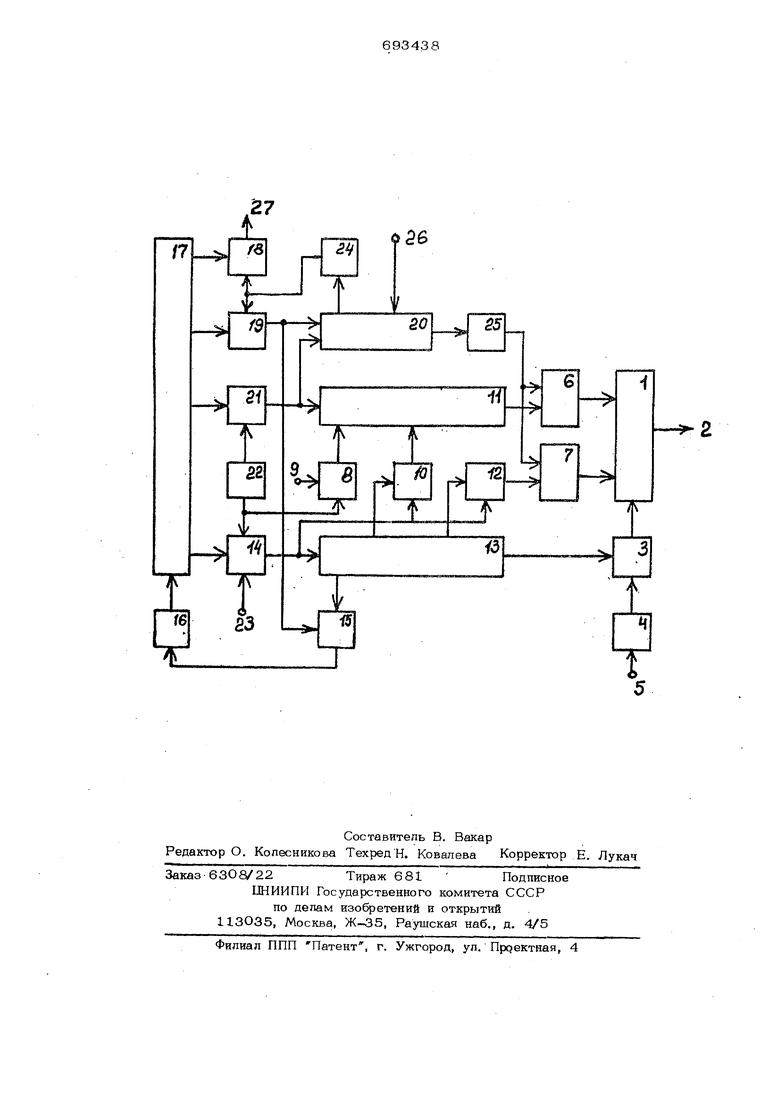

первый и второй входы которого соответственно соединены с выходами перво.го и второго элементов И, регистр ад реса, выход которого соединен со входом дешифратора адреса, регистр чиспа, выход которого соединен с первым входом формирователя разрядных токов записи, третий элемент И, выход которого соединен со вторым входом формирователя адресных токов записи, первый вход которого .подключен .к выходу детиифратора адреса и генератор импульсов 2. Недостатком известного ЗУ является нестабильность параметров йькодного сигЬапа с накопителя при , считывании информации, что снижает надежностгз работ ы ЗУ. Цель изобретения - повышение надежности устройства путем компенсации частичных разрушений информации. Для достижения поставленной цепи устройство содержит второй элемент ИЛ четвертый, пятый, шестой и седьмой элементы. И, счетчик циклов, дешифратор циклов, блок анализа адреса, счетчик тактов, при этом соответствующие выходы дешифратора циклов соединены с первыми входами четвертого, пятого, шестого и седьмого элементов И, а вход - с выходом счетчика циклов, вхо которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с первым выходом счетчика . тактов, а второй - с первым выходом шестого элемента И, второй выход счет чика тактов соединён со вторымвходом формирователя разрядных токов записи, третий и четвертый соответственно с первыми входами второго и третьего элементов И,, вторые входы со динены с выходом четвёртого элемента И, соединенного со входом счетчики . тактов, первый выход генератора импул сов соединен со вторым входом седьмого элемента И, а второй выход - со вторым входом четвертого элемента И входом; первого элемента И, выход седь мого элемента И по1дключен к третьему входу первого элемента ИЛИ, а первый выход шестого, элемента И соединен с первым входом регистра адреса, второй . вход которого соединен с выходом седьмого элемента И, вход блока анализа; соединен со вторым выходом ре- ; гистра адреса, а выход подключен ко вторым входам nsi-jro и шестого эле ментов И. На чертеже представлена блок-схема редлагаемого устройства. Запоминаю- ш.ее-устройство содержит накопитель 1 выходные числовые шины 2, формиро- , ватель 3 разрядных токов записи и регистр 4 числа со входными числовыми шинами 5, формирователь б адресных токов считывания и формирователь 7 адресных токов записи, первый элемент И 8, шина чтение 9, второй элемент И 10, первый элемент ИЛИ 11, третий элемент И 12, счетчик 13 тактов ,четвертый элемент И 14, второй элемент ИЛИ 15, счетчик 16 -циклов, дешифра- тор 17 циклов, пятый элемент И 18, шестой элемент И 19, регистр 2О адреса, седьмой элемент И 21, генератор импульсов 22, шина 23 записи, блок 24 анализа адреса, дешифратор 25 адреса,адресные шины 26. Синхроимпульс с генератора импульсов 22 через первый элемент И 8 при Наличии на шине чтения 9 разрешаю- шегр потенциала и первый элемент ИЛИ 11 поступает на вход выбранного формирователя 6 адресного тока считывания. В результате по избранной координате накопителя 1 протекает ток считывания и на выходных числовых шинах 2 вырабатывается код считанного числа. В режиме записи информации по :. . адресным шинам 26 в регистр 20 адреса поступает код адреса, а по входным числовым шинам 5 в регистр 4 числа - код числа. На управляюшей шине запись 23 в этом режиме имеется разрешающий потенциал. Счетчик 16 циклов находится в исходном состоянии, поэтому на выходе дешифратора 17 существуют потенциалы, открывающие четвертый 14 и шестой 19 элементы И, и закрывающие пятый 18 и седьмой 21 элементы И. Синхроимпульсы с генератора 22 через четвертый элемент И 14 поступают на входы счетчика 13 тактов, второй элемент И 10 и третий элемент И 12. Вторые входы второго и третьего элементов И 10 и 12 управляются счетчиком 13 таким образом, что в течение определенного времени поочередно синхроимпульс проходит через один из этих элементов И. В результате этого поочередно срабатывают формирователи адресных 5го1юв записи и формирователи 6 адресных токов считывания, т.е. в из бранной координатной шине накопителя че редуЮтся импуттьс тока поотивополож56ной полярности. При этом от счетчика 1 на формирователи 3 разрядных токов за писи поступает разрешающий потенциал в pefЭyльтaтe чего по разрядным шинам накопителя 1 протекают токи, направлепке каждого на которых соответствует значению соответствующего разряда регистра 4 числа. Указанные процессы обеспечивают необходимые изменения магнитных состояний запоминающих эпе ментов, т.е. запись информации в течение некоторого промежутка времени, вели чина которого зависит от физических свой запоминающих элементов. Заданное время отсчит ывается счетчиком 13 тактов который при достижении определенной кодовой комбинации запрещает работу разрядных формирователей 3 токов записи и запрещает прохож дение синхроимпульсов через третий элемент И 12 на запуск формировате. лей 7 адресных токов записи. Последующий промежуток времени, который TaitoKe;- ограничивается достижением определенной кодовой комбинации в счетчике 13 тактов характеризуется протеканием по избранной координате нескольких токов считывания. Это необходимо для устранения известного явления, заключающегося в том, что при нескольких обращениях за информацией сразу же после записи сигналов на выходе накопителя амплитуда сигнала на порядок больще и с более, пологим фрон том по сравнению с нормализованным сигналом, который образуется после воз действия на избранную координату нескольких токов считывания. Вследствие этого несмотря на значительную амплйтуд из-за полого фронта при жестком полозкении строба, ненормализованные выходные и сигналы с накопителя могут быть неправильно восприняты усилителями считывания. По окончании процесса нормализации счетчик 13 вырабатывает запрещающий потенциал на второй элемент И Ю и разовый сигнал, поступающий через второй элемент ИЛИ 15 на вход сЧетчика 16 циклов. При изменении состояния счетчика 16 с помощью дешифратора 17 вырабатывается запрещакялий потенциал на вход четвертого элемента И 14 и разрешающие потенциалы на входы пятого и шестого элементов И 18 и 19. В результате синхроимпульсы от генератора 22 через седьмой элемент И 21 поступают на счетный вход регистра 2086адреса и через первый элемент ИЛИ 1J на запуск формирователей 6 адресных токов считывания. Таким образом обеспечивается режим, при котором ток считывания последовательно протекает по координатным шинам накопителя 1 в соответствии с перебором кодов на регистре 20 адреса, работающем в счетном режиме. При выходе из зоны массива адресов накопителя 1, охваченных единой разрядной шиной записи, блок 24 анализа адреса вырабатывает сигнал, осуществляющий через шестой элемент И 19 сброс старших разрядов регистра 20 адреса с целью возврата к началу рабочего массива адресов. Этим же сигналом увеличивается на единицу через второй элемент ИЛИ 15 содержимое счетчика 16 циклов. В следующем цикле зсе адреса массивабудут подвергнуты воздействию токов считывания. После выполнения заданного количества циклов с дешифратора 17 поступают запрещающие потенциалы на шестой и седьмой элементы И 19 и 21. Пятый элемент И 18 будет открыт и через него сигнал с блока 24 анализа адреса поступит в управляющую шину конец записи 27, произойдет сброс ражима записи. К этому моменту времени все неизбранные адреса, имеющие с избранным единую разрядную обмотку записи будут подвергнуты неоднократному воздействию токов считывания что частично компенсирует разрушений, произведенные в них разрядными токами в процессе записи. .., Предлагаемое запоминающее устроство без разрушения информации отличается от известных устройств типа 2Д многоотврестных ферритовых элементах стабильностью параметров выходных сигналов с накопителя в режиме считывания информации. Это-дает возможность применить более простые и надежные схемотехнические решения например, стабильность временных параметров выходного сигнала позволяет обеспечить надежн5гю работу устройства при фиксированном во времени положении сигнала стррбирования усилителей считывания. Стаби.лиэация амплитуды выходного сигнала исключает забивание усилителей большим сигналом, , ограничивающее быстродействие устройства, и, вместе с этим, Ловышает нижний уровень амплитуды выходного сигнала, что приводит к повышению отношения полезного сигнапа к помехе. Таким образом использование предлагаемого изобретения обеспо .чивает более надежную работу запоминаю щего устройства. Формула изобретения Запоминающее устройство системы 2 Д с неразрушающим считыванием информации на многоотверстных ферритовых элементах, содержащее накопитель, первый бход которого соединен с выходом формирователя разрядных токов записи, второй вход с выходом формирователя адресных токов записи, а. третий - с выходом формирователя адресных токов считывания, первый вход которого соединен с вь1хЬдом дешифратора адреса, а второй - с выходом первого элемента ИЛИ, первый и второй входы которого . соответственно соединены с выходами первого и вторЬго элементов И, регистр адреса, выход которого соединен со входом дешифратора адреса, регистр чйс ла, выход которого соединен с первым входом формирователя разрядных токов записи, третий элемент И, выход которо го соединен со вторым входом формирова теля адресных токов записи, первый вхо котрррго подключен к выводу дешис)ратора. ацрЪса и генератор импульсов, отличающееся тем, что, с целью повышения надежности устройства путем .компенсации частичных разрушений информации, онр содержит второй элемент ИЛИ, четвертый, пятый, шестой и седьмой элементы И, счетчик циклов, пеши( циклов, блок анализа адреса, счетчик тактов, при этом соответствующие выходы дешифратора циклов соедине ны с первыми входами четвертого пятого, шестого и седьмого элементов И, а. вход - с выходом счетчика циклов, вхоп которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с первым выходом счетчика тактов, а второй - с первым выходом шестого элемента И, второй выход счет чика тактов соединен со вторым входом формирователя разрядных токов записи, третий и четвертый соответственно с первыми входами второго и третьего элементов И, вторые входы которых соедш1ены с выходом четвертого элемента И, соединенного со входом счетчика тактов, .первый выход генератора импульсов, соединен со вторым входом седьмого элемента И, а второй выход - со вторым входом Четвертого элемента И и входом первого элемента И, выход седьмого элемента И подключен к третьему входу первого элемента ИЛИ, а первый выход шестого элемента И соединен с первым входом регистра адреса, второй вход которого соединен с выходом седьмого элемента И, вход блока анализа адреса соединен со вторым вьрсодом регистра адреса, а выход подключен ко вторым входам пятого и шестого элементов И. Источники информации, принятыево внимание при экспертизе 1.Климов И. И. и др. Полупостоянное запоминающее устройство на тороидальных магнитных сердечниках с диаметральными отверстиями. Вопросы радиоэлектронники, сер. ЭВТ, 1970. вып. 5-6. 2.Генкин В. Л. Запоминающее устгройство на транс(|люксррах с записью информации полными токами. Сб. Запоминающие устройства,Тонкие магнитные пленки. Наука, 1969.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство типа 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1979 |

|

SU773731A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Запоминающее устройство со считыванием без разрушения информации | 1979 |

|

SU773724A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1100640A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

Авторы

Даты

1979-10-25—Публикация

1977-06-20—Подача