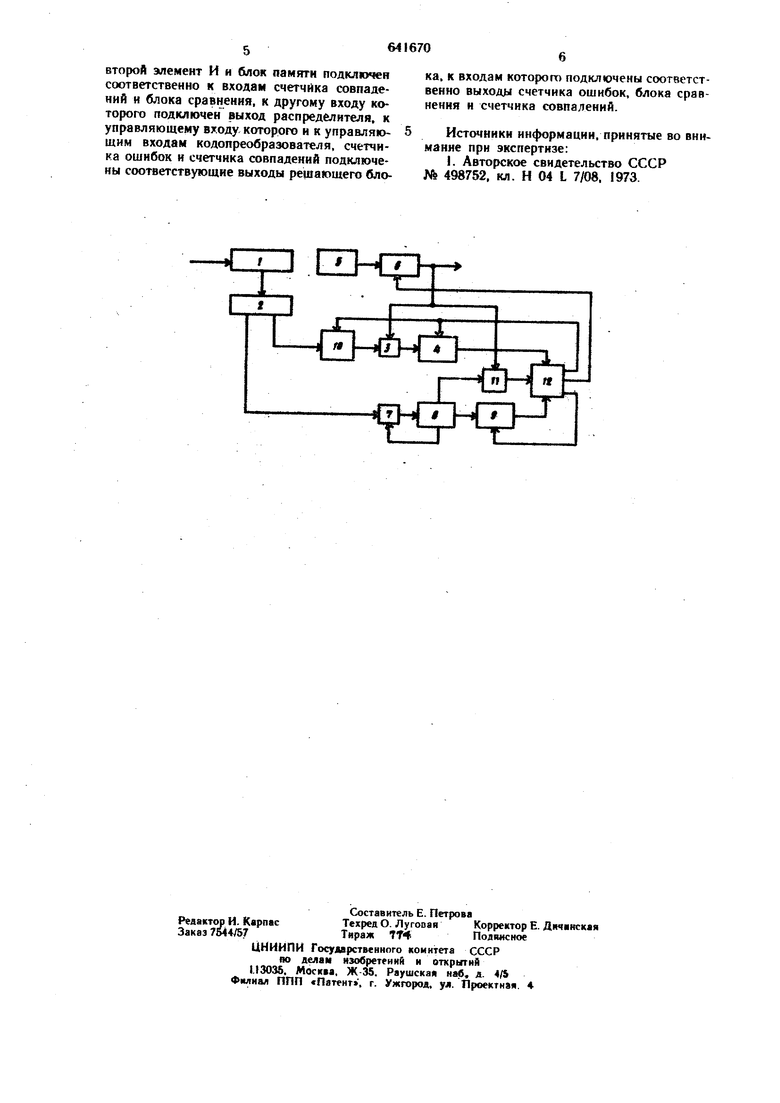

и счетчик 4 ошибок, последовательно соединенные генератор 5 тактовых импульсов и распределитель 6, выход которого подключен к первому входу первого элемента И 3, а также второй элемент И 7, к одному из входов которого подключен выход блока памяти 8, и счетчик 9 совпадений. Устройство содержит также кодопреобразователь 10. блок сравнения И и решающий блок 12, при этом кодопреобразователь 10 включен между первым выходом дешифратора 2 и вторым входом первого элемента И 3, а второй выход дешифратора 2 через последовательно соединенные второй элемент И 7 и блок памяти 8 подключен соответственно к входам счетчика 9 и блока сравнения 11. К другому входу блока сравнения 11 подключен выход распределителя 6, к управляющему входу которого и к управляющим входам кодопреобразователя 10 и счетчиков 4, 9 подключены соответствующие выходы рещающего блока 12. К входам блока 12 подключены выходы счетчика 4, блока сравнения 11 и счетчика 9.

Устройство работает следующим образом.

Принимаемая двоичная последовательность, закодированная блочными корректирующими кодами, или с маркерными сигналами, представляющими собой некоторую фиксированную комбинацито, поступает в накопитель 1 с дещифратором 2.

При совпадении поступающей информации с законом построения кода или маркера на втором выходе дешифратора 2 появляются единичные сигналы. Эти сигналы далее следуют через элемент И 7 на блок памяти 8, где запоминаются все фазовые сдвиги последовательности на объеме одного цикла анализа.

С первого выхода дешифратора 2 на кодопреобразователь 10 поступают кодовые сигналы, соответствующие уравнениям проверок корректирующего кода или числу ощибочных знаков в маркерной посылке.

Кодопреобразователь 10 обеспечивает формирование единичного сигнала на элемент И 3 При условии, что кратность ошибок на анализнруемой.познции распределителя 6, управляемого генератором 5, превосходит установленное значение, которое задается .решающим блоком 12. В результате счетчик 4 производит подсчет циклов анализа, на которых кратность ошибок превосходит кратность корректируемых ошибок в коде или в маркерах, что повышает помехоустойчивость синхронизации в режиме захвата.

Накопленные в блоке памяти 8 результаты анализа различных фазовых сдвигов на последовательных циклах анализа постепенно исключаются из памяти, так как через элемент И 7 проходят только единичные сигналы, удовлетворяющие коду или маркерам с п1ериодичностью, равной длительности цикла.

Счетчик 9 подсчитывает число циклов анализа, в течение которых в блоке памяти 8 циркулирует один единичный сигнал, соответствующий с наибольшей вероятностью синхронному положению. В блоке сравнения 11 фаза этого сигнала сравнивается с фазой распределителя бив зависимости от результатов сравнения и срабатывания одного из счетчиков 4 или 9 решающий блок 12 вырабатывает управляющие сигналы на распределитель 6, кодопреобразователь 10 и счетчики 4, 9.

Совпадение фаз на блоке сравнения 11 при срабатывании счетчика 9 и при отсутпвии срабатывания счетчика 4 свидетельствует о нали.л синхронизма в работе устройства.

Срабатывание обоих счетчиков 4, 9 при наличии совпадения фаз характерно для ситуащш ложного обнаружения потери синхронизма, и рещающий блок 12 увеличивает коэффициент пересчета счетчика 4 или снижает значение подмножества ошибок.в кодопреобразователе 10.

Прн несовпадении фаз в блоке сравнения 11 срабатывание счетчиков 4. и 9 соответствует ситуации потери синхронизма, и решающий блок 12 производит фазирование распределителя 6 выделенными синхросигналами..

Прн несовпадении фаз в блоке сравнения 11 срабатывание счетчика 4 и отсутствие срабатывания счетчика 9 соответствуют случаю потери синхронизма и невыделению синхросигнала, и решающий блок 12 умейьилает коэффициент пересчета счетчика 9.

Предло7кенное устройство позволяет повысить помехоустойчивость синхронизации за счет более надежного обнаружения потери синхронизма в режиме захвата, а также выделения синхронного положения в режиме поиска при передаче информации по каналам связи с помехами.

Формула изобретения

Устройство синхронизации по циклам, содержащее последовательно соединенные входной накопитель и дешифратор, последовательно соединенньле перйый элемент И и счетчик ошибок, последовательно соединенные генератор тактовых импульсов и распределитель, выход которого подключен к первому входу первого элемента И, а также второй элемент И, к одному лз входов которого подключен выход блока памяти, и счетчик совпадений, отличающееся тем, что, с целью повышения помехоустойчивости, введены кодопреобразователь, блок сравнения и решающий блок, при этом кодопреобразователь включен между первым выходом дешифратора и вторым входом первого элемента И, а второй выход дешифратора через последовательно соединенные

второй элемент И и блок памяти подключен соответственно к входам счетчика совпадений и блока сравнения, к другому входу которого подключен выход распределителя, к управляющему входу которого н к управляющим входам кодопреобразователя, счетчнка ошибок и счетчика совпадений подключены соответствующие выходы решающего блока, к входам которого подключены соответственно выходы счетчика ошибок, блока сравнения и счетчика совпадений.

Источники информации, прииятые во вннмание при экспертизе:

1. Авторское свидетельство СССР № 498752. кл. Н 04 L 7/08. 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| Устройство цикловой синхронизации | 1980 |

|

SU944136A1 |

| Устройство синхронизации по циклам | 1973 |

|

SU498752A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство синхронизации по несущей частоте | 1983 |

|

SU1124440A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| Устройство для приема дискретной информации | 1983 |

|

SU1111260A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

Авторы

Даты

1979-01-05—Публикация

1977-03-29—Подача