(54) АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

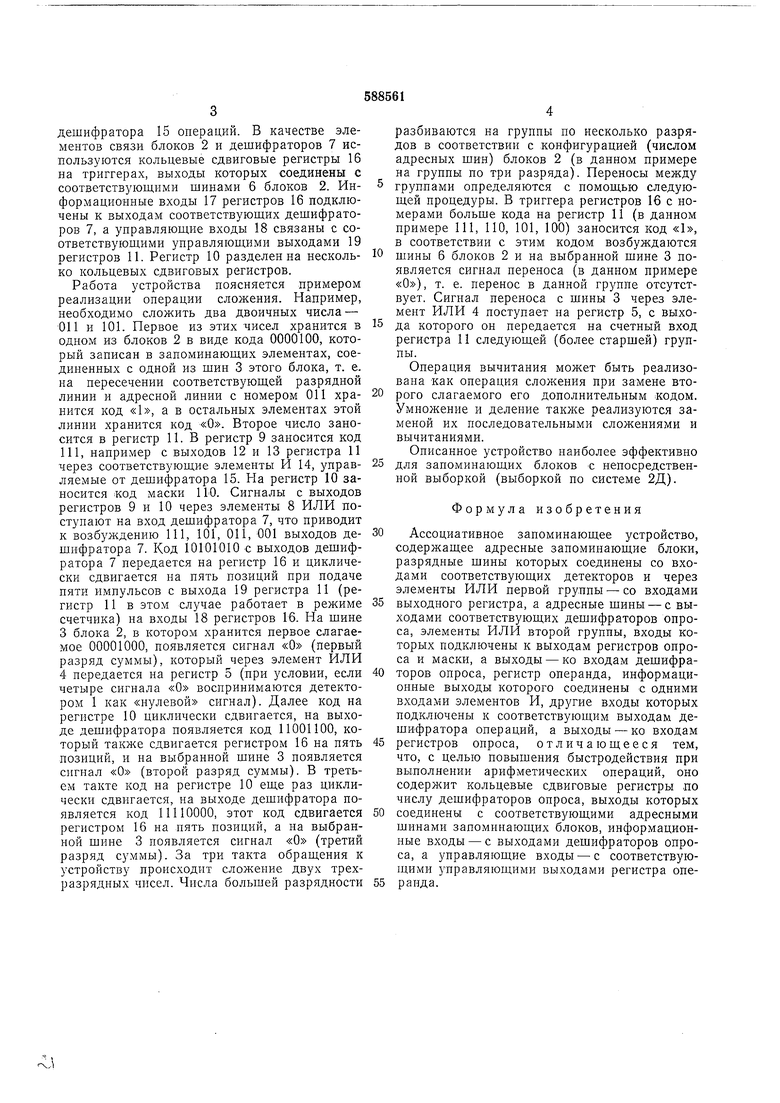

дешифратора 15 операций. В качестве элементов связи блоков 2 и дешифраторов 7 используются кольцевые сдвиговые регистры 16 на триггерах, выходы которых соединены с соответств)ющими шинами 6 блоков 2. Информационные входы 17 регистров 16 подключены к выходам соответствующих дешифраторов 7, а управляющие входы 18 связаны с соответствующими управляющими выходами 19 регистров 11. Регистр 10 разделен на несколько кольцевых сдвиговых регистров.

Работа устройства поясняется примером реализации операции сложения. Например, необходимо сложить два двоичных числа - 011 и 101. Первое из этих чисел хранится в одном из блоков 2 в виде кода 0000100, который записан в запоминающих элементах, соединенных с одной из шин 3 этого блока, т. е. на пересечении соответствующей разрядной линии и адресной линии с номером 011 хранится код «1, а в остальных элементах этой линии хранится код «О. Второе число заносится в регистр 11. В регистр 9 заносится код 111, например с выходов 12 и 13 регистра И через соответствзющие элементы И 14, управляемые от дешифратора 15. На регистр 10 заносится )Код маски 110. Сигналы с выходов регистров 9 и 10 через элементы 8 ИЛИ поступают на вход дешифратора 7, что приводит к возбуждению 111, 101, 011, 001 выходов дешифратора 7. Код 10101010 с выходов дешифратора 7 передается на регистр 16 и циклически сдвигается на пять позиций при подаче пяти импульсов с выхода 19 регистра 11 (регистр 11 в этом случае работает в режиме счетчика) на входы 18 регистров 16. На щине

3блока 2, в котором хранится первое слагаемое 00001000, появляется сигнал «О (первый разряд суммы), который через элемент ИЛИ

4передается на регистр 5 (при условии, если четыре сигнала «О воспринимаются детектором 1 как «нулевой сигнал). Далее код на регистре 10 циклически сдвигается, на выходе дешифратора появляется код 11001100, который также сдвигается регистром 16 на пять позиций, и на выбранной шине 3 появляется сигнал «О (второй разряд суммы). В третьем такте код на регистре 10 еще раз циклически сдвигается, на выходе дешифратора появляется код 11110000, этот код сдвигается регистром 16 на пять позиций, а на выбранной шине 3 появляется сигнал «О (третий разряд суммы). За три такта обращения к устройству происходит сложение двух трехразрядных чисел. Числа болыией разрядности

разбиваются на группы по несколько разрядов Б соответствии с конфигурацией (числом адресных щин) блоков 2 (в данном примере на группы по три разряда). Переносы между группами определяются с помощью следующей процедуры. В триггера регистров 16 с номерами больше кода на регистр 11 (в данном примере 111, ПО, 101, 100) заносится код «1, в соответствии с этим кодом возбуждаются шины 6 блоков 2 и на выбранной щине 3 появляется сигнал переноса (в данном примере «О), т. е. перенос в данной группе отсутствует. Сигнал переноса с шины 3 через элемент ИЛИ 4 поступает на регистр 5, с выхода которого он передается на счетный вход регистра 11 следующей (более старщей) группы.

Операция вычитания может быть реализована как операция сложения при замене второго слагаемого его дополнительным :кодом. Умножение и деление также реализуются заменой их последовательными сложениями и вычитаниями.

Описанное устройство наиболее эффективно для запоминающих блоков € непосредственной выборкой (выборкой по системе 2Д).

Формула изобретения

Ассоциативное запоминающее устройство, содержащее адресные запоминающие блоки, разрядные щины которых соединены со входами соответствующих детекторов и через элементы ИЛИ первой группы - со входами выходного регистра, а адресные щины - с выходами соответствующих дещифраторов опроса, элементы ИЛИ второй группы, входы которых подключены к выходам регистров опроса и маски, а выходы - ко входам дещифраторов опроса, регистр операнда, информационные выходы которого соединены с одними входами элементов И, другие входы которых подключены к соответствующим выходам дешифратора операций, а выходы - ко входам регистров опроса, отличающееся тем, что, с целью повышения быстродействия при выполнении арифметических операций, оно содерн ит кольцевые сдвиговые регистры по числу дешифраторов опроса, выходы которых соединены с соответствующими адресными щинами запомннающих блоков, информационные входы - с выходами дешифраторов опроса, а управляющие входы - с соответствующими управляющими выходами регистра операнда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1975 |

|

SU604033A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Ассоциативное запоминающее устройство | 1978 |

|

SU701349A1 |

| Ассоциативное запоминающее устройство | 1971 |

|

SU493162A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Запоминающее устройство на приборах с переносом заряда | 1979 |

|

SU894794A1 |

| Запоминающее устройство на сдвиго-ВыХ РЕгиСТРАХ | 1979 |

|

SU841052A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Устройство для сжатия последователь-НОСТи СигНАлОВ | 1979 |

|

SU842911A1 |

Авторы

Даты

1978-01-15—Публикация

1974-04-22—Подача