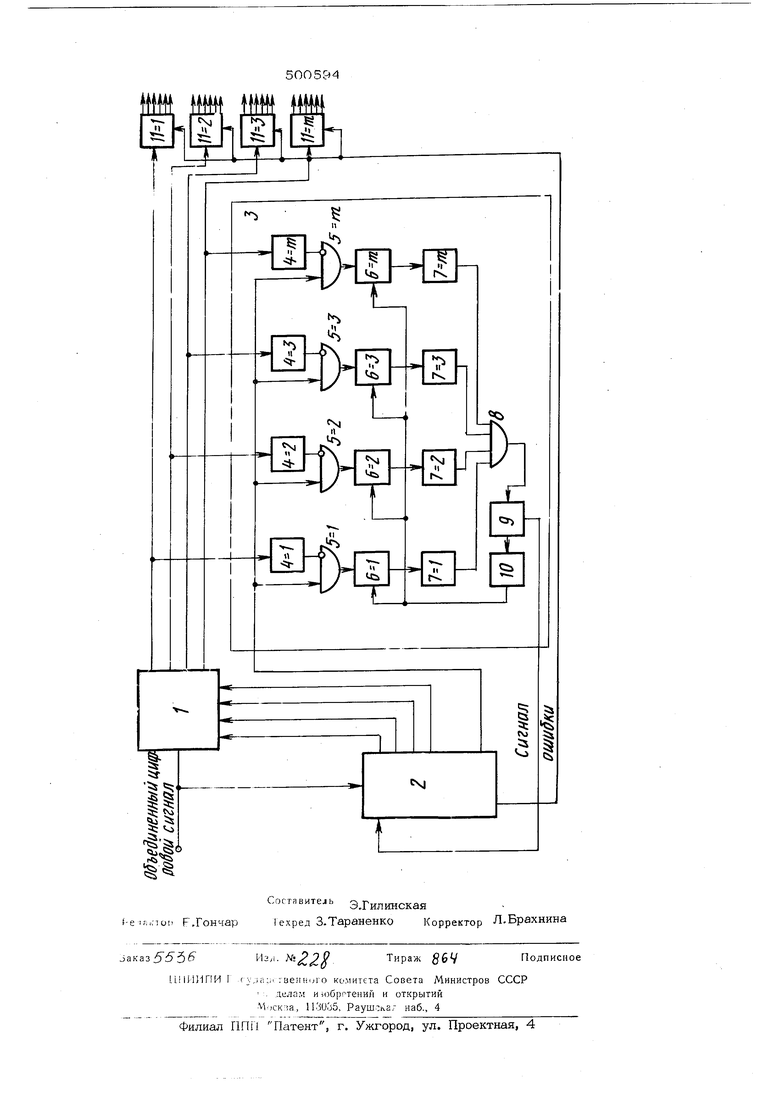

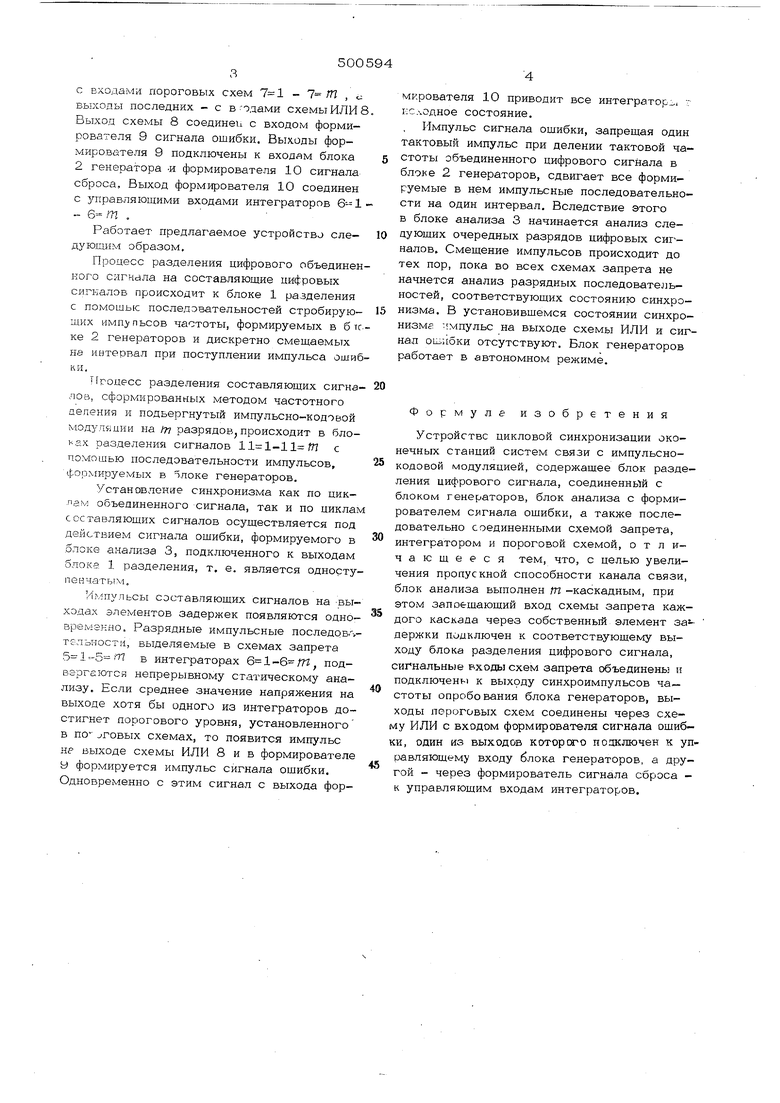

Изобретение относится к радиотехнике и Может испол1 зоБаться в системах связи с импульсно-кодовой модуляцией для цикловой синхронизации генераторного оборудования оконечных станций, в частности, в системах с импульсно-кодовой модуляцией синхронной сети связи при передаче цифрового сигнала, Известно устройство цикловой синхронизации оконечных станций систем связи с импульсно-кодовой модуляцией, содержащее блок разделения цифрового сигнала, соеди ненный с блоком генераторов, блок анализа с формирователем сигнала ошибки, а также .последовательно соединенными схемой запрета, интегратором и пороговой схемой. Цель изобретения - увеличение пропускной способности канала связи. Достигается это благодаря тому, что (блок анализа, выполнен Ш-каскадным,. при ; этом запрещающий вход схемы запрета каж дого каскада через собственный элемент .задержки подключен к соответствующему ; выходу блока разделения цифрового сигна;ла, сигнальные входы схем запрета объеди нены и подключены к выходу синхроимпуль- сов частоты опробывания блока генерато- ров, .выходы пороговых схем соединены через схему ИЛИ с входом формирователя сигнала ошибки, один из выходов которого подключен к управляющему входу блока генераторов, а другой - через формирователь сигнала сброса к управляющим входам интеграторов. На чертежепоказана I функциональная схема предложенного устройства (совместно с другими узлами приемной станции, с которыми оно взаимодействует). Устройство цикловой синхронизации оконечных станций систем связи с импульснокодовой модуляцией содержит блок 1 разделения цифрового сигнала, соединенный с блоком 2 генераторов , блок анализа 3, который выполнен ТП -каскадным. Блок анализа 3 в свою очередь содержит элементы задержки 4-1-4 fn . . Запрещающие входы схем запрета 5l-5f соединены соответственно с выходами элементов за-: держки. Выходы схем запрета 5-1 - 5 ОТ соединены с входами интеграторов 6-1 -&- ГП , Выходы интеграторов соединены с входами пороговых схем - 7 Л1 , ел выходы последних - с вводами схемы ИЛИ 8 Выход схемы 8 соединеи с входом формирователя 9 сигнала ошибки. Выходы формирователя 9 подключены к входам блока 2 генератора -и формирователя 10 сигнала сброса. Выход формирователя 10 соединен с управляющими входами интеграторов 6-1 - 6 m , Работает предлагаемое устройство еледующим образом. Процесс разделения цифрового объединен ного сигнала на составляющие цифровых сигналов происходит к блоке 1 разделения с помошыс последовательностей стробируюших MMnjnbCOB частоты, формируемых в б ic ке 2 генераторов и дискретно смещаемых на интервал при поступлении импульса ошиб к и. frouecc разделения составляющих сигналов, сформированных методом частотного целения и подвергнутый импульсно-кодовой модулйции на /т разрядов, происходит в блоках разделения сигналов Il :l-ll ft7 с помощью последовательности импульсов, 4f,opMKpyeMbix в 5локе генераторов. Установление синхронизма как по цик- пам объединенного сигнала, так и по циклам составляющих сигналов осуществляется под действием сигнала ошибки, формируемого в блоке анализа 3, подключенного к выходам блока 1 разделения, т. е. является односту пенчатьгм. Импульсы составляющих сигналов на -выходах элементов задержек появляются одновременно. Разрядные импульсные последов-гтельности, выделяемые в схемах запрета Б интеграторах 6 1-3-т, подвэргйются непрерывному статическому анализу. Если среднее значение напряжения на выходе хотя бы одного из интеграторов достигнет порогового уровня, установленного в ПО говых схемах, то появится импульс HP выходе схемы ИЛИ 8 и в формирователе У формируется импульс сигнала ошибки. Одновременно с этим сигнал с выхода фор- мкрователя 10 приводит все интeгpaтopi, : кс одное состояние. Импульс сигнала ошибки, запрещая один тактовый импульс при делении тактовой частоты объединенного цифрового сигнала в блоке 2 генераторов, сдвигает все формируемые в нем импульсные последовательности на один интервал. Вследствие этого в блоке анализа 3 начинается анализ следующих очередных разрядов цифровых сигналов. Смещение импульсов происходит до тех пор, пока во всех схемах запрета не начнется анализ разрядных последовательностей, соответствующих состоянию синхронизма. В установивщемся состоянии синхронизме импульс на выходе схемы ИЛИ и сигнал ош.цбки отсутствуют. Блок генераторов работает в автономном режиме. Формуле изобретения Устройстве пикловой синхронизации оконечных станций систем связи с импульснокодовой модуляцией, содержащее блок разделения цифрового сигнала, соединеннь№ с блоком генераторов, блок анализа с формирователем сигнала ошибки, а также последовательно соединенными схемой запрета, интегратором и пороговой схемой, отличающееся тем, что, с целью увеличения пропускной способности канала связи, блок анализа выполнен т -каскадным, при этом запрещающий вход схемы запрета каждого каскада через собственный элемент задержки подключен к соответствующему выходу блока разделения цифрового сигнала, сигнальные входы схем запрета объединены и подключены к выходу синхроимпульсов частоты опробования блока генераторов, выходы пороговых схем соединены через схему ИЛИ с входом формирователя сигнала ошибки, один из выходов которсуо подключен к управляющему входу блока генераторов, а другой - через формирователь сигнала сброса к управляющим входам интеграторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Устройство для определения достоверности передачи двоичной информации | 1988 |

|

SU1670794A1 |

| Устройство формирования испытательных сигналов для многоканальной системы связи с импульно-кодовой модуляцией и временным разделением каналов | 1977 |

|

SU657633A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| Видеорегенератор для систем связи с импульсно-кодовой модуляцией | 1977 |

|

SU792603A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2013 |

|

RU2534221C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК СИГНАЛОВ УПРАВЛЕНИЯ И ВЗАИМОДЕЙСТВИЯ С АДАПТИВНОЙ ДИФФЕРЕНЦИАЛЬНОЙ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1993 |

|

RU2103840C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

Авторы

Даты

1976-01-25—Публикация

1974-01-03—Подача