Изобретение относится к радиотехнике и может быть использовало в устройствах преобразования, обработки и передачи информации.

Известно устройство для генерации одиночных 1имиульсов, . содержащее i S-триггер, S вход которого подключен к первому входу выходного логического элемента «И-НЕ, выход которого соединен с R входом / 5-т1риггера и с первым входом иервого логического элемента «И-НЕ, второй вход которого подключен к выходу ./ 5-триггера, а выход первого логического элемента «И-НЕ соединен с вторым входом выходного логического элемента «И-НЕ, третий вход которого подключен к шине тактовых сигналов.

Цель изобретения - повышение стабильности длительности выходных импульсов.

Это достигается тем, что в предлагаемое устройство введен логический элемент «НЕ и /)-триггер, выход которого соединен с S входом / 5-триггвра, первый вход 1)-триггера подключен к шине аоинхроиньтх сигналов, а второй вход .D-триггера через логический элемент «НЕ соедииен с третьим входом выходного логического элемента «И-НЕ.

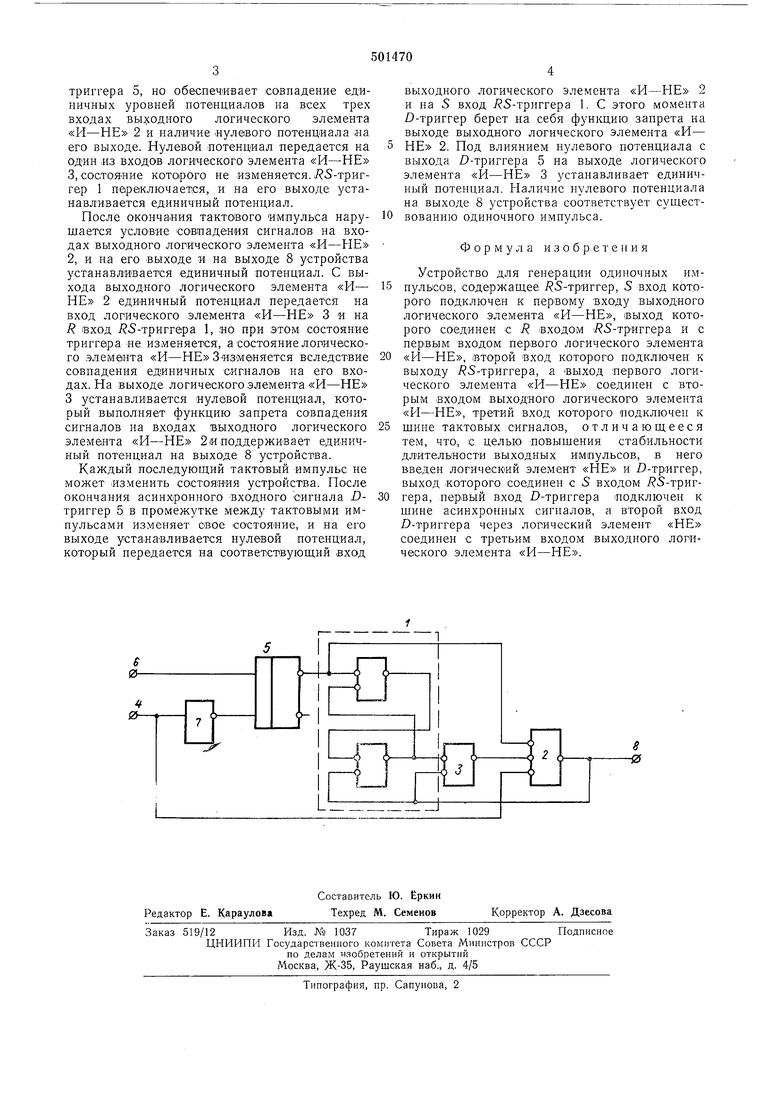

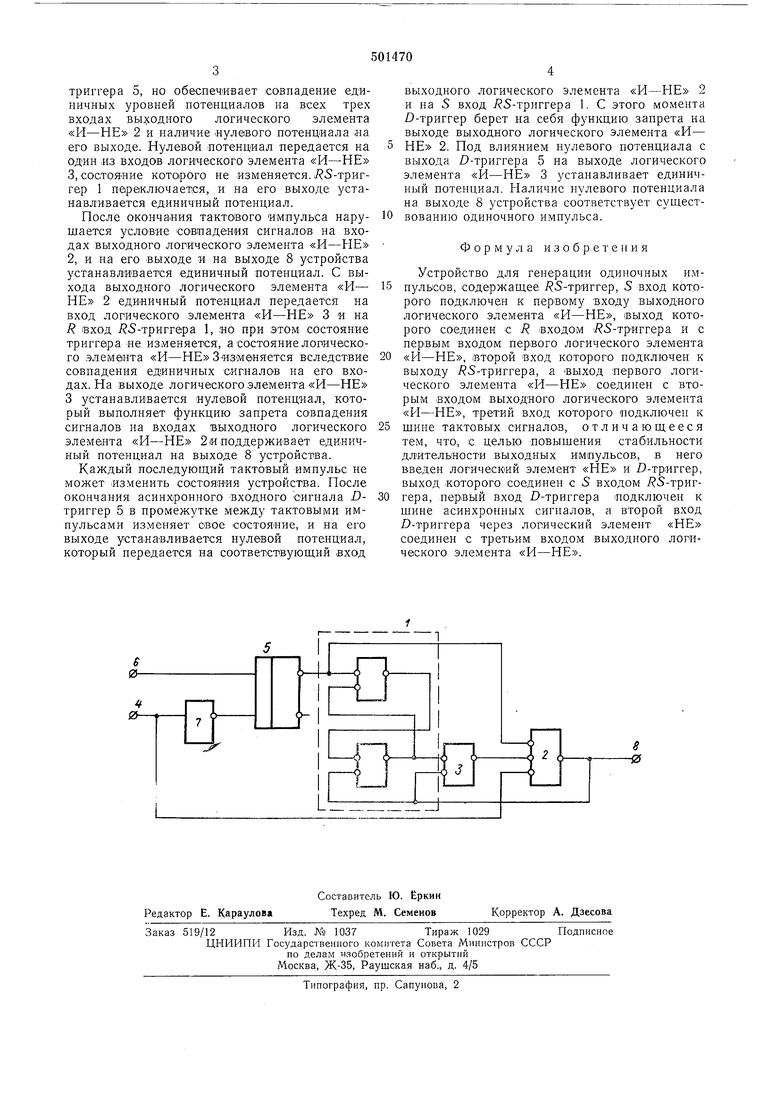

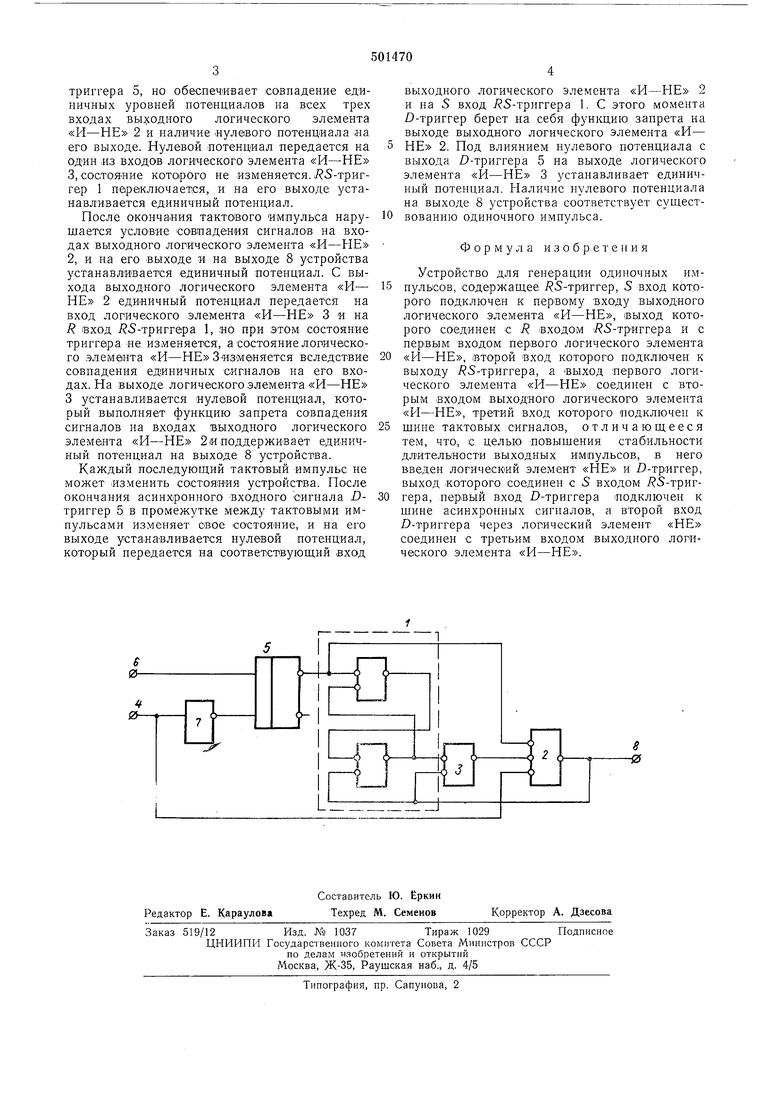

На чертеже приведена структурная электрическая схема предлагаемого устройства для генерации одиночных импульсов.

Устройство содержит S-триггер 1, 5 вход

которого подключен к первому входу выходного логического элемента «И-НЕ 2, выход которого соединен с J входом / 5-триггера 1 и с Первым входом логического элемента «И-НЕ 3, второй вход которого подключен к выходу У 5-триггера 1, а выход логического элемента «И-НЕ 3 соединен с вторым входом выходного логического элемента «И-НЕ 2, третий вход которого подключен к шине тактовых сигналов 4.

Выход /)-тригера 5 соединен с 5 входом JRSтриггера 1, первый -вход D-триггера подключен к шине асинхронных сигналов 6, а второй вход О-триггера через логический элемент «НЕ 7 соединен с третьим входом выходного логического элемента «И-НЕ 2.

Устройство для генерации одиночных импульсов работает следующим образом.

Поступающий на ши«у 6асинхронный входной сигнал переводит D-триггер 5 в единичное состояние. Единичный потенциал с его выхода подается на S вход / 5-триггера 1, но не меняет его состояния. Кроме того, единичный потенциал с выхода О-триггера 5 подается HP вход выходного логического элемента «И- НЕ 2, что означает разрешение для анализа совпадения сигналов на его входе. Поступающий на шину 4 и на один из входов выходного логического элемента «И-НЕ 2 тактовый импульс не изменяет состояние D3

триггера 5, но обеспечивает совпадение едипичных уровней потенциалов на всех трех входах выходного логического элемента «И-НЕ 2 и наличие .нулевого потенциала на его выходе. Нулевой потенциал передается на один |Из входов логического элемента «И-НЕ 3, состояние KOTOiporo не изменяется. ;/ 5-триггер 1 переключается, и иа его выходе устанавливается единичный потенциал.

После окончания тактового импульса нарушается условие совпадения сигналов на входах выходного логического элемента «И-НЕ 2, и на его выходе и на выходе 8 устройства устанавливается единичный потенциал. С выхода выходного логического элемента «И- НЕ 2 единичный потенциал передается на вход логического элемента «И-НЕ 3 и на R вход 5-триггера 1, яо при этом состояние триггера не изменяется, а состояние логического элемента «И-НЕ 3 изменяется вследствие совпадения единичных сигналов на его входах. На выходе логического элемента «И-НЕ 3 устанавливается нулевой потенциал, который выполняет функцию запрета совпадения сигналов на входах оаыходного логического элемента «И-НЕ 2 и поддерживает единичный потенциал на выходе 8 устройства.

Каждый последующий тактовый импульс не может изменить состояния устройства. После окончания асинхронного входного сигнала Dтриггер 5 в промежутке между тактовыми импульсами изменяет свое состояние, и на его выходе устанавливается нулевой потенциал, который передается на соответствующий вход

выходного логического элемента «И-НЕ 2 и на S вход ./ 5-триггера 1. С этого момента D-триггер берет на себя функцию запрета на выходе выходного логического элемента «И- НЕ 2. Под влиянием пулевого потенциала с выхода D-триггера 5 на выходе логического элемента «И-НЕ 3 устанавливает единичный потенциал. Наличие нулевого потенциала на выходе 8 устройства соответствует существованию одиночного импульса.

Формула изобретения

Устройство для генерации одиночных импульсов, содержащее 5-триггер, S вход которого подключен к первому входу выходного логического элемента «И-НЕ, выход которого соединен с R входом / 5-триггера и с первым входом первого логического элемента

«И-НЕ, второй вход которого подключен к выходу S-триггера, а выход первого логического элемента «И-НЕ соединен с вторым входом выходного логического элемента «И-НЕ, третий вход которого подключен к

щине тактовых сигналов, отличающееся тем, что, с целью повышения стабильности длительности выходных импульсов, в него введен логический элемент «НЕ и D-триггер, выход которого соединен с 5 входом / 5-триггера, пер)Вый вход D-триггера подключен к шине асинхронных сигналов, а второй вход D-триггера через логический элемент «НЕ соединен с третьим входом выходного логического элемента «И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для генерации одиночных импульсов | 1977 |

|

SU711670A1 |

| Устройство синхронизации импульсов | 1988 |

|

SU1531185A1 |

| Устройство для задержки и формирования импульсов | 1988 |

|

SU1539979A1 |

| Формирователь синхроимпульсов | 1981 |

|

SU951669A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Формирователь одиночного импульса | 1980 |

|

SU892677A2 |

| Устройство тактовой синхронизации | 1978 |

|

SU748839A1 |

| Устройство для выделения одиночного импульса | 1978 |

|

SU744935A1 |

| Формирователь импульсов | 1989 |

|

SU1720151A1 |

| Преобразователь последовательностииМпульСОВ B ОдиНОчНый пРяМОугОльНыйиМпульС | 1979 |

|

SU809534A1 |

6

0« 0

Авторы

Даты

1976-01-30—Публикация

1974-04-17—Подача