1

Изобретение относится к области вычислительной техники/ может найти применение при построении квазистатических регистров сдвига и является усовершенствованием иэвест-г ного устройства, описанного в авт. св. 570108.

В ОСНОВНОМ изобретении по авт. св. 570108 описана ячейка памяти для регистра сдвига, содержащая коммутирующий МДП-транзистор и инвертор, выйспненный на последовательно включенных нагрузочном и ключевом МДП-транзисторах, причем сток нагрузочного МДП-транзистора подключен к шине питания, исток коммутирующего МДП-транзистора подключен к затвору ключевого транзистора, а дток - к тактовой шине и к затвору нагрузочного МДП-транзистора 1.

При последовательном соединении таких ячеек памяти образуется динамический регистр сдвига.

Недостатком известной ячейки памяти для регистра сдвига является большое потребление мощности за сче постоянного протекания тока, так ка один из ключевых транзисторов всегд открыт, а нагрузочные транзисторы открыты постоянно.

Целью дополнительного изобретения является уменьшение потребляемой мсадн ос ти.

Поставленная цель достигается тем, что в ячейку памяти регистра сдвига по авт. ев. № 570108 введены конденсатор и два дополнительных МДП-транзистора, соединенные тригГерт ной связью, истоки которых соедине0ны со стоком ключевого МДП-транзистора, сток перВЪго дополнительного МДП-транзистора через конденсатор подключен к соответствующей тактовой шине, а сток второго дополнительно5го МДП-транзистора - к шине питания.

Такое техническое решение обеспечивает квазистатический режим работы ячейки памяти в составе регистра, что значительно уменьшает потребляе0мую мЬщность, так как токи винверторах текут толькоВО время действия тактовых сигналов.

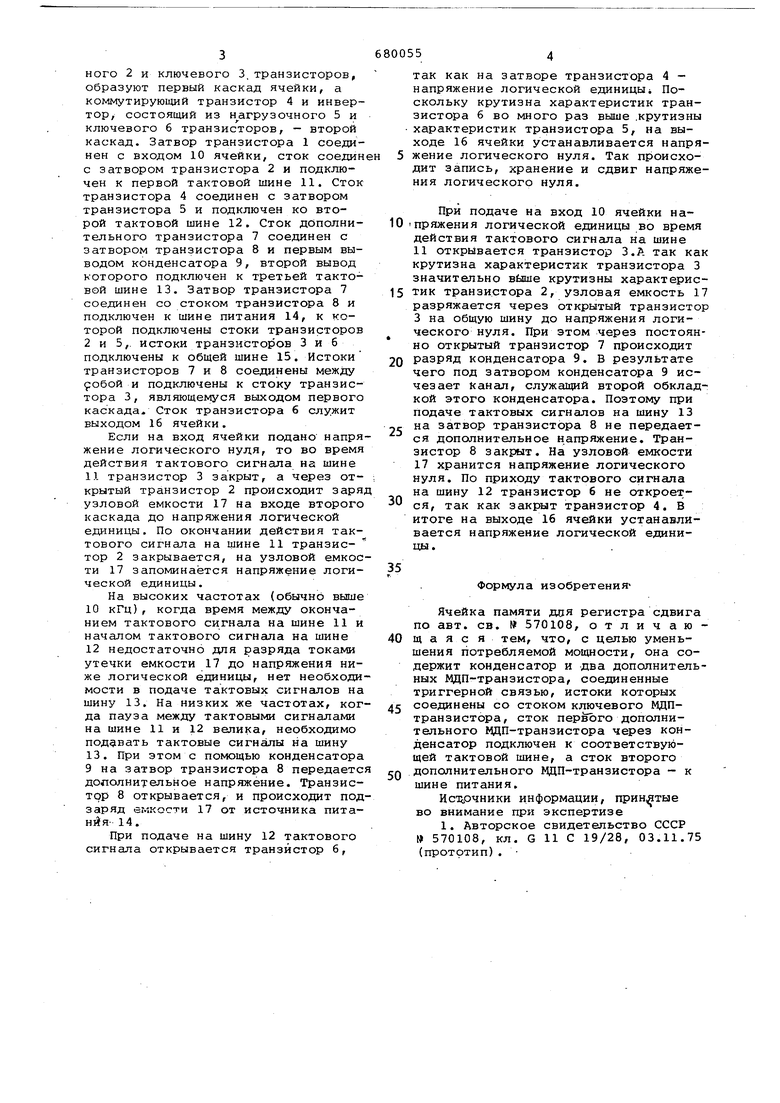

На фиг. 1 представлена.электрическая схема ячейки памяти для регистра

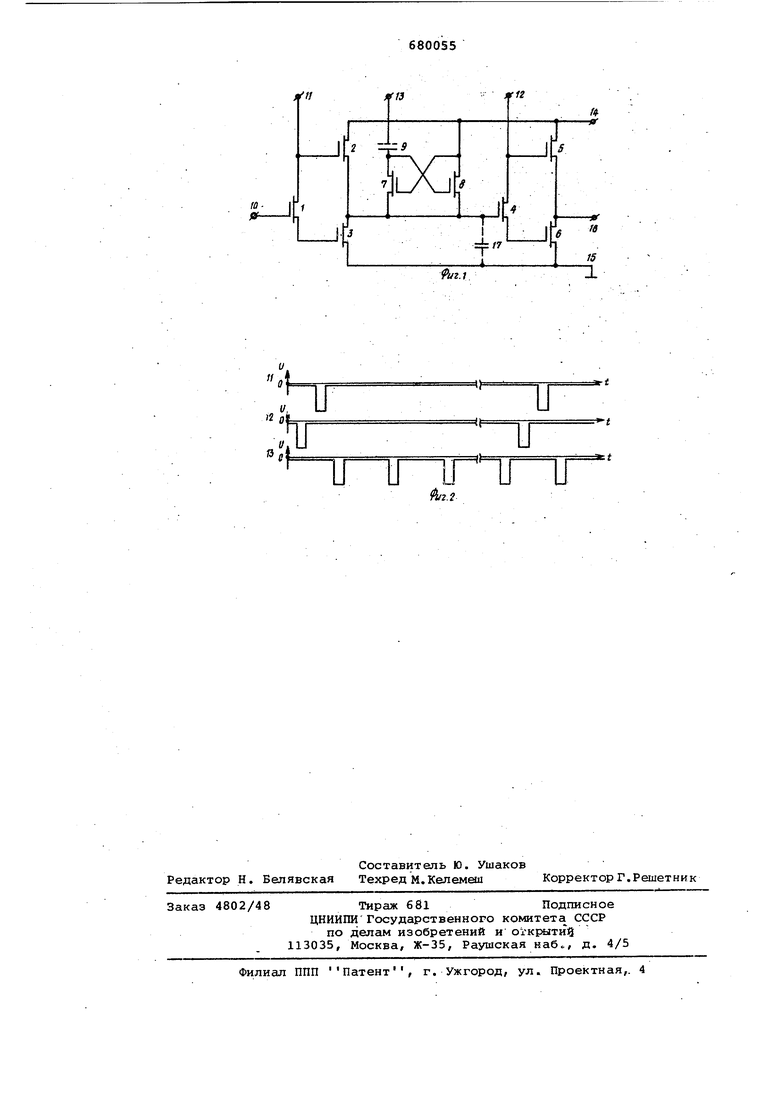

5 сдвига; на фиг. 2 - временная диаграмма сигналов на тактовых шинах.

Устройство выполнено на восьми МДП-транзисторах 1-8 и одном конденсаторе 9. Коммутирующий транзистор 1

0 и инвертор, состоящий из нагрузочного 2 и ключевого 3.транзисторов, образуют первый каскад ячейки, а коммутирующий транзистор 4 и инвертор, СОСТОЯ1ДИЙ из н агрузочного 5 и ключевого 6 транзисторов, - второй каскад. Затвор транзистора 1 соединен с входом 10 ячейки, сток соедин с затвором транзистора 2 и подключен к первой тактовой шине 11. Сток транзистора 4 соединен с затвором транзистора 5 и подключен ко второй тактовой шине 12. Сток дополнительного транзистора 7 соединен с затвором транзистора 8 и первым выводом конденсатора 9, второй вывод которого подключен к третьей тактовой шине 13. Затвор транзистора 7 соединен со стоком транзистора 8 и подключен к шине питания 14, к которой подключены стоки транзисторов 2 и 5,. истоки транзисторов 3 и 6 подключены к общей шине 15. Истоки транзисторов 7 и 8 соединены между 9обой и подключены к стоку транзистора 3, являющемуся выходом первого каскада. Сток транзистора 6 служит выходом 1б ячейки.

Если на вход ячейки подано напряжение логического нуля, то во время действия тактового сигнала на шине

11транзистор 3 закрыт, а через открытый транзистор 2 происходит заря узловой емкости 17 на входе второго каскада до напряжения логической единицы. По окончании действия тактового сигнала на шине 11 транзистор 2 закрывается, на узловой емкости 17 запоминается напряжение логической единицы.

На высоких частотах (обычно выше 10 кГц), когда время между окончанием тактового сигнала на шине 11 и началом тактового сигнала на шине

12недостаточно для разряда токами утечки емкости 17 до напряжения ниже логической единицы, нет необходимости в подаче тактовых сигналов на шину 13. На низких же частотах, когда пауза между тактовыми сигналами на шине 11 и 12 велика, необходимо подавать тактовые сигналы на шину 13. При этом с помощью конденсатора 9 на затвор транзистора 8 передаетс дополнительное напряжение. Транзистор 8 открывается, и происходит подзаряд емкости 17 от источника питания- 14.

При подаче на шину 12 тактового сигнала открывается транзистор б.

так как на затворе транзистора 4 напряжение логической единицыi Поскольку крутизна характеристик транзистора б во много раз выше .крутизны характеристик транзистора 5, на выходе 16 ячейки устанавливается напряжение логического нуля. Так происходит запись, хранение и сдвиг напряжения логического нуля.

При подаче на вход 10 ячейки напряжения логической единицы во время действия тактового сигнала на шине 11 открывается транзистор З.А так как крутизна характеристик транзистора 3 значительно вЬпде крутизны характеристик транзистора 2, узловая емкость 17 разряжается через открытый транзистор 3 на общую шину до напряжения логического нуля. При этом через постоянно открытый транзистор 7 происходит разряд конденсатора 9. В результате чего под затвором конденсатора 9 исчезает канал, служащий второй обкладкой этого конденсатора. Поэтому при подаче тактовых сигнешов на шину 13 на затвор транзистора 8 не передается дополнительное напряжение. Транзистор 8 закрыт. На узловой емкости 17 хранится напряжение логического нуля. По приходу тактового сигнала на шину 12 транзистор 6 не откроется, так как закрыт транзистор 4. В итоге на выходе 16 ячейки устанавливается напряжение логической единицы.

Формула изобретения

Ячейка памяти доя регистра сдвига по авт. св. № 570108, отличающаяся тем, что, с целью уменьшения потребляемой мощности, она содержит конденсатор и два дополнительных МДП-транзистора, соединенные триггерной связью, истоки которых соединены со стоком ключевого МДПтранзистора, сток первого дополнительного ВДП-транзистора через конденсатор подключен к соответствующей тактовой шине, а сток второго дополнительного МДП-транзистора - к шине питания.

Ис1ьочники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

570108, кл. G 11 С 19/28, 03.11.75

(протртип).

J

-.17

tS

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для регистра сдвига | 1975 |

|

SU570108A1 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Ячейка памяти для регистра сдвига | 1983 |

|

SU1125655A1 |

| Ячейка памяти на МДП транзисторах | 1981 |

|

SU968854A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU902075A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Регистр сдвига | 1975 |

|

SU550678A1 |

| Ячейка памяти для регистра сдвига | 1972 |

|

SU503295A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

Авторы

Даты

1979-08-15—Публикация

1977-05-11—Подача