Изобретение относится к импульсной и вычислительной технике и может быть использовано в интегральных схемах запоминающих устройств.

Цель изобретения - повышение быстродействия устройства за счет устранения влияния емкости нагрузки на скорость перезаряда узлов устройства путем подключения емкости нагрузки к источнику через дополнительный транзистор, а также введения еще трех транзисторов и одного инвертора для управления переключениями транзисторов и процессом подкачки потенциала на выходную шину.

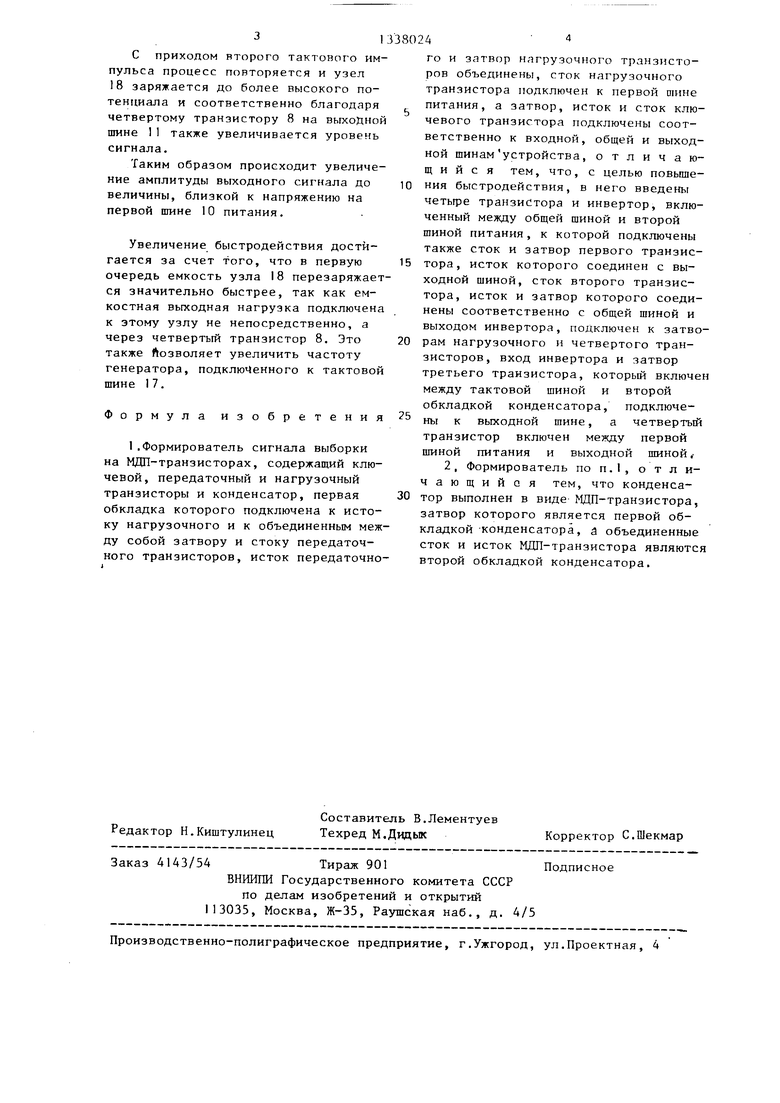

На чертеже приведена принципиальная схема формирователя.

Устройство содержит ключевой 1 , передаточный 2, нагрузочный 3 тран- . зисторы, конденсатор 4, первый 5, второй 6, третий 7 и четвертый 8 транзисторы, инвертор 9.

Стоки нагрузочного 3 и четвертого 8 транзисторов подключены к первой шине 10 питания, а выходная шина 11 соединена с источниками первого 5 и четвертого 8 транзисторов, стоком ключевого транзистора 1, а также с затвором третьего транзистора 7 и входом 12 инвертора 9, выход 13 которого соединен с затвором второго транзистора 6.

Входная шина 14 подключена к затвору ключевого транзистора 1, исток которого соединен с источником второго транзистора 6 и подключен к общей шине 15.

Сток и затвор первого транзистора 5 подключены к второй шине 16 пита- НИИ. Сток и затвор передаточного транзистора 2 и исток нагрузочного транзистора 3 соединены с первой обкладкой конденсатора 4, вторая обкладка которого через третий транзис- тор 7 подключена к тактовой шине 17.

Затворы нагрузочного 3 и четвертого 8 транзисторов, исток передаточного 2 и сток второго 6 транзисторов объединены, а инвертор 9 включен меж- ду второй шиной 16 питания и общей шиной 15.

Конденсатор 4 выполнен в виде МДП-транзистора, затвор которого является первой обкладкой конденсатора а объединенные сток и исток - второй обкладкой

Устройство функционирует следующим образом.

На первую шину 10 питания подается постоянное напряжение, величина которого достаточна для формирования выходного сигнала заданной амплитуды Напряжение на второй шине 16 питания меньше этой величины.

Когда на входную шину 14 поступает сигнал 1, на выходной шине II устанавливается нулевой исходный уровень сигнала. Одновременно закрытый третий транзистор 7 блокирует подачу импульсов с тактовой шины 16 на конденсатор 4. Сигнал 1 с вьосо- да 13 инвертора 9 открывает второй транзистор 6 и разряжает узел 18, образованный затворами нагрузочного 3 и четвертого 8 транзисторов, до потенциала общей шины 15 так что эти транзисторы закрыты и изолируют вы- ходную шину I1 от первой шины питания . I

Когда на входную шину 14 поступает сигнал о, на выходной шине 11 за несколько циклов действия тактового сигнала по тактовой шине 17 происходит формирование выходного единичного сигнала.

В этот период нагрузочный транзистор 3, а также третий транзистор 7 открыты, а второй транзистор 6 заперт.

Сигнал I на выходной шине 11 появляется сначала за счет открытого транзистора 5 от второй шины 16 питания, а дальнейшее увеличение его амплитуды происходит от источника, подключенного к первой шине 10 питания через четвертый транзистор 8;

С приходом переднего фронта импульса по тактовой шине 17 через открытый третий транзистор 3, конденсатор 4 и передаточный .транзистор 2 в диодном включении заряд передается в узел 18 и поступает на затвор четвертого транзистора 8, который открывается.

По приходу заднего фронта тактового импульса ток через конденсатор 4 течет в обратном направлении, но узел 18 не разряжается, так как передаточный транзистор 2 включен как диод. Спад потенциала на первой обкладке конденсатора 4 компенсируется током через открытый нагрузочный транзистор 3 от источника, подключенного к первой гаине 10 питания.

С приходом второго тактового импульса процесс повторяется и узел 18 заряжается до более высокого потенциала и соответственно благодаря

четвертому транзистору 8 на выходной шине 11 также увеличивается уровень сигнала.

Таким образом происходит увеличение амплитуды выходного сигнала до величины, близкой к напряжению на первой шине 10 питания.

Увеличение быстродействия достигается за счет того, что в первую очередь емкость узла 18 перезаряжается значительно быстрее, так как емкостная выходная нагрузка подключена к этому узлу не непосредственно, а через четвертый транзистор 8. Это также Аозволяет увеличить частоту генератора, подклю11енного к тактовой шине 17.

Формула изобретения

1.Формирователь сигнала выборки на МДП-транзисторах, содержащий ключевой, передаточный и нагрузочный транзисторы и конденсатор, первая обкладка которого подключена к истоку нагрузочного и к объединенным между собой затвору и стоку передаточного транзисторов, исток передаточноРедактор Н.Киштулинец Заказ 4143/54

Составитель В.Лементуев Техред М.Двдык

Тираж 901 ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-33, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

го и затвор нагрузочного транзисторов объединены, сток нагрузочного транзистора подключен к первой шине питания, а затвор, исток и сток ключевого транзистора подключены соответственно к входной, общей и выходной шинам устройства, отличающийся тем, что, с целью повышения быстродействия, в него введены четыре транзистора и инвертор, включенный между общей шиной и второй шиной питания, к которой подключены также сток и затвор первого транзистора, исток которого соединен с выходной шиной, сток второго транзистора, исток и затвор которого соединены соответственно с общей шиной и выходом инвертора, подключен к затворам нагрузочного и четвертого транзисторов, вход инвертора и затвор третьего транзистора, который включе между тактовой шиной и второй обкладкой конденсатора, подключены к выходной щине, а четвертый транзистор включен метзду первой шиной питания и выходной шиной ,

2, Формирователь по п.I, о т л и- чающийоя тем, что конденсатор выполнен в виде МДП-транзистора, затвор которого является первой обкладкой -конденсатора, а объединенные сток и исток МДП-транзистора являютс второй обкладкой конденсатора.

Корректор С.Шекмар Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Выходное устройство | 1978 |

|

SU771874A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Формирователь импульсов на МОП-транзисторах | 1984 |

|

SU1236604A1 |

| Устройство для последовательного включения источников питания в МДП интегральных схемах | 1986 |

|

SU1406771A1 |

Изобретение может быть использовано в интегральных схемах запоминающих устройств импульсной и вычислительной техники. Цель изобретения - повышение быстродействия формирователя - достигается путем устранения влияния емкости нагрузки на скорость перезаряда его накопительных элементов в результате подключения емкости нагрузки к источнику питания через дополнительный транзистор,а также введения еще трех транзисторов и одного инвертора для управления переключением транзисторов в процессе подкачки потенциала на выходную шину. Формирователь содержит ключевой 1, передаточный 2 и нагрузочньгй 3 транзисторы, конденсатор 4, транзисторы 6, 7 и 8, инвертор 9, шины: питания 10 и 16, выходные II и 14, общую 15, тпктоную 17. Инвертор 9 имеет вход 12 и выход 13. Конденсатор 4 выполнен в виде МДП-транзистора, затвор которого является первой обкладкой конденсатора, а объединенные сток и исток - второй об- кладкой. 1 з .п. ф-лы, 1 ил. (Л со со 00 о IsD

| Патент США № 4347448, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| IEEE Journal of Solid-State Cireuifs, 1983, № 5, p.535 | |||

| I | |||

Авторы

Даты

1987-09-15—Публикация

1986-05-27—Подача