(54) ЧЕТЫРЕХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР НА МДП-ТРАНЗИСТОРАХ

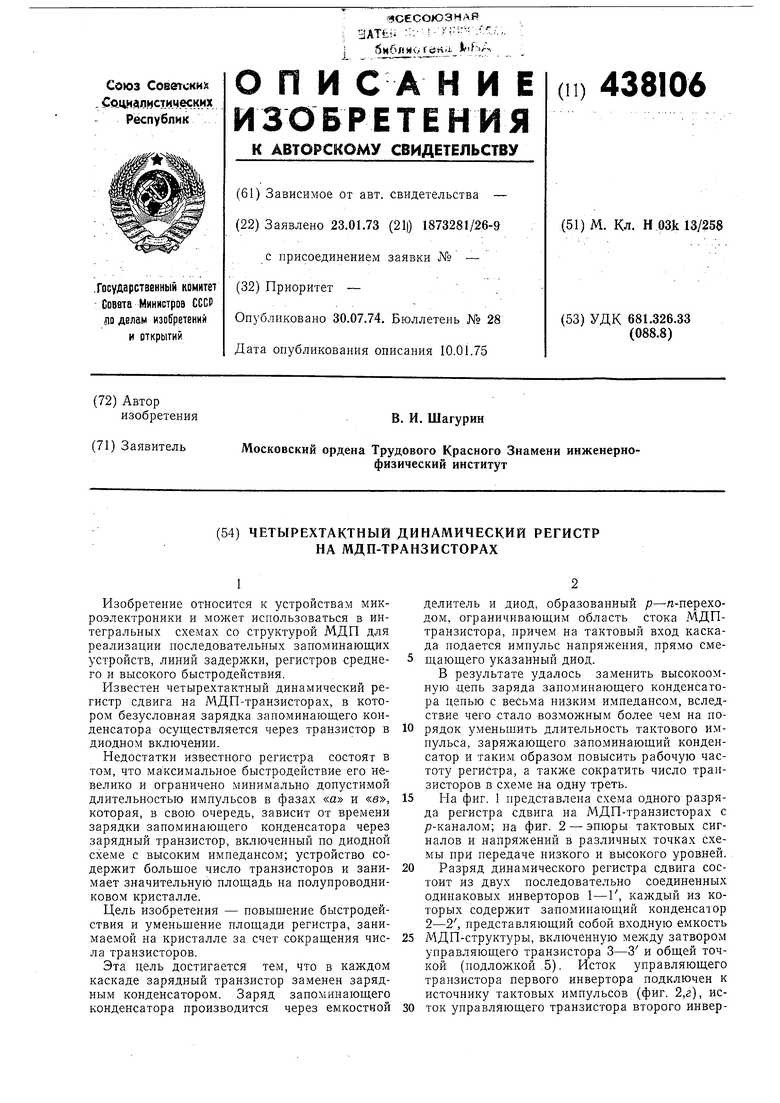

тора подключен к источнику тактовых импульсов (фиг. 2,6). Последовательно с управляющим транзистором в каждом Инверторе включены транзисторы 4-4 и зарядные конденсаторы 6-б. Затвор ключевого транзистора 4 и зарядный конденсатор 6 первого инвертора подключены соответственно к генераторам импульсов б и а, а затвор ключевого транзистора 4 и зарядный конденсатор 6 второго инвертора - к генераторам импульсов г и в. Входом каждого из инверторов являются затворы управляющих транзисторов 3-3. Выходами каждого из инверторов служат средние точки ключевых транзисторов и зарядных конденсаторов, к которым подключены паразитные диоды 7-7, образованные границей раздела стоковых областей ключевых транзисторов и подложки 5.

Устройство работает следующим образом.

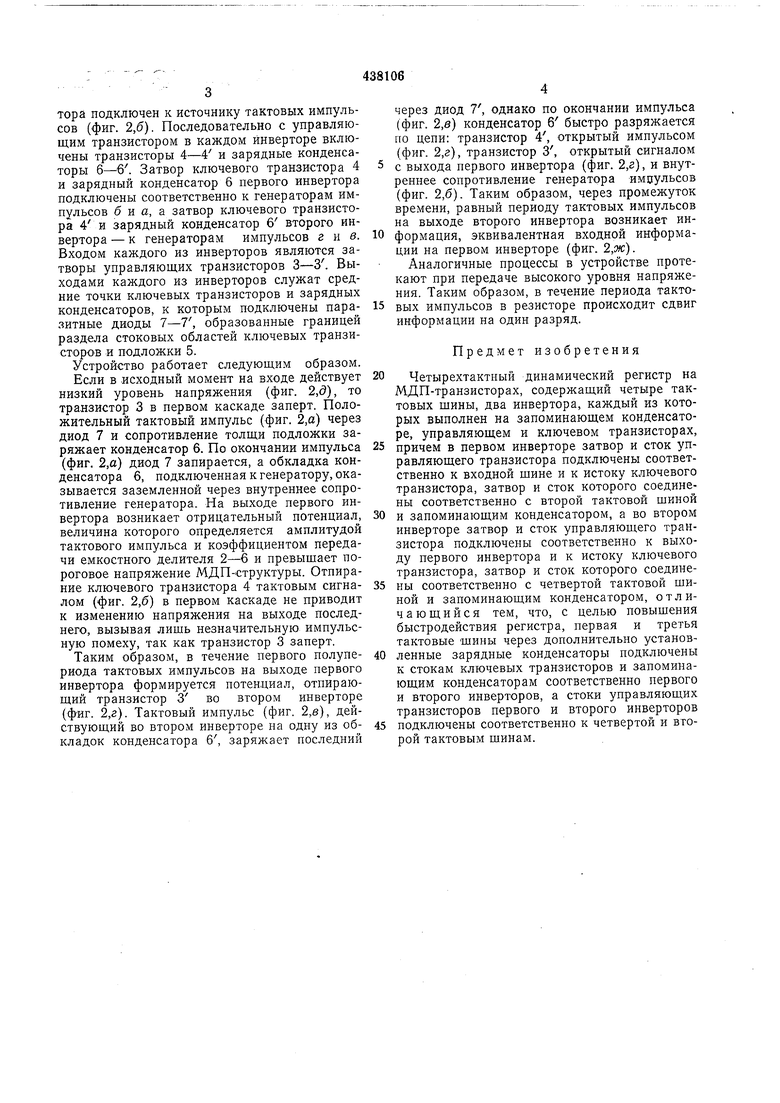

Если в исходный момент на входе действует низкий уровень напряжения (фиг. 2,5), то транзистор 3 в первом каскаде заперт. Положительный тактовый импульс (фиг. 2,а) через диод 7 и сопротивление толщи подложки заряжает конденсатор 6. По окончании импульса (фиг. 2,а) диод 7 запирается, а обкладка конденсатора 6, подключенная к генератору, оказывается заземленной через внутреннее сопротивление генератора. На выходе первого инвертора возникает отрицательный потенциал, величина которого определяется амплитудой тактового импульса и коэффициентом передачи емкостного делителя 2-6 и превышает пороговое напряжение МДП-структуры. Отпирание ключевого транзистора 4 тактовым сигналом (фиг. 2,6) в первом каскаде не приводит к изменению напряжения на выходе последнего, вызывая лишь незначительную импульсную помеху, так как транзистор 3 заперт.

Таким образом, в течение первого полупериода тактовых импульсов на выходе первого инвертора формируется потенциал, отпирающий транзистор 3 во вгором инверторе (ф-иг. 2,г). Тактовый импульс (фиг. 2,8), действующий во втором инверторе на одну из обкладок конденсатора 6, заряжает последний

через диод Т, однако по окончании импульса (фиг. 2,0) конденсатор 6 быстро разряжается по цепи: транзистор 4, открытый импульсом (фиг. 2,г), транзистор 3, открытый сигналом с выхода первого инвертора (фиг. 2,г), и внутреннее сопротивление генератора имоульсов (фиг. 2,6). Таким образом, через промежуток времени, равный периоду тактовых импульсов на выходе второго инвертора возникает информация, эквивалентная входной информации на первом инверторе (фиг. 2,ж).

Аналогичные процессы в устройстве протекают при передаче высокого уровня напряжения. Таким образом, в течение периода тактовых импульсов в резисторе происходит сдвиг информации на один разряд.

Предмет изобретения

Четырехтактный динамический регистр на МДП-транзисторах, содержащий четыре тактовых щины, два инвертора, каждый из которых выполнен на запоминающем конденсаторе, управляющем и ключевом транзисторах,

причем в первом инверторе затвор и сток управляющего транзистора подключены соответственно к входной шине и к истоку ключевого транзистора, затвор и сток которого соединены соответственно с второй тактовой шиной

и запоминающим конденсатором, а во втором инверторе затвор и сток управляющего транзистора подключены соответственно к выходу первого инвертора и к истоку ключевого транзистора, затвор и сток которого соединены соответственно с четвертой тактовой шиной и запоминаюшим конденсатором, отличающийся тем, что, с целью повышения быстродействия регистра, первая и третья тактовые шины через дополнительно установленные зарядные конденсаторы подключены к стокам ключевых транзисторов и запоминающим конденсаторам соответственно первого и второго инверторов, а стоки управляющих транзисторов первого и второго инверторов

подключены соответственно к четвертой и второй тактовым шинам.

n

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

| Формирователь импульсов регенерации для запоминающих устройств на мдп-транзисторах | 1974 |

|

SU500581A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Устройство согласования на мпд-транзисторах | 1973 |

|

SU661797A1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Усилитель считывания | 1979 |

|

SU858093A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU902075A1 |

| Формирователь двухполярных сигналов | 1988 |

|

SU1582372A1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| Ячейка памяти для регистра сдвига | 1972 |

|

SU503295A1 |

I генератор- L

Л генератор

Фаг. 1

л

Авторы

Даты

1974-07-30—Публикация

1973-01-23—Подача