1

Изобретение относится к области вычислительной техники.

Известны устройства для обмена данными, содержащие блоки памяти, приема правляющего слова, буферной памяти, сравнения, приоритетного выбора, управления буферной пагу1ятыо, сиихропизации, соиряжепия, регистры текущего и конечного адресов, коммутатор адресов. Причем блок памяти соединеи ипформациопной шииой с блоком б ферной памяти и блоком приема управляющего слова, выход которого подключен к входам регистров текущего и коиечиого адресов. Выходы последних соединены с соответствуюии1ми входа ми-блока сравнения. Управляюпи-1Й выход блока соиряжения подключен к первому входу блока синхронизации и входу блока управления буферной памятью, выходы которого подключены соответствеино к управляюп1,ему входу блока буферной памяти и второму входу блока сиихроиизации. Выход блока еипхронизации соединеи с входом блока приоритетного выбора, блок сопряжения соединен двусторонними связями с блоком буфериой памяти, первый вход коммутатора адресов соедииен с соответствующим выходом регистра текуи1,его адреса, выход подключен к адресиому входу блекл памяти.

В известпых устройствах обмен информацией производится по инструкции, храияи1ейся в

памяти и требующей для своего выполнепия использоваиия арифметического блока. При этом для выборки самой ииструкции используются команды, адреса и запросы, поступающие из периферийных устройств. Выполнение каждой инструкции требует прерывания теку цей ггрограммы и участия арифметического блока в операциях обмена информацией с периферийными устройствами.

В целях иовыи1ения эффективности в предлагаемое устройство введены блокн управления подканалом, согласованпя и блок управления обменом, первый вход которого соединен с нервы.м выходом блока приоритетиого выбора, выходы подключены соответствеппо к первым входам блоков памяти, приема управляюидего слова, сопряжения и управляющему входу регистра текущего адреса. Второй выход блока приоритетного выбора соединен с входом блока управления подкапалом, выходы которого подключены соответственно к вторым входам блоков памяти, приема управляющего слова, управления обменом и коммутатора адресов. Третий вход коммутатора подключеи к выходу блока сопряжения, выход блока сравпепия соединеи с третьим входом блока управления обменолГ, соединенного с управляющими входом и выходом устройства, вход блока согласоваиия подключеи к информационной шиие, выход - к второму входу блока сопряжеНИИ. Это обеспечивает обмен информацией двумя параллельными потоками, что позволяет производить считывание командной информации для выполнения следующей команды программы канала в процессе обмена данными по текуп:1ей команде. Тем самым сокращается время выполнения последовательности команд программы канала. Кроме того, отсутствие прерывания текущей программы, выполняемой процессором в процессе выполнения программы канала, значительно повышает эффективность работы процессора. Использование устройства в каналах позволяет расширить интерфейс ввода-вывода и увеличить тем самым парк периферийных устройств вычислительной машины.

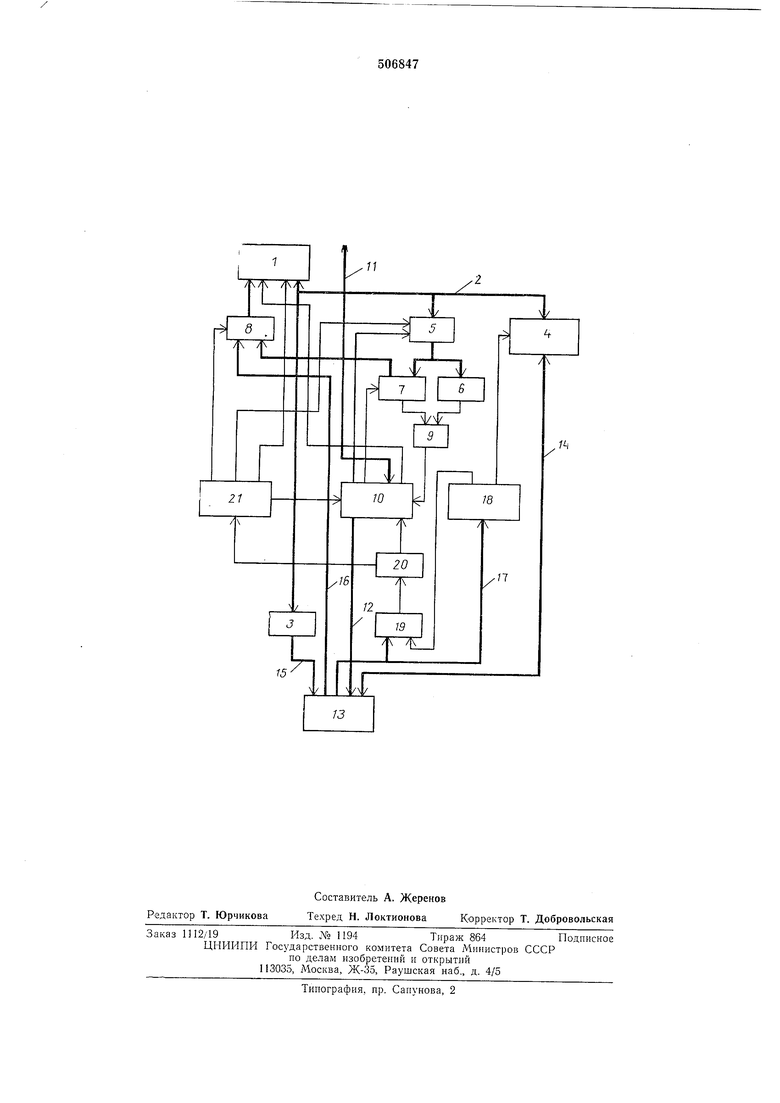

На чертеже ноказана блок-схема предлагаемого устройства.

Устройство содержит блок 1 памяти, информационную шину 2, блоки согласования 3, буферной памяти 4, приема управляюшего слова 5, регистры конечного 6 и текущего 7 адресов, коммутатор 8 адресов, блок 9 сравнения, блок 10 управления обменом, шину 11 «Управление, шину 12 «Управление каналом, блок 13 сопряжения (оконечное устройство), шины «Данные 14, «Выдача 15, «Адрес обращения 16 и «Управление внешнее 17, блок 18 управления буферной памятью и блоки синхронизации 19, приоритетного выбора 20, управления подканалом 21.

Блок 5, состояший из логических элементов И, ИЛИ и триггера, предназначен для организации приема управляющего слова в регистры конечного 6 и текущего 7 адресов.

Блок 4 представляет собой ряд регистров, связанных между собой цепями приема-передачи, предназначенных для преобразования формата обмениваемых данных, а также для синхронизации потоков данных «буферная память и «буферная память-ОЗУ.

Блок 9, содержащий схему поразрядного сравнения содержимого регистров конечного адреса и текущего адреса, выполненную на логических элементах И-ИЛИ-НЕ и И, служит для выработки сигнала при совпадении адресов, содержапшхся в указанных регистрах.

Блок 10 унравления обменом, состоя1ций из триггеров и логических элементов И, ИЛИ, НЕ, нредназначен для выполнения инструкций обращения к оконечному устройству 13, реализации управляющих последовательностей сигналов, управления потоком данных между блоком 1 памяти и оконечным устройством 13.

Блок 21 управления подканалом, содержащий триггеры и логические элементы И, ИЛИ, НЕ, служит для организации выполнения двух основных функций: передачи в блок 13 команды, которая читается из ячейки блока 1 по адресу, выдаваемому блоком 13, и смены управляющего слова в регистрах конечного и текущего адресов по сигналу из блока 13, причем адрес нового управляющего слова также выдается блоком 13.

Блок 19, содержащий триггеры и схемы опроса этих триггеров, предназначен для синхронизации сигналов, поступающих асинхронно из блока 13. Блок 13 сопряжения предназначен для подключения к устройству для обмена данными устройств ввода-вывода, имеющих интерфейс ввода-вывода, расширенный по сравнению с интерфейсом данной вычислительной машины.

Нри работе устройства для обмена данными с блоком сопряжения используется программа канала, хранящаяся в блоке 1. Она представляет собой последовательную запись комапд и управляющих слов. Ее выполнение инициируется инструкцией обращения к блоку 13.

Устройство работает лседующим образом. В процессе выполнения инструкции обращения к блоку 13 из процессора в блок 10 управления обменом по шине 11 «Управление поступают сигналы, по которым производится прием управляющего слова в регистры текущего 7 и конечного 6 адресов. Блок 10 вырабатывает управляющую последовательность сигналов, поступающих по шине 12 «управление каналом в блок 13. В результате блок 13 настраивается на обмен информацией и получает адрес ячейки блока 1, в которой хранится начальный адрес программы канала.

Обмен данными производится по запросам,

поступающим в блок 18 управления буферной намятью из блока 13 по шине 17« Управление внешнее. По одному запросу производится обмен единицей данных по реверсивной шине 14 «Данные между блоком 13 и блоком

4 буферной памяти. Обмен данными между блоками 4 и 1 организуется блоком 10 по адресу, содержащемуся в регистре 7. В процессе обмена данными блок 10 производит модификацию адреса. Обмен данными нродолжается

до тех пор, пока текущий адрес обмена не достигнет значения конечного адреса обмена. В этом случае блок 9 сравнения выдает в блок 10 сигнал совпадения, а блок 10 по шине 12 передает в блок 13 сигнал об окончании обмена данными, заданного управляющим словом массива. Блок 13 реагирует на этот сигнал двояко.

В случае отсутствия признака выполнения следующей команды программы канала блок

13 выдает в блок 10 унравления обменом сигнал об окончании работы, поступающий по шине 17 через блок 19 синхронизации и блок 20, после чего обмен информацией заканчивается. Нри наличии признака выполнения следующей команды программы канала блок 13 вырабатывает сигнал смены управляюн1его слова, который после синхронизации, в случае отсутствия более приоритетных сигналов, требующих обработки, поступает в блок 21

управления подканалом и выдает на шину 16 «Адрес обращения адрес нового управляющего слова. В этом случае блок 21 запускает блок 1 памяти на чтение, выдает сигнал в коммутатор адресов 8, по которому последний

соединяет шину 16 с блоком 1. Считанное таКИМ образом новое управляющее слово через блок 5 подается в регистры конечного 6 и текущего 7 адресов. После этого блок 21 вырабатывает сигнал, по которому блок 10 управления обменом начинает генерировать управляющую последовательность сигналов, поступающую по шине 12 «Управление каналом в блок 13, для подготовки к обмену данными по новому управляющему слову. Команду, соответствующую новому управляющему слову, блок 13 полчает во время обмена данными по предыдущей команде. Для получения этой команды блок 13 выдает сигнал запроса, поступающий в блок 19 синхронизации, и адрес команды на шину 16 «Адрес обращения.

В случае отсутствия запроса от блока 18 управления буферной памятью блок 20 приоритетного выбора вырабатывает сигнал, поступающий в блок 21 управления подканалом, который в свою очередь запускает блок 1 на чтение и вырабатывает сигнал, по которому коммутатор адресов 8 подключает шину 16 к блоку 1. Считанная команда по информационной шине 2 через блок 3 согласования выдается на шину 15, по которой она поступает в блок 13. Эта команда хранится в блоке 13 до окончания обмена текущего массива данных, затем как было описано выше в регистры 7 и 6 текущего и конечного адресов принимается управляющее слово, соответствующее принятой команде, и начинается ее выполнение. После того как программа канала выполнена полностью, блок 13 вырабатывает сигнал об окончании работы, который поступает в блок 10 управления обменом. По этому сигналу блок 10 выдает на шину 11 «Управление сигнал прерывания, поступающий в процессор, который озпачает, что программа канала выполнена полностью.

Формула изобретения

Устройство для обмена данными, содержащее блоки памяти, приема управляюп1,сго слова, буферной памяти, сравнення, приоритетпого выбора, управления буферной памятью, синхронизации, сопряжения, регистры текущего и конечного адресов, коммутатор адресов, нричем блок памяти соединен информационной шиной с блоком буферной памяти и блоком приема управляюпд,его слова, выход которого подключен к входам регистров текущего и конечного адресов, выходы которых соединены с соответствующими входами блока

сравнения, управляющий выход блока сопряжения подключен к первому входу блока синхронизации и входу блока управления буферной памятью, первый и второй выходы которого подключены соответственно к управляющему входу блока буферной памяти и второму входу блока синхронизации, выход которого соединен с входом блока приоритетного выбора, блок сопряжения соединен двусторонними связями с блоком буферной памяти, первый вход коммутатора адресов соединен с соответствующим выходом регистра текущего адреса, выход подключен к адресиому входу блока памяти, отличающееся тем, что, с целью повышения эффективности работы устройства, в него введены блоки управления подканалом, согласовання и блок управления обменом, первый вход которого соединен с первым выходом блока приоритетного выбора, выходы подключены соответственно к первым

входам блоков памяти, приема управляющего слова, сопряжения и уиравляющему входу регистра текущего адреса, второй выход блока приоритетного выбора соединен с входом блока управлеппя подканалом, выходы которого

подключены соответственно к вторым входам блоков памяти, приема управляющего слова, управления обменом и коммутатора адресов, третий вход которого подключен к выходу блока сонряжепия, выход блока сравнения соеднней с третьим входом блока управления обменом, соединенного с управляюпи-вш входом и выходом устройства, вход блока согласования подключен к информационной ninne, выход - к второму входу блока сопряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для сопряжения | 1978 |

|

SU813401A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для сопряжения устройств ввода-вывода с цвм | 1974 |

|

SU736083A1 |

| Устройство для сопряжения | 1978 |

|

SU809139A2 |

| Устройство для сопряжения | 1984 |

|

SU1166126A2 |

| Мультиплексный канал | 1980 |

|

SU879580A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

Авторы

Даты

1976-03-15—Публикация

1974-09-12—Подача