зэ

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для управления каналами | 1976 |

|

SU641436A1 |

| Устройство для управления каналами | 1974 |

|

SU520592A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1256036A1 |

| Устройство управления каналами | 1973 |

|

SU518769A1 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

Изобретение относится к области вычислительной техники и может быть использовано в системах ввода-вывода электронно-вычислительных машин. Целью изобретения является повышение быстродействия. Устройство содержит блок 1 управления, блок 2 обмена информацией, блок 3 счета байтов, блок 4 задания режима работы, блок 5 запроса загрузки, блок 6 задания характеристик, блок 7 элементов И, блок 8 регистров, блок 9 формирования команд, узел 10 триггеров, узел 11 маски. 1 з.п. ф-лы, 13 ил.

со

00 00 00

00

Изобретение относится к вычислительной технике и может быть использовано в системах ввода-вывода электронных вычислительных машин (ЭВМ).

Цель изобретения - повышение быстродействия устройства для сопряжения ЭВМ с внешним устройством (в дальнейшем устройства) за счет организации блочного обмена данными при передаче информации между устройством и оперативной памятью по одной команде ввода-вывода, когда несколько передаваемых блоков данных заданного фиксированного объема располагаются в не- смежных областях оперативной памяти, что достигается за счет организации .контроля конца передачи обменного I массива заданного объема, позволяюще- I го хранить в оборудовании устройства минимальный объем следующей исполь- ; зуемой управляющей информации, за счет чего скорость передачи данных I для разных массивов сохраняется такой ;же, как и скорость передачи данных внутри одного обменного массива, что позволяет увеличить общую скорость :передачи данных между устройством и оперативной памятью и реализовать страничную организац:ию оперативной памяти,

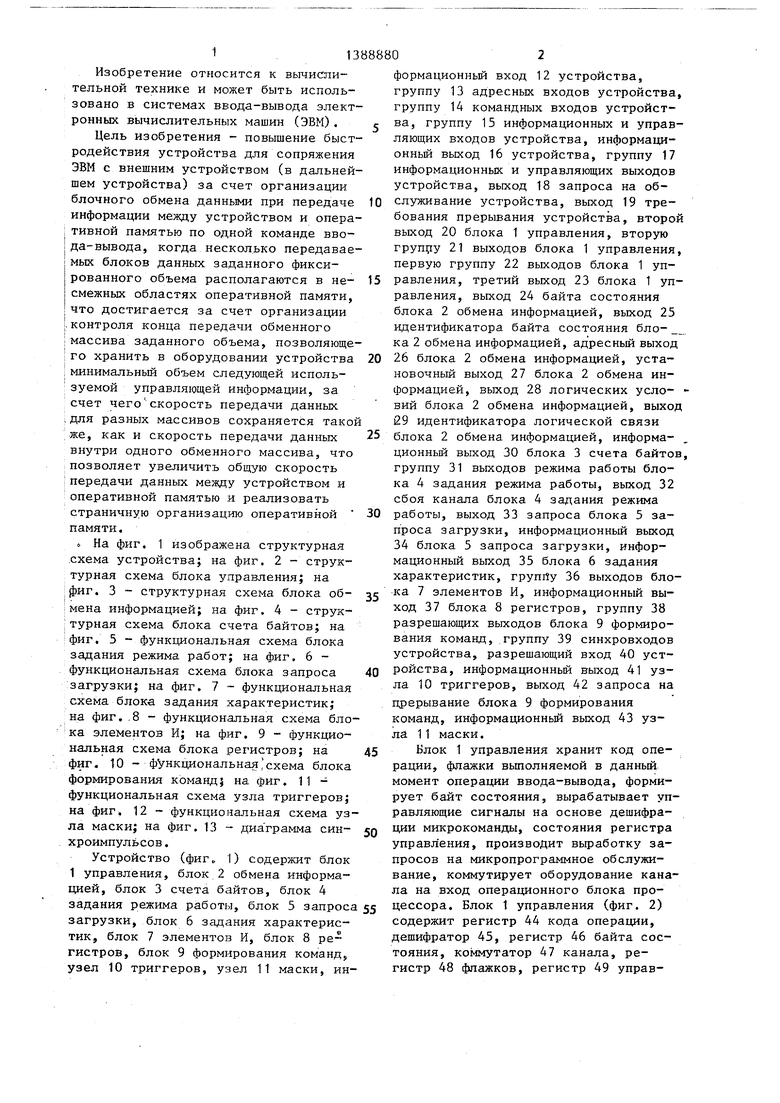

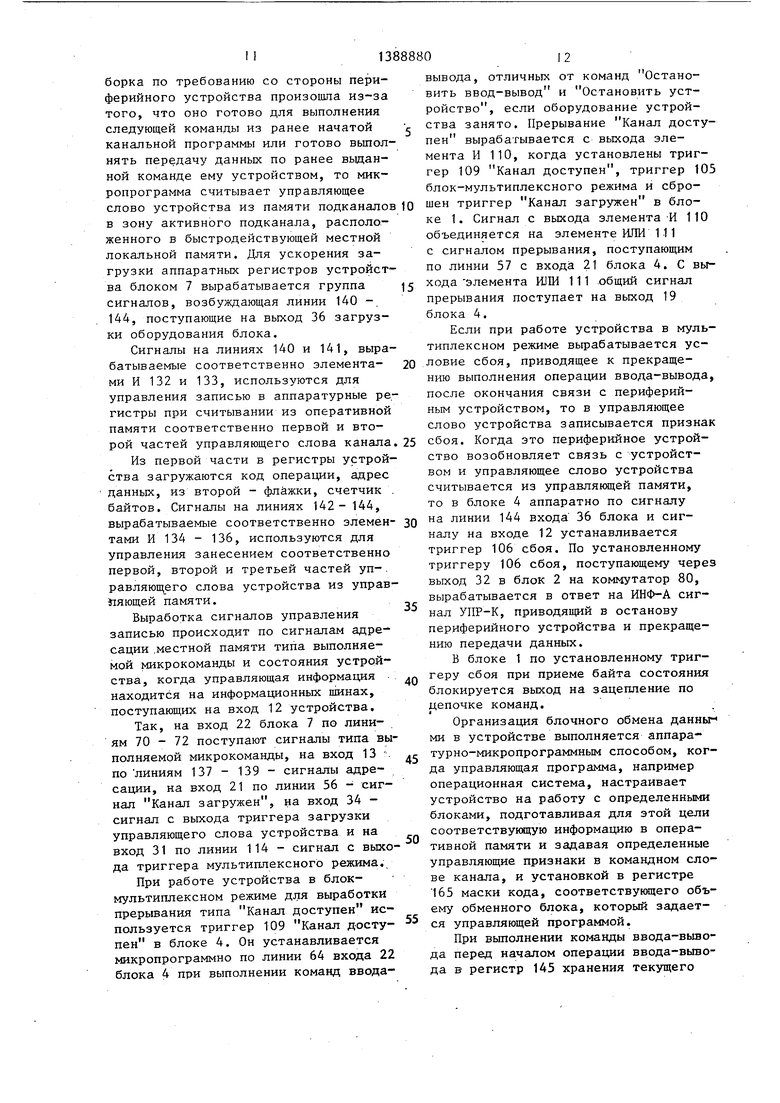

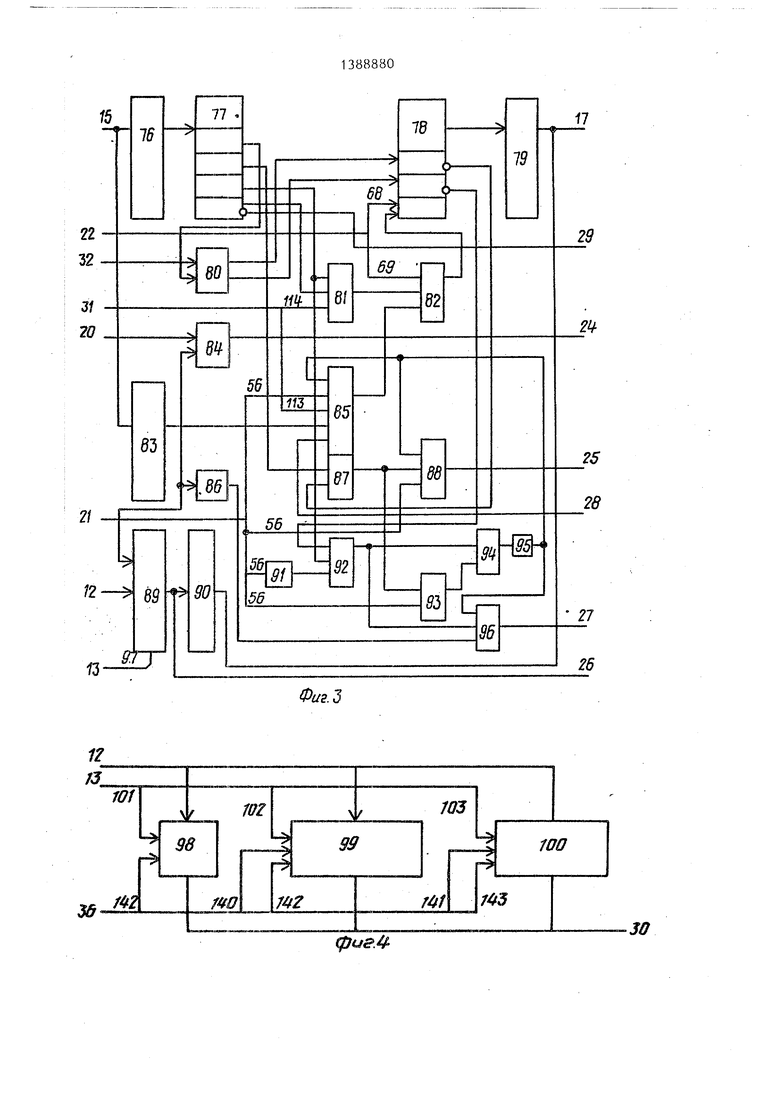

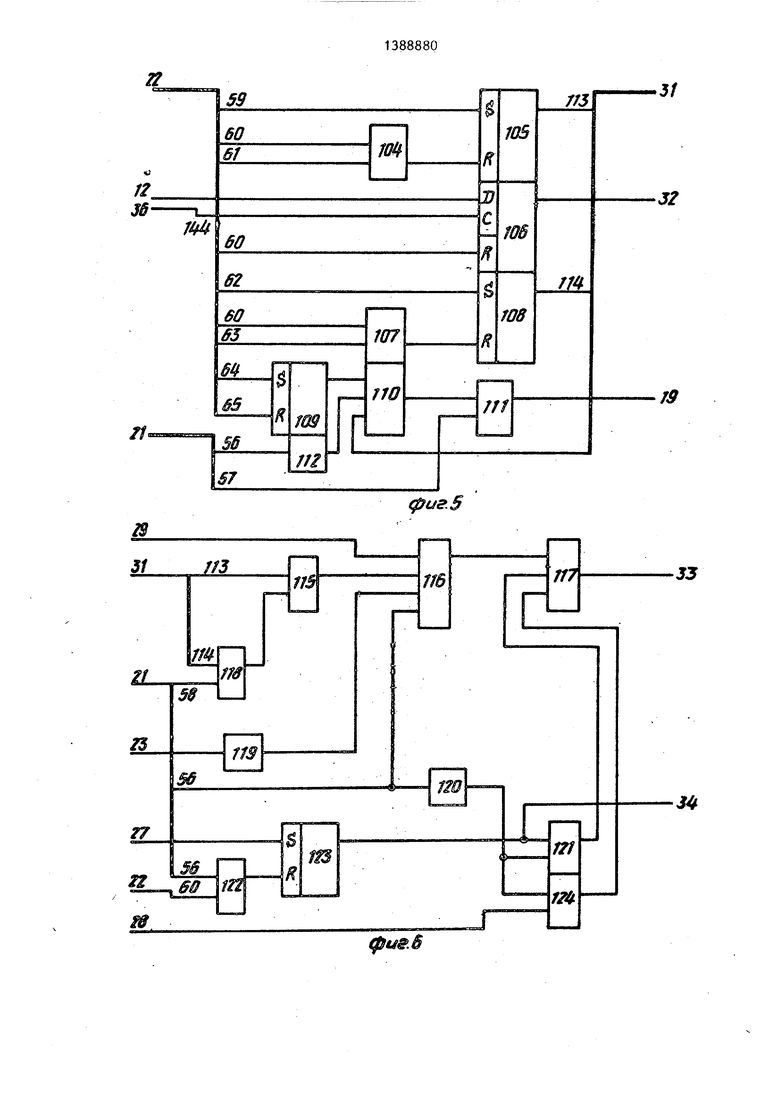

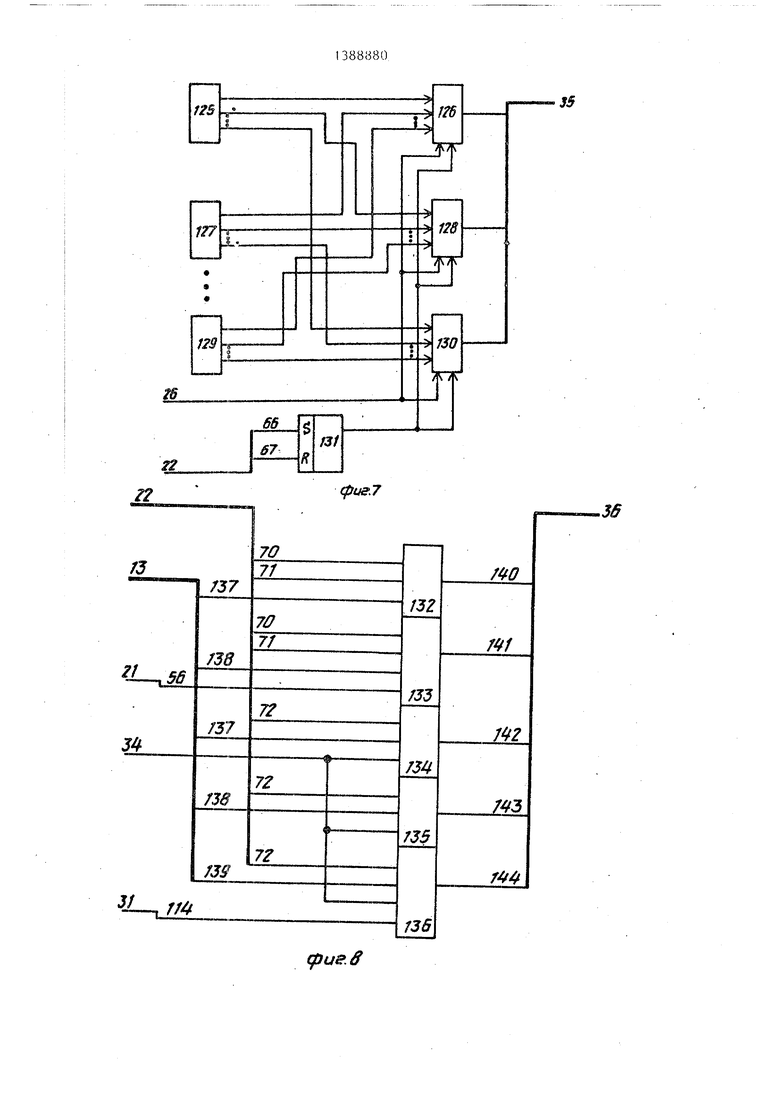

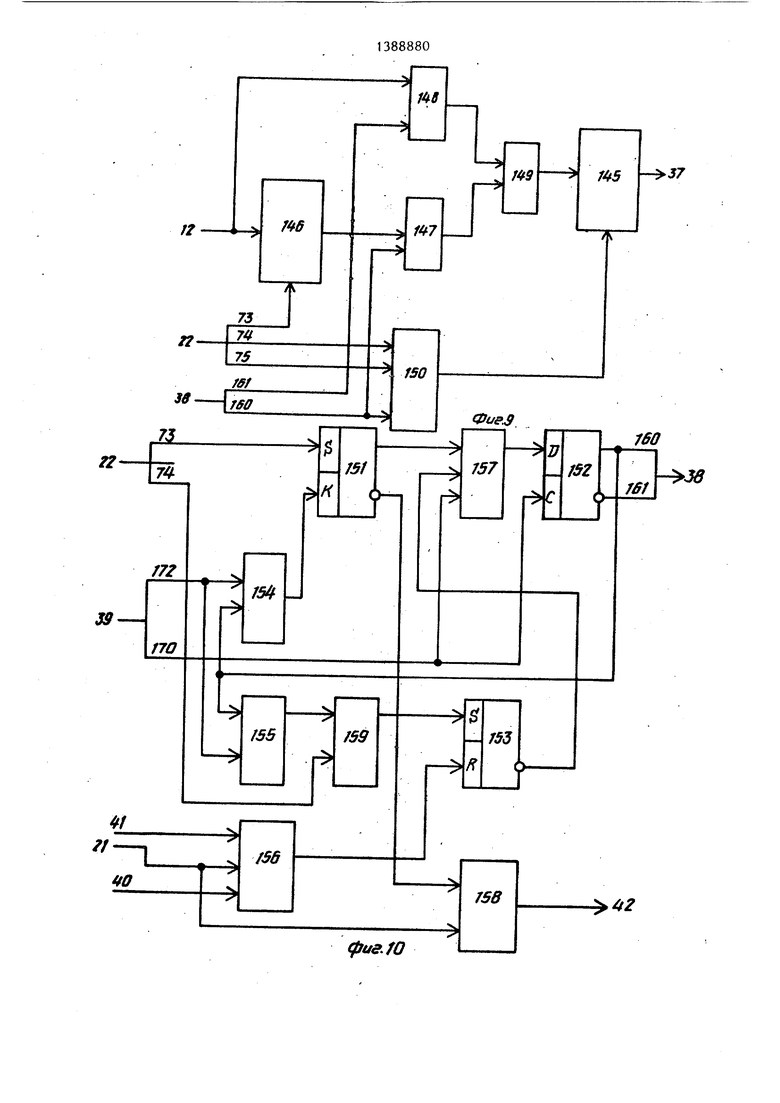

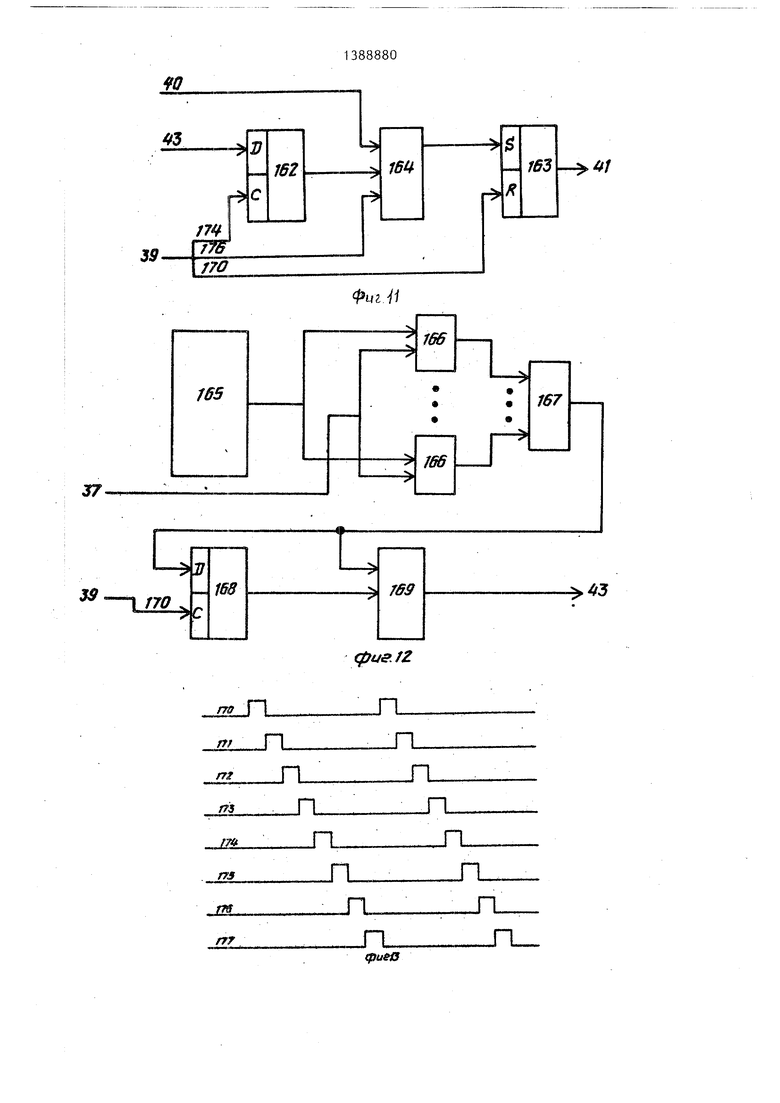

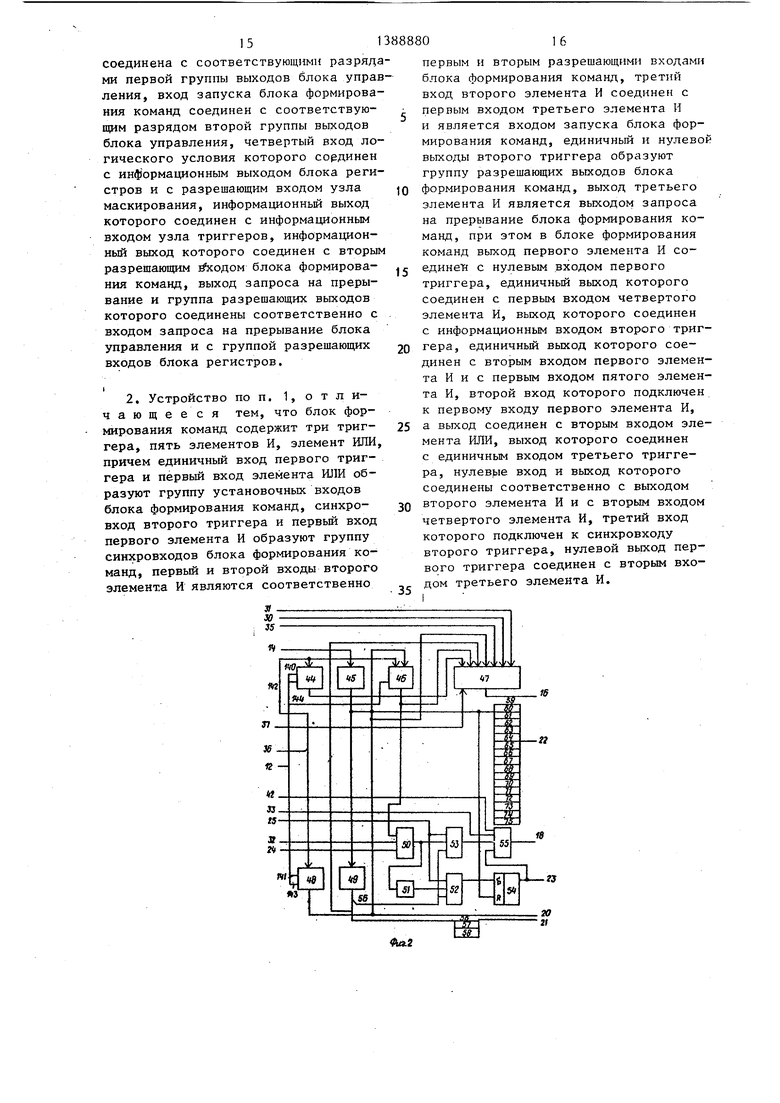

На фиг. 1 изображена структурная .схема устройства; на фиг, 2 - структурная схема блока управления; на ;0иг. 3 - структурная схема блока об- iмена информацией; на фиг. 4 - струк- ;турная схема блока счета байтов; на ;фиг. 5 - функциональная схема блока задания режима работ; на фиг. 6 - функциональная схема блока запроса загрузки; на фиг. 7 - функциональная схема блока задания характеристик; на фиг. ,8 - функцион альная схема блока элементов И; на ф.иг. 9 - функциональная схема блока регистров; на фиг. 10 - функциональная;схема блока формирования команд} на фиг. 11 - функциональная схема узла триггеров; на фиг. 12 - функциональная схема узла маски; на фиг. 13 - диа грамма син- хроимпульсов.

Устройство (фиг., 1) содержит блок 1 управления, блок 2 обмена информацией, блок 3 счета байтов, блок 4 задания режима работы, блок 5 запроса загрузки, блок 6 задания характеристик, блок 7 элементов И, блок 8 регистров, блок 9 формирования команд, узел 10 триггеров, узел 11 маски, PIH

0 5 0 5 0

5 Q

5

5

0

формационньй вход 12 устройства, группу 13 адресных входов устройства, группу 14 командных входов устройства, группу 15 информационных и управляющих входов устройства, информаци- онньш выход 16 устройства, группу 17 информационных и управляющих выходов устройства, выход 18 запроса на обслуживание устройства, выход 19 требования прерывания устройства, второй выход 20 блока 1 управления, вторую групцу 21 выходов блока 1 управления, первую группу 22 выходов блока 1 управления, третий выход 23 блока 1 управления, выход 24 байта состояния блока 2 обмена информацией, выход 25 идентификатора байта состояния бло- ка 2 обмена информацией, адресный выход 26 блока 2 обмена информацией, установочный выход 27 блока 2 обмена информацией, выход 28 логических уело- - ВИЙ блока 2 обмена информацией, выход 29 идентификатора логической связи блока 2 обмена информацией, информа- ционньй выход 30 блока 3 счета байтов, группу 31 выходов режима работы блока 4 задания режима работы, выход 32 сбоя канала блока 4 задания режима работы, выход 33 запроса блока 5 запроса загрузки, информационный выход 34 блока 5 запроса загрузки, информационный выход 35 блока 6 задания характеристик, групйу 36 выходов блока 7 элементов И, информационный выход 37 блока 8 регистров, группу 38 разрешающих выходов блока 9 формирования команд, группу 39 синхровходов устройства, разрешающий вход 40 устройства, информационный выход 41 узла 10 триггеров, выход 42 запроса на прерывание блока 9 формирования команд, информационньй выход 43 уз- лй 11 маски.

Блок 1 управления хранит код операции, флажки вьшолняемой в данный момент операции ввода-вывода, формирует байт состояния, вырабатывает управляющие сигналы на основе дешифрации микрокоманды, состояния регистра управл ения, производит вьфаботку запросов на микропрограммное обслуживание, коммутирует оборудование канала на вход операционного блока процессора. Блок 1 управления (фиг. 2) содержит регистр 44 кода операции, дешифратор 45, регистр 46 байта состояния, коммутатор 47 канала, регистр 48 флажков, регистр 49 управления, элемент ШШ 50, элемент НЕ 51, элементы И 52 и 53, триггер 54, элемент ИЛИ 55, выходы 56-58 второй группы 21 выходов, выходы 59-75 первой группы 21 выходов.

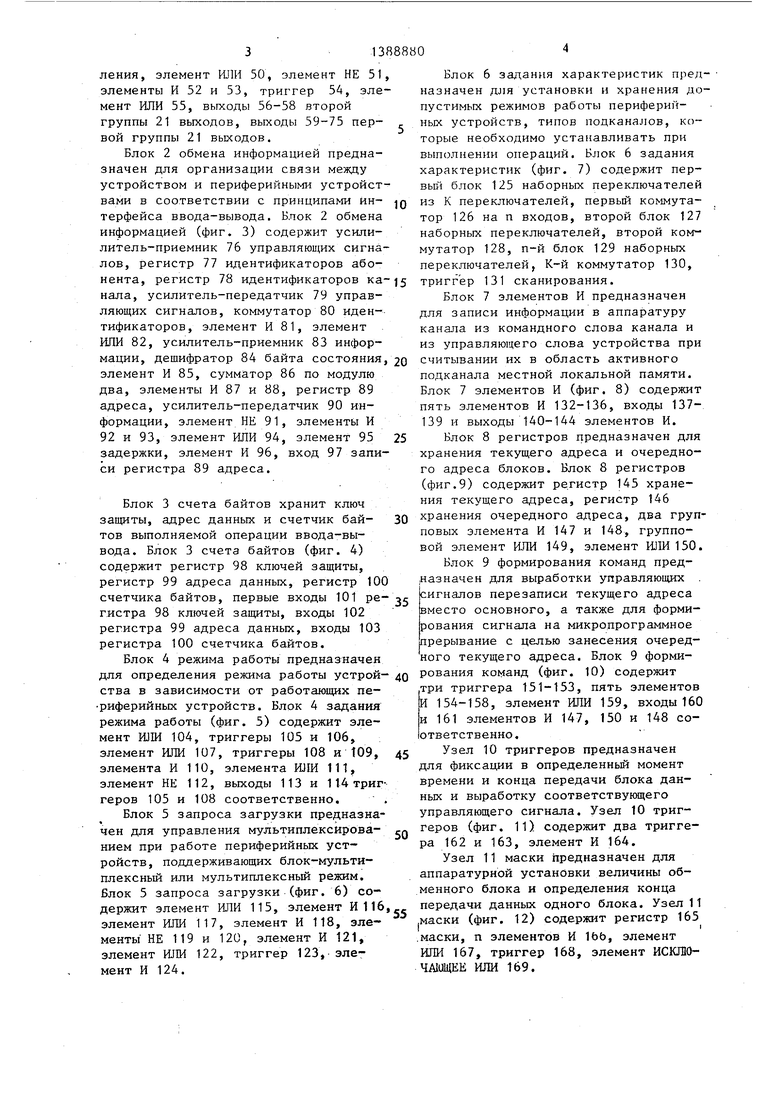

Блок 2 обмена информацией предназначен для организации связи между устройством и периферийными устройствами в соответствии с принципами ин- Qиз К переключателей, первый коммутатерфейса ввода-вывода. Блок 2 обменатор 126 на п входов, второй блок 127

информацией (фиг. 3) содержит усили-наборных переключателей, второй комлитель-приемник 76 управляющих сигна-мутатор 128, п-й блок 129 наборных

лов, регистр 77 идентификаторов або-переключателей, К-й коммутатор 130,

нента, регистр 78 идентификаторов ка-15триггер 131 сканирования, нала, усилитель-передатчик 79 управ- Блок 7 элементов И предназначен

ляющих сигналов, коммутатор 80 иден-для записи информации в аппаратуру

тификаторов, элемент И 81, элементканала из командного слова канала и

ИЛИ 82, усилитель-приемник 83 инфор-из управляющего слова устройства при

мации, дешифратор 84 байта состояния, 20считывании их в область активного

элемент И 85, сумматор 86 по модулю два, элементы И 87 и 88, регистр 89 адреса, усилитель-передатчик 90 информации, элемент НЕ 91, элементы И 92 и 93, элемент ИЛИ 94, элемент 95 задержки, элемент И 96, вход 97 записи регистра 89 адреса.

Блок 3 счета байтов хранит ключ защиты, адрес данных и счетчик байтов выполняемой операции ввода-вывода. Блок 3 счета байтов (фиг. 4) содержит регистр 98 ключей защиты, регистр 99 адреса данных, регистр 100

подканала местной локальной памяти. Блок 7 элементов И (фиг. 8) содержит пять элементов И 132-136, входы 137- 139 и выходы 140-144 элементов И.

25 Блок 8 регистров предназначен для хранения текущего адреса и очередного адреса блоков. Блок 8 регистров (фиг.9) содержит ре.гистр 145 хранения текущего адреса, регистр 146

30 хранения очередного адреса, два групповых элемента И 147 и 148, групповой элемент ИЛИ 149, элемент ИЛИ 150.

Блок 9 формирования команд предназначен для выработки управляющих

сигналов перезаписи текущего адреса вместо основного, а также для формирования сигнала на микропрограммное прерывание с целью занесения очередного текущего адреса. Блок 9 формисчетчика байтов, первые входы 101 ре- 35 гистра 98 ключей защиты, входы 102 регистра 99 адреса данных, входы 103 регистра 100 счетчика байтов.

Блок 4 режима работы предназначен для определения режима работы устрой- до Рования команд (фиг. 10) содержит ства в зависимости от работающих пе- три триггера 151-153, пять элементов риферийных устройств. Блок 4 задания режима работы (фиг. 5) содержит элемент ШЖ 104, триггеры 105 и 106, элемент ИЛИ 107, триггеры 108 и 109, 45 элемента И 110, элемента ИЛИ 111, элемент НЕ 112, выходы 113 и 114 триггеров 105 и 108 соответственно.

Блок 5 запроса загрузки предназначен для управления мультиплексирова- Q геров (фиг. 11) содержит два тригге- нием при работе периферийных уст- ра 162 и 163, элемент И 164.

Узел 11 маски предназначен для аппаратурной установки величины обИ 154-158, элемент ИЛИ 159, входы 160 и 161 элементов И 147, 150 и 148 соответственно.

Узел 10 триггеров предназначен для фиксации в определенньй момент времени и конца передачи блока данных и выработку соответствующего управляющего сигнала. Узел 10 тригменцого блока и определения конца

ройств, поддерживающих блок-мультиплексный или мультиплексный режим. Блок 5 запроса загрузки (фиг. 6) содержит элемент ИЛИ 115, элемент И116,- передачи данных одного блока. Узел 11 элемент ИЛИ 117, элемент И 118, эле- маски (фиг. 12) содержит регистр 165 менты НЕ 119 и 120, элемент И 121, .маски, п элементов И Ibb, элемент элемент ШШ 122, триггер 123, эле- ИЛИ 167, триггер 168, элемент ИСКШО- мент И 124.Ч МиЩЕЕ ШШ 169.

Блок 6 задания характеристик пред- назначен для установки и хранения допустимых режимов работы периферийных устройств, типов подканалов, которые необходимо устанавливать при выполнении операций. Блок 6 задания характеристик (фиг. 7) содержит пер- вьш блок 125 наборных переключателей

подканала местной локальной памяти. Блок 7 элементов И (фиг. 8) содержит пять элементов И 132-136, входы 137- 139 и выходы 140-144 элементов И.

Блок 8 регистров предназначен для хранения текущего адреса и очередного адреса блоков. Блок 8 регистров (фиг.9) содержит ре.гистр 145 хранения текущего адреса, регистр 146

хранения очередного адреса, два групповых элемента И 147 и 148, групповой элемент ИЛИ 149, элемент ИЛИ 150.

Блок 9 формирования команд предназначен для выработки управляющих

сигналов перезаписи текущего адреса вместо основного, а также для формирования сигнала на микропрограммное прерывание с целью занесения очередного текущего адреса. Блок 9 формиРования команд (фиг. 10) содержит три триггера 151-153, пять элементов

Рования команд (фиг. 10) содержит три триггера 151-153, пять элементов

геров (фиг. 11) содержит два тригге- ра 162 и 163, элемент И 164.

И 154-158, элемент ИЛИ 159, входы 160 и 161 элементов И 147, 150 и 148 соответственно.

Узел 10 триггеров предназначен для фиксации в определенньй момент времени и конца передачи блока данных и выработку соответствующего управляющего сигнала. Узел 10 тригменцого блока и определения конца

передачи данных одного блока. Узел маски (фиг. 12) содержит регистр 1 .маски, п элементов И Ibb, элемент ИЛИ 167, триггер 168, элемент ИСКШ Ч МиЩЕЕ ШШ 169.

На фиг. 13 представлены синхросигналы 170-177.

Предлагаемое устройство может применяться в системах ввода-вывода ЕС ЭВМ. Устройство может подключаться непосредственно к центральному процессору или входить как один из каналов в состав процессора ввода-вывода

Центральный процессор управляет работой устройства с помощью специальных команд ввода-вывода. Обра;ще- ние к программе канала осуществляегт- ся с помощью адресного слова канала, расположенного в фиксированной ячей- ке оперативной памяти. Адресное слово канала содержит ключ защиты и адрес первого управляющего слова канала. Программа канала состоит из последовательности управляющих слов канала. Управляющее слово канала содержит код выполняемой операции в/в, начальный адрес данных, признаки режима работы канала и правила выборки следующего управляющего слова канала (ф-пажки) , длину массива (счетчик байтов ) . В состав устройства входят логические схемы, регистры, счетчики, позволяющие хранить информацию с выполняемой операции ввода-вывода .

Так как оборудование устройства разделяется во времени несколькими операциями ввода-вывода, то управляющая информация об операциях ввода- вывода хранится в областях управляющей или оперативной памяти центрального процессора, называемой подканалами. В подканале хранятся код операции, адрес данных, (флажки, счетчик байтов, ключ защиты памяти, состояни канала, адрес следующего управляющег слова канала. Эта управляющая информация называется управляющим словом устройства.

Так как в устройстве исполь зуется комбинированное аппаратно-микропро- граммное управление, то для устройства, кроме логических схем, регистров и счетчиков выделяется область быстродействующей местной памяти, в которой хранится управляющее слово устройства для активного подканала, т.е подканала, связанного логически в данный момент с устройством. Эта информация отражает условия завершения начальной выборки, текущее состояние или условия отсоединения периферий - ного устройства при последовательности окончания. В процессе передач

o

0

5

г

/Q

0

}5

5

0

5

, продвижения по канальной программе управляющее слово устройства обновляется. Если устройство работает селекторном режиме, то управляющая информация хранится в его регистрах в теление всего времени выполнения операции ввода-вывода, поскольку се- лекторньй режим имеет только один подканал и навязывает периферийному устройству монопольный режим .

Б мультиплексном и блок-мультиплексном режимах устройство способно обслуживать несколько периферийных устройств, для каждого из которых назначен свой подканал.

В устройстве управляющая информация хранится в регистре 44 кода операции, регистре 48 флажков, регистре 46 байта состояния блока 1 управления, в регистре 78 ключей защиты, регистре 99 адреса данных, регистре 1UU счетчика байтов блока 3 счета байтов. Загрузка информации в зти регистры может производиться во время выполнения соответствующей микропрограммы с помощью сигналов адресации и входных информационных шин, поступающих в устройство соответственно через входы 13 и 12.

Микропрограммное управление устройством осуществляется посредством сигналов с выхода дешифратора 45. С помощью сигналов, возбуждающих линии 59-69 выхода 22 блока 1. управления, производятся микропрограммная установка и сброс триггеров в других блоках устройства. По сигналам на линиях 70-75 этого же выхода блока выполняются действия по загрузке оборудования устройства, связанные с выполнением определенных микрокоманд. При выполнении микрокоманды чтения данньк устанавливается сигнал на линии 70, при микрокоманде обращения к оперативной памяти - на линии 71, при микрокоманде обращены к управляю- щей памяти - на линии 72.

Микропрограммно устанавливаются и сбрасываются триггеры регистра 49 управления блока 1 управления. К этим триггерам относятся следующие: триггер Канал загрузки - линия 56 выхода 21 блока 1 управления, триггер прерывания - линия 57 того же выхода блока, триггер действительности адреса данных - линия 58.

Триггер Канал загружен устанавливается с момента выполнения опера15

20

ции ввода-вывода с использованием оборудования устройства. Триггер пре-. рывания устанавливается, когда в устройстве или на нерифериГпюм устрой- стве, подключенном к этом устройству, хранится прерывание. Триггер действительности адреса данных указывает, что в регистре 89 адреса.находится действительный адрес. Этот триггер Q устанавливается, когда выполняется микропрограмма загрузки адреса данных, а сбрасывается, когда при передаче данных использование адреса даных ограничивается обменом определенного объема данных, определяемым по изменению соответствующего разряда адреса данных (например, страничный обмен при косвенной адресации в устройстве) .

В регистре 46 байта состояния блоа 1 фиксируются ошибки в управляющей информации канальной программы, ошиби в работе оборудования устройства.

Микропрограммный анализ регистров 25 стройства и отдельных триггеров, объединенных в регистры, производится в операционном блоке процессора через- коммутатор 47 канала, выход которого соединен с выходом 16 устройства. ,Q

Условия запросов на микропрограм- ное обслуживание поступают на выход 18 устройства с выхода элемента ИЛИ 55. В блоке 1 управления вырабатываются запросы на микропрограммное обслуживание по приходу байта состояния пе- риферийного устройства при завершении операции ввода-вывода и зацеплении по цепочке команд.

Запрос по цепочке команд с выхода триггера 54 поступает на выход 18 блока 1 управления. Условия установки запросов этих типов вырабатываются в блоке 2 дешифратором 84 байта состояния и элементов И 88, который выдает сигнал на выходе 25 блока 2 после отработки элемента 95 задержки при загруженном устройстве.

Для работы дешифратора 84 байта состояния из блока 1 через выход 20 в дешифратор 84 байта состояния вы- даются состояния регистра 48 флажков. Через блок 2 устройство соединяется с периферийным устройством. На усилители-приемники управляющих сигналов 76- и информации 83 поетупают сигналы 55 интерфейса от периферийных устройств через вход 15 устройства. Усилители- передатчики 79 управляющих сигналов

40

45

5

20

. Q

5 ,Q

5

0

5

и информации 90 соединены с выходом 17 ycTpoiicTBa. В регистре 89 ал,реса хранится адрес перифери11ного устройства, который загружается микропрограммно при выполнении команды ввода- вывода или аппаратурно при связи по инициативе периферийного устройства. Регистр 78 идентификаторов канала используется для управления последовательностями интерфейса. Прием байта состояния периферийного устройства в блок 2 осуществляется с помощью элементов И 87 и 88, элемента НИИ 94 и элемента 95 задержки. Прием адреса периферийного устройства производится с помощью элементов И 92, элемен-- та ИЛИ 94 и элемента 95 задержки. Но сигналу с выхода элемента 95 задержки производится анализ информации на выходах усилителей-приемников информации и контроль ее по паритету путем сложения по модулю 2 элементом 86.

После сброса системы устройство находится в исходном состоянии и готово к выполнению операции ввода-вывода в одном из трех режимов: блок- ryльтиJплeкcнoм, селекторном или мультиплексном. В устройстве имеется блок 6 задания характеристик, на блоках наборных переключателей 125, 127 и 129 которого на группы периферийных устройств, имеющих по.следователь- ные адреса, набираются характеристики периферийных устройств.С помощью переключателей можно задать режим работы, которьш должен поддерживаться устройством, тип подканала и другие характеристики. Через группу коммутаторов 126, 128 и 130 блока 6 задания характеристик, управляемых с помощью триггера 131 сканирования и соответствующей константы, в регистре 89 адреса блока 2 происходит считывание состояний блоков 125, 127 и 129 наборных переключателей по группам адресов периферийных устройств через коммутатор 47 канала блока 1 в управ- ляющую память процессора. В результате в управляющей памяти процессора формируется таблица указателей характеристик периферийных устройств. Эта процедура формирования таблицы характеристик производится во время выполнения микропрограммы сброса системы.

Режим работы, в котором должно находиться устройство, определяется на основе таблицы характеристик по

9 ;13

адресу периферийного устройства JEIO время выполнения ввода-вывода Начать ввод-вывод. При запуске периферийного устройства, работающег в мультиплексном режиме, микропрограммно устанавливается триггер 108 мультиплексного режима блока 4. Если периферийное устройство поддерживает блок- мультиплексный режим и нулевой бит нулевого управляющего регистра процессора в единичном состоянии, то микропрограммно устанавливается триггер 105 блок-мультиплексного режима. При работе устройства в селекторном режиме триггеры мультиплексного и блок-мультиплексного режиме сброшены

Режим работы устройства управляет продолжительностью связи по интерфейсу ввода-вывода между устройством и периферийньм устройством, формированием запроса на запоминание управляющего слова устройства в управляющую память процессора или формированием запроса на загрузку управляющего уст ройства в оборудование устройства.

Продолжительность связи по интерфейсу ввода-вывода определяется устройством и периферийным устройством.

Возможность управления длитель- . ;нрстью связи со стороны устройства обеспечивается триггером ВБР-К регистра 78 идентификаторов канала блока 2. Периферийное устройство не может прерывать связь и отключаться от инферфейса ввода-вывода до тех пор, пока канал не сбросит ВБР-К. Периферийное -устройство поддерживает связь с устройством после сброса ВБР-К до тех пор, пока текущая последовательность сигналов интерфейса ввода-вывода. не будет зако.нчена. Триггер ВБР-К сбрасывается через элемент ИЛИ 82 блока 2 микропрограммно по сигналу на линии ,69, в блок-мультиплексном режиме сбрасывается по сигналу с выхода элемента И 85, в мультиплексном режиме- по сигналу с выхода элемента И 81„ При работе устройства в блок-мультиплексном режиме сигнал сброса триггера ВБР-К появляется по приему байта состояния с признаком Канал кончил Это позволяет освобождать устройство при выполнении цепочки команд после приема байта состояния Канал кончил

При работе устройства в мультиплексном режиме триггер ВБР-К сбраеы1вается во время выполнения начальной выборки по приходу сигнала АДР-А.

0

5

880

0 5

0

5

0

5

0

5

10

Если устройство работает в селекторном режиме, то при цепочке команд периферийное устройство остается подключенным к устройству до приема состояния с признаком Устройство кончило.

Таким образом, в мультиплексном режиме периферийное устройство может отсоединиться от устройства в течение выполнения команды канала, d в блок- мультиплексном режиме - только после выполнения передачи всех данных по текущему управляющему слову какала. Отсоединение периферийного устройства позволяет освободить устройство для выполнения других операций ввода- вывода .

Запрос на запоминание управляющего слова устройства в память подканалов вырабатывается элементами И 116, 1ШИ 115, И 118, элементом НЕ 119 блока 5. При этом оборудование устройства должно быть загружено, не должно быть запроса на зацепление по цепочке команд, и связь с периферийным устройством закончена. Эти условия обеспечиваются установленным триггером Канал загружен в блоке 1, сброшенным триггером РАБ-А в регистре 77 идентификаторов абонента блока 2, сброшенным триггером 54 блока 1. При этом для мультиплексного режима триггер действительности адреса регистра 49 управления блока 1 должен быть установлен.

Во время выборки по требованию в результате приема адреса периферийного устройства без сбоя по паритету на выходе элемента И 96 блока 2 вырабатывается сигнал установки тригге-г . ра 123 загрузки управляющего слова устройства. Этот сигнал поступает в блок 5 запроса загрузки с выхода 27 блока 2 о По этому сигналу при сброшенном триггере Канал загружен на выходе элемента И 121 вырабатывается запрос на загрузку управляющего слова устройства. Запрос этого же типа вырабатывается элементом И 124 по сигналу с выхода элемента И 87 блока 2 при условии, что устройство свободно. Это условие используется для обработки требования от периферийных устройств, для которых прерывание типа Канал кончил по завершении операции ввода-вывода уже обработано или Которые переводят из состояния Не

готов в состояние Готов. Если вы11

борка по требованию со стороны периферийного устройства произошла из-за того, что оно готово для выполнения следующей команды из ранее начатой канальной программы или готово выполнять передачу данных по ранее вьщан- ной команде ему устройством, то микропрограмма считывает управляющее

вывода, отличных от команд Остановить ввод-вывод и Остановить устройство, если оборудование устройства занято. Прерывание Канал досту пен вырабатывается с выхода элемента И 110, когда установлены триггер 109 Канал доступен, триггер 10 блок-мультиплексного режима и сброслово устройства из памяти подканалов 10 шен триггер Канал загружен в блоке 1. Сигнал с выхода элемента-И 110 объединяется на элементе ИЛИ 111 с сигналом прерывания, поступающим по линии 57 с входа 21 блока 4. С выхода элемента ИЛИ 111 общий сигнал прерывания поступает на выход 19 блока 4.

Если при работе устройства в мультиплексном режиме вырабатывается ус- соответственно элемента- 20 ловие сбоя, приводящее к прекращению выполнения операции ввода-вывода, после окончания связи с периферийным устройством, то в управляющее слово устройства записывается признак

в зону активного подканала, располо,- женного в быстродействующей местной локальной памяти. Для ускорения загрузки аппаратных регистров устройства блоком 7 вырабатывается группа 5 сигналов, возбуждающая линии 140 -. 144, поступающие на выход 36 загрузки оборудования блока.

Сигналы на линиях 140 и 141, вырабатываемые

ми И 132 и 133, используются для управления записью в аппаратурные регистры при считывании из оперативной памяти соответственно первой и второй частей управляющего слова канала. 25 сбоя. Когда это периферийное устрой30

35

40

Из первой части в регистры устройства загружаются код операции, адрес данных, из второй - флажки, счетчик . байтов. Сигналы на линиях 142- 144, вырабатываемые соответственно элементами И 134 - 136, используются для управления занесением соответственно первой, второй и третьей частей уп-. равляющего слова устройства из управляющей памяти.

Выработка сигналов управления записью происходит по сигналам адресации .местной памяти типа выполняемой микрокоманды и состояния устройства, когда управляющая информация - находится на информационных шинах, поступающих на вход 12 устройства.

Так, на вход 22 блока 7 по линиям 70 - 72 поступают сигналы типа выполняемой микрокоманды, на вход 13 . по линиям 137 - 139 - сигналы адресации, на вход 21 по линии 56 - сигнал Канал загружен, на вход 34 - сигнал с выхода триггера загрузки управляющего слова устройства и на вход 31 по линии 114 - сигнал с выхода триггера мультиплексного режима.

При работе устройства в блок- мультиплексном режиме для выработки прерывания типа Канал доступен используется триггер 109 Канал досту- пен в блоке 4, Он устанавливается микропрограммно по линии 64 входа 22 блока 4 при выполнении команд ввода45

50

ал-138888012

вывода, отличных от команд Остановить ввод-вывод и Остановить устройство, если оборудование устройства занято. Прерывание Канал доступен вырабатывается с выхода элемента И 110, когда установлены триггер 109 Канал доступен, триггер 105 блок-мультиплексного режима и сбро0

5

0

5

0

ство возобновляет связь с устройством и управляющее слово устройства считывается из управлянщей памяти, то в блоке 4 аппаратно по сигналу на линии 144 входа 36 блока и сигналу на входе 12 устанавливается триггер 106 сбоя. По установленному триггеру 106 сбоя, поступающему через выход 32 в блок 2 на коммутатор 80, вырабатывается в ответ на ИНФ-А сигнал УПР-К, приводящий в останову периферийного устройства и прекращению передачи данных.

В блоке 1 по установленному триггеру сбоя при приеме байта состояния блокируется выход на зацепление по цепочке команд.

Организация блочного обмена данны- ми в устройстве выполняется аппара- турно-микропрограммным способом, когда управляющая программа, например операционная система, настраивает устройство на работу с определенными блоками, подготавливая для этой цели соответствующую информацию в оперативной памяти и задавая определенные управляющие признаки в командном слове канала, и установкой в регистре 165 маски кода, соответствующего объему обменного блока, который задается управляющей программой.

При выполнении команды ввода-вывода перед началом операции ввода-вывода в регистр 145 хранения текущего

адреса, а затем в регистр 146 хранения очередного адреса записываются а|цреса текущего блока данных и оче- р;едного блока данных.. Эта запись выполняется путем дешифрации на дешифраторе 45 соответствующих микроко- записи 1 и записи 2, результа- ifoM которых являются управляющие сиг цалы на линиях 74 и 73 соответственно. По этим же сигналам устанавли- ается в исходное состояние блок 9 формирования команд. I После выполнения команды ввода-вы- иода начинает выполняться операция ивода-вывода, в процессе выполнения ноторой организуется обмен данными между устройством и оперативной па- фятью. При этом каждьм раз осуществ 1яется модификация адреса данных, рас-20 запроса на запись микропрограммным

25

30

доложенного в регистре хранения текущего адреса путем вьщачи микро- дрограммым. путем содержимого этого Регистра через коммутатор 47 на информационный выход 16 устр ойства и Приемом модифицированного адреса IB регистр 145 хранения текущего (адреса с информационного входа 12 Устройства по управляющему сигналу Записи по линии 75, который является результатом дешифрации соответствую- 1йей- микрокоманды. Этот процесс будет повторяться до тех пор, пока, не бу передан весь объем обменного Ьлока. Анализ конца обмена всего объема блока выполняется следующим образом. По синхросигналу СИ 1 (линия 170) в триггер 168 заносится состояние соответствующего разряда текущего адреса до его модификации. Следующее занесение в триггер 168 будет выполнено, только в другой микрокоманде по СИ 1 (цикл выполнения микрокоманды СИ 1 И СИ 8).

Таким образом, в конце выполнения микрокоманды модификации адреса на первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 169 будут подаваться значения одного и того же разряда щего адреса после его модификации и до его модификации соответственцр Если разряд в течение этого времени изменил полярность, то весь объ- ем обменного блока данных передачи,. На выходе 43 блока появится сигнал, который по СИ 5 (линия -174) установит триггер 162 и далее по СИ 7 (ли- , НИН 176) и специальному управляющему сигналу обращения к оперативной па35

40

45

50

мяти, поступающему на вход элемента И 164 с входа 40 блока, будет установлен триггер 163, который будет

сброшен по СИ 1 (линия 170) следующего цикла. Следовательно, в течение продолжительности синхроимпульсов СИ 7, СИ 8 будет сброшен триггер 153, что повлечет за собой сброс по СИ 1

(линия 170) следующего цикла триггера 152, вследствие чего будет выполнена перезапись информации из регистра хранения очередного адреса в регистр хранения текущего адреса,

вследствие чего начнется передача очередного блока данных, кроме того будет сброшен по СИ 3 (линии 172) триггер 151, вследствие чего на выходе 42 блока будет установлен сигнал

5

0

5

0

5

0

путем следующего адреса в регистр 146 хранения очередного адреса. Этот сигнал будет сохраняться до тех пор, пока запись очередного адреса не будет выполнена. Эта запись выполняется по управляющему сигналу на линии 73, за счет чего устанавливается триггер 151 и автоматически сбрасывается сигнал на управляющем выходе 42 блока 9 формирования команд.

Формула изобретения

15

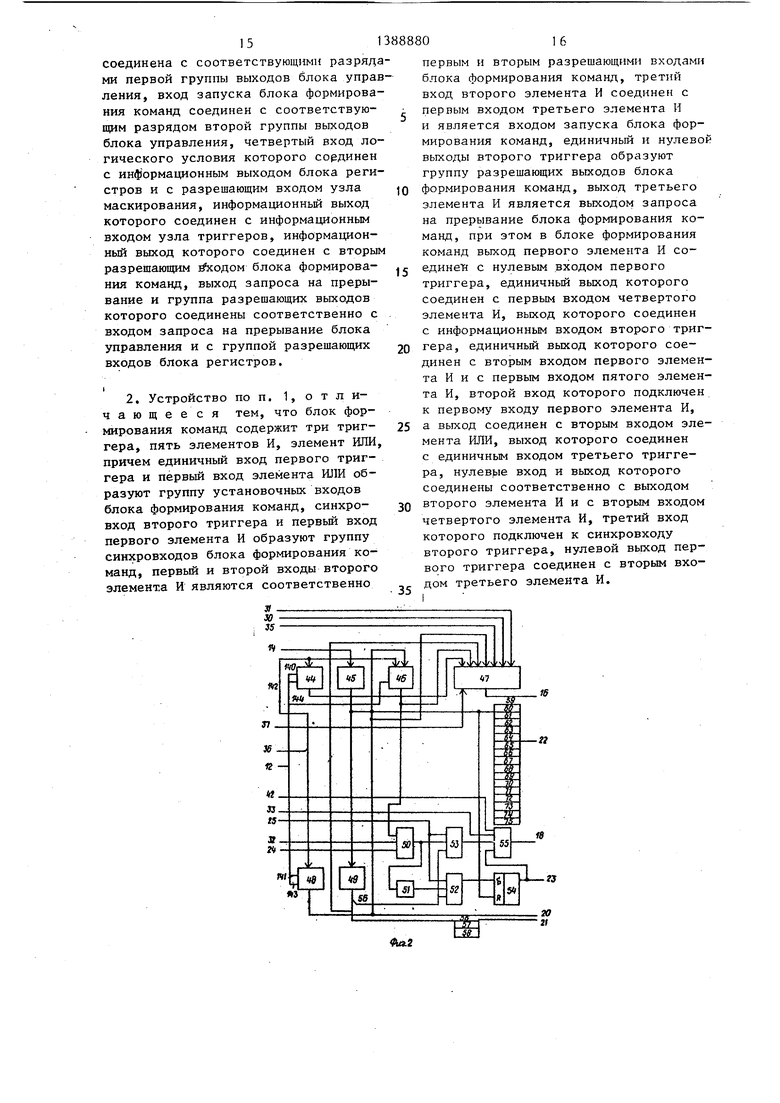

соединена с соответствующими разрядми первой группы выходов блока упраления, вход запуска блока формирования команд соединен с соответствую- щим разрядом второй группы выходов блока управления, четвертый вход логического условия которого соединен с информационным выходом блока регистров и с разрешающим входом узла маскирования, информационньй выход которого соединен с информационным входом узла триггеров, информационный выход которого соединен с вторы разрешающим йсодом блока формирова- ния команд, выход запроса на прерывание и группа разрешающих выходов которого соединены соответственно с входом запроса на прерывание блока управления и с группой разрешающих входов блока регистров.

первым и вторым разрешающими входами блока формирования команд, третий вход второго элемента И соединен с первым входом третьего элемента Н и является входом запуска блока формирования команд, единичный и нулевой выходы второго триггера образуют группу разрешающих выходов блока формирования команд, выход третьего элемента И является выходом запроса на прерывание блока формирования команд, при этом в блоке формирования команд выход первого элемента И со- единеТ с нулевым входом первого триггера, единичный выход которого соединен с первым входом четвертого элемента И, выход которого соединен с информационным входом второго триггера, единичный выход которого соединен с вторым входом первого элемента И и с первым входом пятого элемента И, второй вход которого подключен к первому входу первого элемента И, а выход соединен с вторым входом элемента ИЛИ, выход которого соединен с единичным входом третьего триггера, нулевые вход и выход которого соединены соответственно с выходом второго элемента И и с вторым входом четвертого элемента И, третий вход которого подключен к синхровходу второго триггера, нулевой выход первого триггера соединен с вторым входом третьего элемента И.

ts

/5

16

-

77

22 32

3f

111L

8/

113

65

ез

61

21

56

12

56

91

92

f3

jrr

Фиг. 3

12 if

mi

98

L

.-Ж. 9ff

3d

т

fW

фигЛ

70

11

68

Г

29

69

62

21

25 28

UT

9if

W3

/4r/

t

wo

30

П

31 т

115

IL

т

г

.

ш

.5/

im

П7

JJ

ш

т

12В

127

J29

66

22

(.7

срие.в

т

S5

т

J30

.56

24т

74

75

№f

Зв

ТбО

22

S9 -

т

/«5

/«7

1

150

Фие

/7)7

r.

/Г/

n

/7/

n

/7J

n

v;

n.

/Xf

n

.

n

/ГУ

ffjijeJZ

n

n

n

n

n

n

ru

qtuea

FL

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-15—Публикация

1986-10-08—Подача