Изобретение относится к области вычислительной техники, в частности к организации мультиплексных каналов микропрограммных вычислительных машин и может быть использовано для управления обменом информацией между внешними устройствами (ВУ и процессором. Известны мультиплексные каналы микропрограммных вычислительных машин которые при выполнении операций вводвывода используют оборудование центг рального процессора fJ содержащего оперативную память, блок памяти микро программ , арифметическо-логическое устройство и мультиплексную память, соединенные между собой и каналом системойинформационных и управляющих шин. Известные каналы при работе в мультиплексном режиме, выполняя обмен информацией между ВУ и процессором, считывают для каждого устройства управляющую информацию опера1Э1и ввода-вывода из мультиплексной памяти, выполняют обмен информацией между ВУ и оперативной памятью, затем запоминают измененную управляющую информацию мультиплексной памяти. Недостатком этих каналов является низкая пропускная способность, так как при обмене информацией с ВУ они используют оборудование процессора на время считывания и записи управляющей информации операции ввода-вывода, что значительно снижает производительность процессора. Наиболее близким к изобретению по сущности технического решения является мультиплексный канал IBM 360/30 C2J, содержащий блок управленчя каналом, блок регистра, блок управления интерфейсом, регистр последующего адреса, управлякхций, первый н второй информационные выходы которого подключены соответственно к первому выходу блока управления каналом, к первому и второму входам канала, третий, четвертый и пятый входы которого подключены соответственно к информационному входу блока регистров, ко входу блока управления каналом и к первому информационному входу блока управления интерфейсом, второй информационный и управляюпщй входы которого подключены соответственно к первому .информационному и управлякицему входам регистра последующего адреса, выход которого подключен к первому выходу канала, второй, третий, четвертый и пятый выходы которого подключены соответственно к первому и второму информа ционным выходам блока управления . интерфейсом,ко второму выходу блока управления каналом и к выходу блока регистров, управляющий вход которого подключен к первому выходу блока управления каналом,

В этом канале микропрограммы канала и процессора размещаются в одном блоке памяти микрограмм, и в любой момент времени может выполняться микропрограмма либо процессора, либо канала. Причем микропрограммы канала более приоритетны и могут прерывать микропрограмг ы процессора.

Недостатком канала является то, что он при большой загрузке имеет низкую пропускную способность, что значительно снижает производительнос процессора.

Цепью изобретения являетая повышение пропускной способности канала и снижение влияния канала на произволительность процессора.

Поставленная цель достигается тем что в мультиплексный канал, срдержаш й блок дешифрации команд, блок регистров, блок сопряжение с интерфейсом регистр последукяцего адреса, первый и второй информационные входы и выход которого являются соответственно первым и вторьм-входом яс первым выходом канала, а управляюп91й вх соединен с управляющими входами блока сопряжения с интерфейсом и блока регистров и первым выходом блока дешифрации команд, первые и вторые информационные входы и выходы блока сопряжения с интерфейсом соединены соответственно с третьим и первым входами и вторым и третьим выходами канала, вход и второй выход блока дещифрации команд являются соответствено четвертым входом и выходом канала а информационный вход и выход блока

регистров соединены соответственно с пятыми входом и выходом канала, введены .блок формирования начальных адресов подпрограмм и запроса, блок сравНения адресов, регистр текущего адреса и триггер загрузки регистров, С первого по пятый выходы блока формирования начальных адресов подпрограмм и запроса являются соответственно щестым г десятым выходами канала. Первый вход соединен с шес тым входом канала, второй и третий входы - соответственно с первым и вторым управляющими выходами блока

сопряжения с интерфейсом, а четвертый и пятый входы - соответственно с выходами блока сравнения адресов и триггера загрузки регистров. Первый и второй входы блока сравнения адресов соединены соответственно с информационным входом и выходом ре- гистра текущего адреса, управляющий вход которого подключен к третьему выходу блока дешифрации команд, че-гвертым и.пятым выходами соединенного с соответствукшдами входами триггера загрузки регистров. Выход регистра последующего адреса соединен с первым входом блока сравнения. Блок формирования начальных адресов подпрограмм и запроса содержит элемент ИЛИ, два элемента НЕ и пять элементов И, выхода, которых подключены соответственно к первому - пятому выходам блока, а первые входы - к первому входу блока. Вторые входа первого, второго и третьего элементов И подключены к выходу элемента ИЖ, первый и второй входы которого соединены соответственно со вторыми входами пятого и четвертого элементов И и вторым и третьим входами блока. Третий вход второго элемента И подключен через первый элемент НЕ к третьим входам третьего, четвертого и пятого элементов И и пятому входу блока Четвертый вход третьего элемента И соединен через второй элемент НЕ с четвертыми входами четвертого и пятого элементов И и четвертым входом блока.

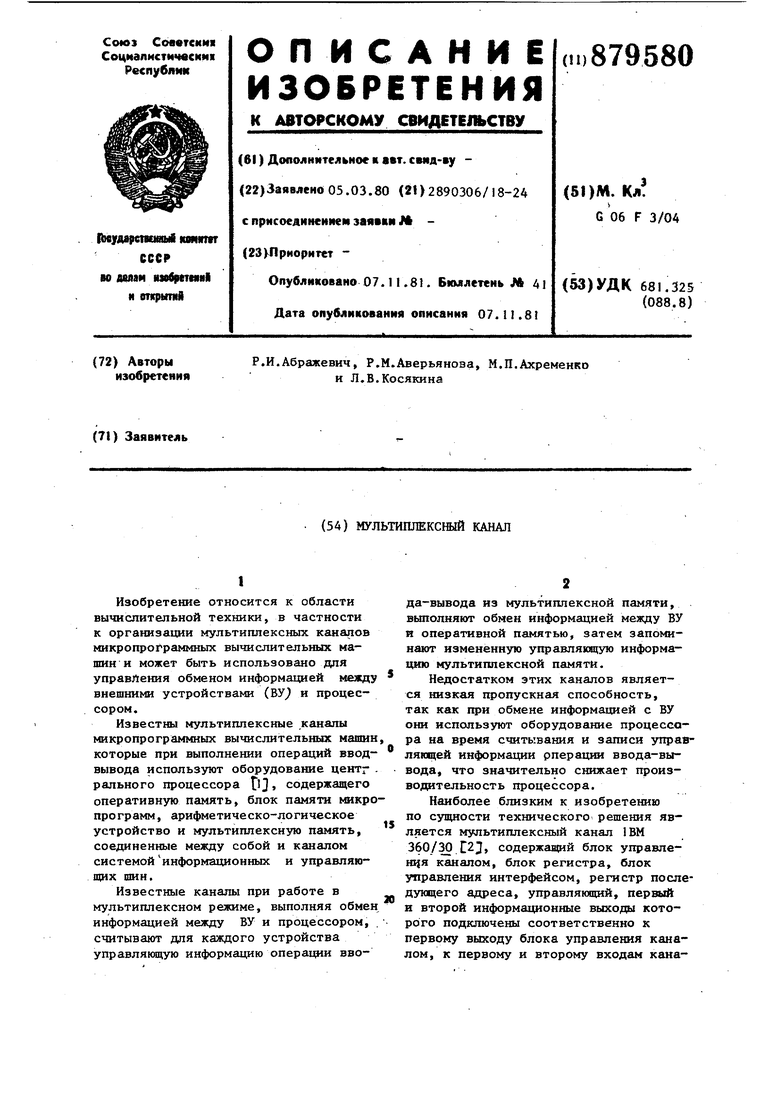

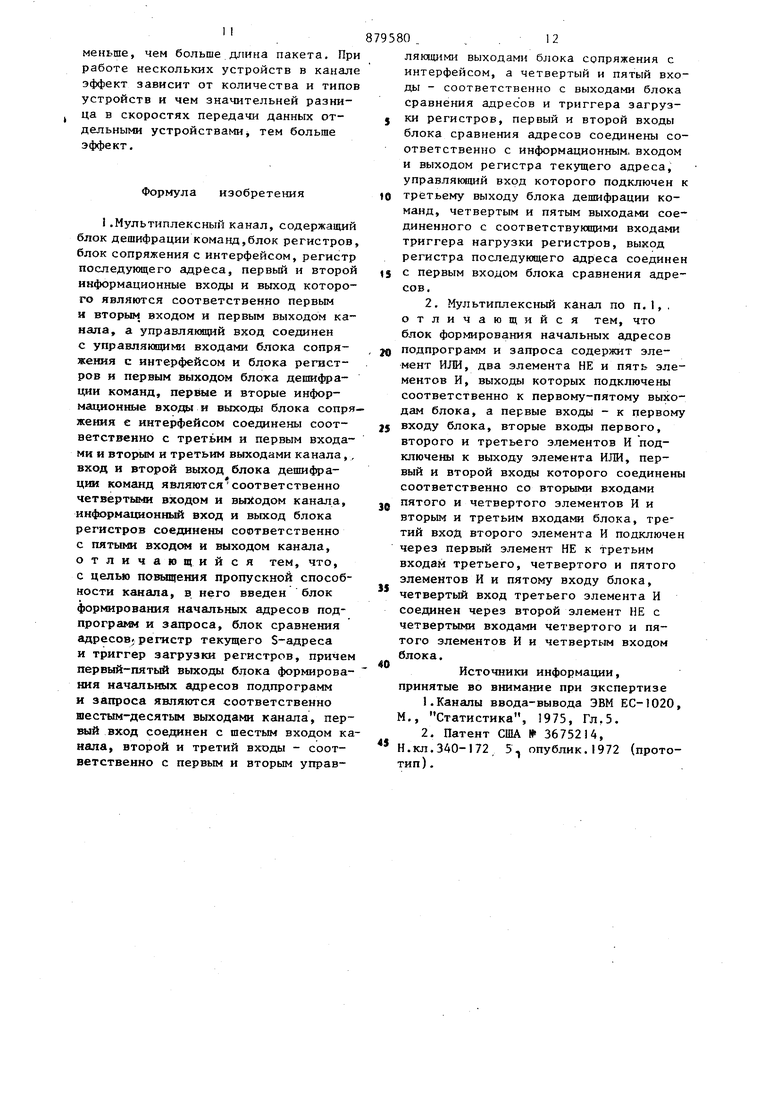

На фиг,1 представлена структурная схема мультиплексного канала и процессора; на фиг,2 - схема блока деши чрации команд; на фиг,3 - схема блока

. регистров; на фиг.4 - схемаблока сопряжения с интерфейсом; на фиг,5 схема :входного регистра управления интерфейсом; на фиг,6 - схема узла

управления выходными сигналами интерфейса; на фиг.7 - структура блока сравнения адресов; на фиг.8 - схема блока формирования начальных адресов подпрограмм и запроса.

Мультиплексный канал 1, соединенный с процессором 2 (фиг.) содержит блок 3 дешифрации.команд, блок 4 регистров, блок 5 сопряжения с интерфейсом, регистр 6 последующего адреса, регистр 7 текущего адреса, триггер 8 загрузки регистров, блок 9 сравнения адресов, блок 10 формирования начальных адресов и запроса. Процессор 2 включает блок 1I арифметческо-логического устройства, блок 12 памяти микропрограмм, блок 13 мультиплексиой памяти и блок 14 оперативной памяти. На фиг.1 обозначены входные информационные шины 15 процессора, выходные информационные шины 16 процессора, пятый, третий, четвертый, шестой, второй и первый входы 17-22 канала, пятый, второй, четвертый, шестой - десятый, первый и третий выходы 23-32 канала, первый четвертый, пятый и третий выходы 33-36 блока дешифрации команд, второ и первый входы 37, 38 блока сравнени адресов, второй, третий, пятый и четвертый входы 39-42 блока формирог вания начальных адресов подпрограмм и запроса.

Блок 3 дешифрации команд (фиг. содеряйт дешифратор 43 микропрограммных установок кашала, дешифратор 44 микропрограммных сбросов канала, дешифратор 45 микропрограммного упраления регистрами, триггер 46 запроса на прерывание по вводу-выводу.

На фиг.2 обозначены шины 47-53 управляющих сигналов микропрограммны установок первого вьпсода блока, шины 54-61 управляющих сигналов микропрограммных сбросов первого выхода блока, шины 62-74 управляюп р1х сигналов приема информации в регистры канала первого выхода блока,.

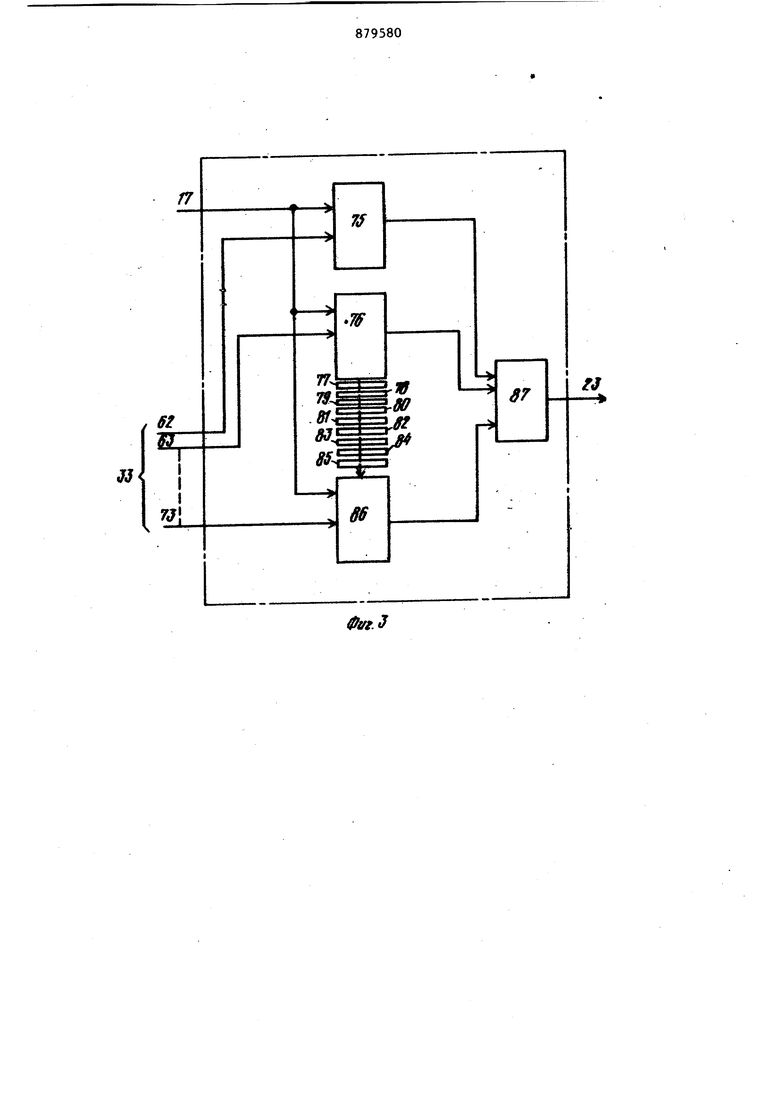

Блок 4 регистров (фиг.З) содеряоит регистры 75-86 хранения информации канала, мультиплексор 87 вьщачи содержимого регистров на шины 23 пятого выхода канала.

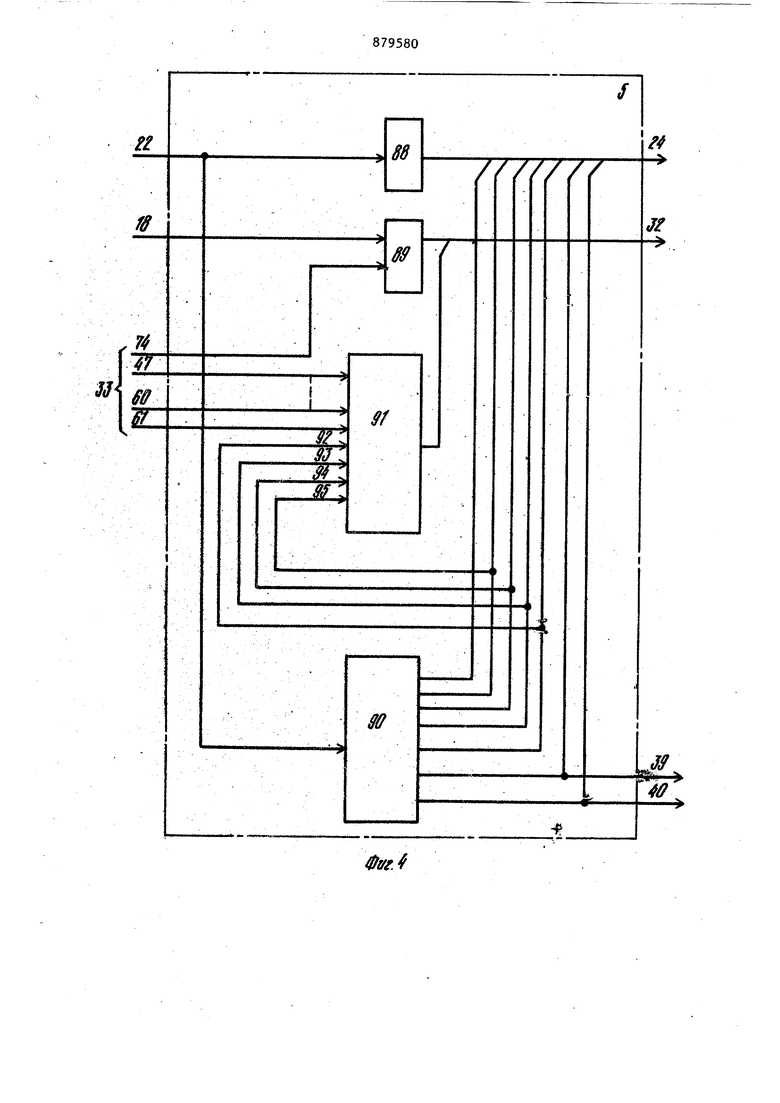

Блок 5 сопряжения с интерфейсом (фиг.4) содержит регистр 88 входной информации иитерфейса, регистр 89 выходной информации интерфейса, регист 90 управления входными сигналами интерфейса, узел 91 управления выходными сигналами интерфейса. На фиг.4 обозначены пшны 92-95 входных ;управлякяцих сигналов интерфейса первого информационного выхода блока. Регистр 90 управления входными сигнала -ш интерфейса (фиг.5) содержит триггер 96 информации абонента, триггер 97 управления абонента, триггер 98 адреса абонента, триггер 99

работы абонента, триггер 100 требования абонента, триггер 101 обратной выборки и триггер 102 измерения от абонента.

Узел 91 управления выходными сигналами интерфейса (фиг.6) содержит триггер 103 выборки канала, триггер 104 сброса выборки, триггер 105 блокировки выборки, триггер 106 начальной выборки, триггер 107 адреса кана-па, триггеры 108-114 управления канала, элементы 115-П6 И-ИШ, элементы И П7-11§, элементы НЕ 119-121, элементы ИШ 122 и элемент задерж-:. ки 123. .

Клок 9 сравнения адресов (фиг. содержит элементы 124-131 сложения по модулю 2 и элемент И 132Блок формирования начальных адресов (4мйг.8) содержит элемент ИЛИ 133,

элементы НЕ 134 И 135 .элементы k 136-140.

ультиш1ексный канал 1 предназначен для подключения к процессору 2 сравнительно медленно действующих устройств ввода-вывода и управления передачей информации между ними Н процессором.

Блок 3 предназначен для форьтрова- ния микропрограммных сигналов управления каналом, блок 4 регистров - для хранения управляющей информации oneрации ввода-вывода, выполняемой каналом. Блок 5 предназначен для обмена информацией между каналом,ВУ (на фиг. не показаныр и процессором. Связь с ВУ осуществляется через вход 22 и выход 32 канала. Обмен информацией с процессором осуществляется через вход 18 и выход 24 канала.

Регистр 6 последующего адреса предназначен для хранения адреса ВУ.. Адрес ВУ запоминается в регистре 6 при инициации операции ввода-вывода в канале, а также в случае приема адреса в канал по требованию устройства в мультиплексном режиме работы канала.Адрес устройства принимается со входа 21 я 22 канала.

Операция ввода-вывода в мультиплексном накале начинается по специальной команде процессора, которая задает адрес канала ВУ и при помощи специальных управляющих слов указывает код команды, начальный адрес оперативной памяти, количество передаваемых байтов данных и другие управляющие признаки, по которым под управлением блока 12 и посредством блока 1I формируется специальное управляющее слово устройства, записываемое в блок

4и в блок 13 мультиплексной памяти. Для каждого ВУ в блоке 13 отводится определенная фиксированная область, называемая подканалом. В мультиплексном канале может одновременно выполняться несколько операций ввода-вывода. Канал обслуживает ВУ по их запросам, поступаюофим со входа 22 в блок 5. При работе канала с одаим или несколькими ВУ от одного и того же устройства может поступать в канал подряд несколько запросов на обг слутЕивание.

В предлагаемом канале в регистр 7 запоминается адрес последнего обслуженного ВУ, управляющее слово которого находится в регистрах блока 4 и в подканале, и всякий раз, когда новый поступает в канал, адрес &У|приславшего запрос, заносится в регистр 6 посшедукмдего адреса и в

блоке 9 сравнивается с содержимым регистра 7 текущего адреса. В зависимости от результата сравнения,.

ида запроса и.состояния триггера 8 блок to формирует один из четырех фиксированных адресов, (0001, 0010,

0100, 1000 , поступающих с шлходов 27-30 канала на адресные шины блока 12 natoiTH микропрограмм,вызывая соответствующую короткую подпрограмму обслуживания. Триггер 8 загрузки регистров всегда находится в состоягг юта I, если в блок 4 производилась

дагрузка управляющего слова любого ВУ устройстваи;.в состоянии О, если загрувки не было..

Мультиплексный канал работает следуюцим образом.

Получив необходимую управляющую информацию и разместив ее в блоке регистров, канал 1 выполняет начальную выборку адресуемого ВУ через вход 22 и выход 32 канала.При зтом передаче чей адреса ВУ, кода команды и байта Начального состояния управляет блок

5совместно с блоком 12,

Далее по командам из блока 3 адрес ВУ записывается в регистр 6 и дублируется в регистре 7 текущего адреса, триггер 8 устанавливается в единичнее состояние, а под управлением сиггг, уналов из блока 12 блок 13 мультиплекс- ной памяти настраивает на область памяти, соответствующую ВУ, адрес которого хранится в регистре 6. После

запуска операции ввода-вывода на устройстве мультиплексный канал 1 логически отключается от процессора 2 и ВУ.

Режим работы канала по обмену данг.

5 ными между ВУ и процессором 2 в дальнейшем зависит от того, какое ВУ выставит на вход 22 канала запрос на обслуживание - ВУ, дпя которого управляющая информация операции ввода-выQ вода находится в блоке регистров, ипи Byv для которого управляющая информация операции ввода-вывода находится в блоке 13 мультиплексной памяти.

В мультиплексном режиме при г.отовности одного из ВУ принять или передать байт данных или байт состояния ВУ выставляет на шины 22 канала сигнал запроса на обслуживание (ТРБ-А), поступакяций в блок 5 по входу 94 (иГб). Если канал не занят выполнением операции ввода-вывода, т.е. отсутствуют сигналы интерфейса на входах 93, 95 (РАБ-А, BBF-AJ, триггер 105 сброшен, то устанавливается триггер 103 выборки устройства (ВБРК). Начинается последовательность илборки устройства и обмена информацией с ним, в течение которой ВУ выдает на вход 22 свой адрее, которьй записывается в регистр 6, и далее признак вида обслужива1шя (ИНФ-А или УПР-А, по которому в блоке 5 формируется соответственно сигнал Требование на обслуживание данных или Требование на обслужи ванне состояния. Эти сигналы поступают в блок 10 соответственно по входам 39 или 40 (4ИГ.8; для формирования по ним сигнала запроса на микропрограммную приостановку и к сированного адреса Рмикропрограммы

обслуживания запро са по сигналу приема фиксированного адреса подпрограммы на входе 20. Сигнал запроса на микропрограммную приостановку

5 по выходу 26 поступает в блок 12 памяти микропрограмм, где по нему с шин 27-30 при нимается код ксированного адреса микропрограммы обслуживания. В зависимости от вида обслуживания и состояния канала вырабатывается четыре кода фиксированного адреса микропрограммы обслуживания, по которым в блоке 12 вызываются (иниции руются) соответствукнцие микропрограм мы обслуживания запроса. Когда по запросу ВУ на входе 39 блока 10 сформировался сигнал Требо вания на обслуживание данных, а в блоке 4 находится управляющее слово дпя выбранного ВУ, то блок 0 форми рует фиксированный адрес 0001, вызывая соответствунлцую микропрограмму в блоке 12. В этом случае управляющее слово не читается из блока 13 мультиплексной памяти, а берется из блока 4 регистров и производится обмен данными между ВУ и блоком 14 оперативной памяти. При операции чтения данные со вхо яа 22 принимаются блоком 5 и переда- нзтся на выход 24 и далее через блок 11 арифметического устройства записы ваются в блок 14 оперативной памяти. При операции записи данные считываются из блока 14 оперативной памят проходят через блок 1 I ари||метическо логического устройства, вход 18 кана ла, блок 5 и передаются на выход 32 канала. После обмена данными управлягрщее слово устройства в блоке регистров модифицируется в блоке 11 и снова записывается в блок 4,- Мультиплексны какал 1 логически отключается от ВУ и процессора 2. Когда на входе 40 блока 10 сформировался сигнал Требование на обсл живание состояния, а- в блоке регист ров содержится управляющая информация для выбранного ВУ, то блок ГО формирует фиксированный адрес 0010, вызывая соответствующую микропро- -грамму в блоке 12, завершения операции ввода-вывода с данным ВУ. Триг- гер 8 по входу 35 сбрасывается в О а мультиплексный канал 1 логически отключается от ВУ и процессора 2. Если блок регистров не содержит управлякнцего слова ни для одного из ВУ, а по запросу от ВУ формировался сигнал на входе 39 или 40 блока 10, „формируется фиксированный адрес 1000 и выполняется микропрограмма обслуживания запроса,по которой из блока 13 мультиплексной памяти по адресу устрой ства на выходе 31 канала считывается соответствующее ему управляющее слово 0. 10 устройства и через блок П, вход 17 канала записывается в блок 4 регистров; адрес ВУ из регистра 6 переписывается в регистр 7, а триггер 8 устанавливается в состояние 1. После этого осуществляется чтение (или запись) данных из (в) оперативной памяти как описано для случая фиксированного адреса 0001, если по запросу ВУ сформирован сигнал на входе 39 блока 10 или осуществляется обслуживание байта состояния как описано для случая фиксированного адреса 0010, если сигнал сформирован на входе 40 блока 10. Если же по запросу ВУ сформирован сигнал на входе 39 или 40 блока 10, а в блоке регистров содержится управляющее слово дпя другого ВУ, то блок 10формирования начального адреса и запроса формирует фиксированный адрес 0100, и начинает выполняться соответствуимцая ему 1 кропрограмма, в процессе выполнения которой содержимое блока 4 через выход 23 и блок 11записывается в подканал, соответствукнций адресу в регистре 7. Дальнейшее действие в канале совпадает с действиями, описанными дпя случая с фиксированным адресом 1000. Таким образом, любая операция в канале, связанная с передачей данных, выполняется в три этапа: - начальная выборка ВУ,- передача данных и заверщение операции, причем все три этапа выполняются под управлением микропрограмма так, что основная нагрузка пpиxo p тcя на второй этап, который выполняется н режиме микропрограммной приостановки в мультиплексном режиме или в монопольном режиме. В режиме микропрограммной приостановки канал оказывает минимальное воздействие на процессор, задерживая его работу при каждой передаче данных на время одной приостановки . Реальная пропускная способность канала зависит от технических характеристик блоков канала, процессора, от количества ВУ, подключенных к каналу, и их скоростей передачи данных. Анализ работы канала показывает, что наибольший эффект достигается .; при работе одного устройства, работаг няцего в мультиплексном режиме и neper дающего данные по одному байту. При передачеданных пакетами эффект тем

меньше, чем больше длина пакета. При работе нескольких устройств в канале эффект зависит от количества и типов устройств и чем значительней разница в скоростях передачи данных отдельными устройствамиj тем больше эффект.

Формула изобретения

1 .Мультиплексный канал, содержащий блок дешифрации команд,блок регистров, блок сопряжения с интерфейсом, регистр последующего адреса, первьй и второй информационные входы и выход которого являются соответственно первым и вторым входом и первым выходом канала, а управлякйций вход соединен с управляю1Ци Я1 входами блока сопряжения с интерфейсом и блока регистров и первым выходом блока депшфрации команд, первые и вторые информационные входы и выкодь блока сопряжеиия е интерфейсом соединены соответственно с третьим и первым входами и вторым и третьим выходами канала,, вход и второй выход блока дешифрации команд являютсясоответственно четвертыми входом и выходом канала, информационный вход и выход блока регистров соединены соответственно с пятыми ВХОДСМ4 и выходом канала, отличающийся тем, что, с целью повыщения пропускной способности канала, в. него введен блок формирования начальных адресов подпрогра ® и запроса, блок сравнения адресов, регистр текущего S-адреса и триггер загрузки регистров, причем первый-пятый выходы блока формирования начальных адресов подпрограмм и запроса являются соответственно шестым-десятым выходами канала, первый вход соединен с шестым входом канала, второй и третий входы - соответственно с первым и вторым управ79580 . .12

ляющими выходами блока сопряжения с интерфейсом, а четвертый и пятый входы - соответственно с выходами блока сравнения адресов и триггера загрузJ ки регистров, первый и второй входы блока сравнения адресов соединены соответственно с информационным, входом и выходом регистра текущего адреса, управлякадий вход которого подключен к

to третьему выходу блока дешифрации команд, четвертым и пятым выходами соединенного с соответствующими входами триггера нагрузки регистров, выход регистра последующего адреса соединен

i с первым входом блока сравнения адресов.

2. Мультиплексный канал по п.1,, отличающийся тем, что блок формирования начальных адресов jfl подпрограмм и запроса содержит элемент ИЛИ, два элемента НЕ и пять элементов И, выходы которых подключены соответственно к первому-пятому выходам блока, а первые входы - к первому

25 входу блока, вторые входы первого, второго и третьего элементов И подключены к выходу элемента ИЛИ, первый и второй входы которого соединены соответственно со вторыми входами

jU пятого и четвертого элементов И и вторым и третьим входами блока, третий вход второго элемента И подключен через первый элемент НЕ к третьим входам третьего, четвертого и пятого элементов И и пятому входу блока, четвертьй вход третьего элемента И соединен через второй элемент НЕ с четвертыми входами четвертого и пятого элементов И и четвертым входом блока.

Источники информации, принятые во внимание при экспертизе

1.Каналы ввода-вывода ЭВМ ЕС-1020, М., Статистика, 1975, Гл,5. 2. Патент США 3675214,

Н.кл.340-172 5, опублик.1972 (прототип).

Фо.1

фуг.З

tff

фуг,

JK

an

rff

«f

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Мультиплексный канал | 1980 |

|

SU964620A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для управления каналами | 1976 |

|

SU641436A1 |

| Мультиплексный канал | 1973 |

|

SU517022A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Устройство для управления диагностикой каналов | 1973 |

|

SU526876A1 |

| Устройство для управления каналами | 1974 |

|

SU520592A1 |

м

4133-

af

I

Авторы

Даты

1981-11-07—Публикация

1980-03-05—Подача