(54) РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО

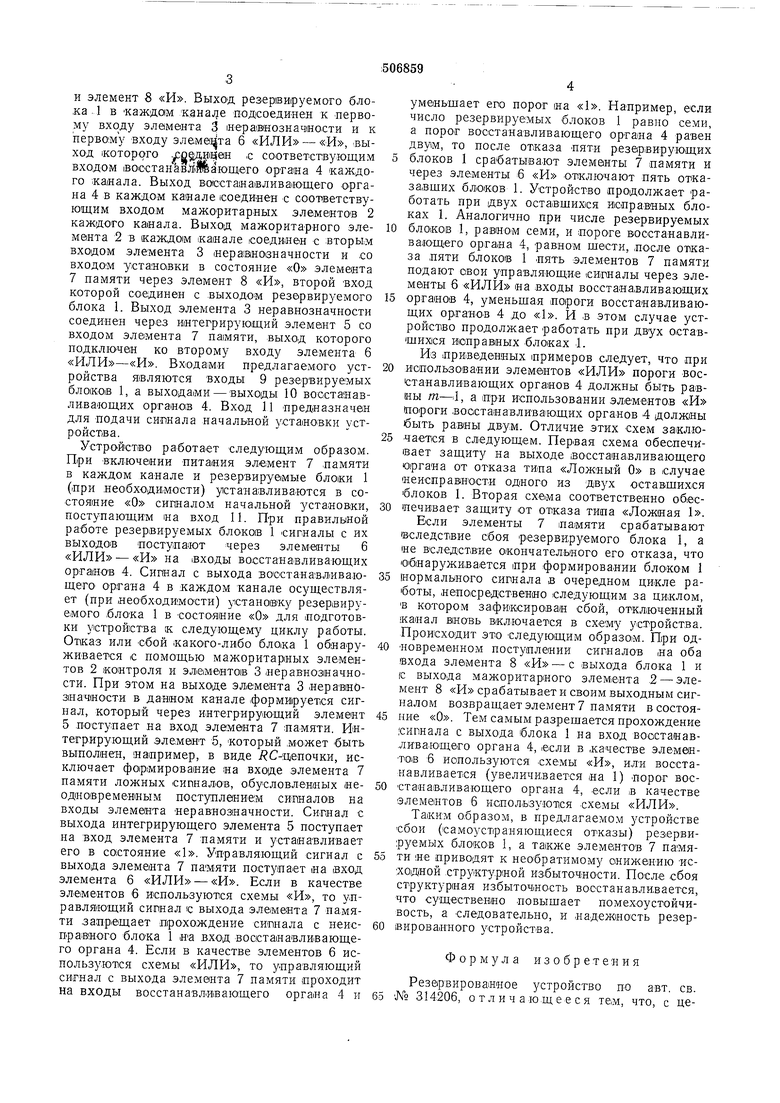

и элемент 8 «И. Выход резервируемого блока . 1 в Каждом Kanajje подсоединен к нервому входу эламента 3 «еравиозначности и к первому входу эл&мщта 6 «ИЛИ - «И, -выход iKOTOporo xn piHien с соответствующим входом |В01Сстанав)1||1ающего ортана 4 каждого «а/нала. Выход восстаиавливающего органа 4 в каждом канале (соединен с соответствующим входом мажоритарных элементов 2 каждого канала. Выход мажоритарного элемента 2 в каждом канале соединен с вторым входом элемента 3 нераиновначности и со входом установки в состояние «О элемента 7 памяти через элемент 8 «И, второй вход которой соединен с выходом резервируемого блока 1. Выход элемента 3 неравнозначности соединен через интегрирующий элемент 5 со входом элемента 7 , выход которого подключен ко второму входу элемента 6 . Входами предлагаемого устройства являются входы 9 резервируемых блоков 1, а выходами - выходы 10 восстанавливающих органов 4. Вход И предназначен для подачи сигнала начальной установки устройства.

Устройст1во работает следующим образом. Ири включении питания элемент 7 памяти в каждом канале и резервируемые блоки 1 (нри необходимости) устанавливаются в состояние «О сигналом начальной зстанов-ки, поступающим на вход 11. При правильной работе резервируемых блок01В 1 Сигналы с их выходов поступают через элем-енты 6 «ИЛИ - «И на (ВХОДЫ восстанавливающих органов 4. Сигнал с выхода восстанавливающего органа 4 в .каждом канале осуществляет (при необходимости) установку резервируемого блока 1 в состояние «О для подготовки устройства к следующему циклу работы. Отказ или Сбой какого-либо блока 1 обнаруживается с помощью мажоритарных элементов 2 контроля и элементов 3 неравнозначности. При этом на выходе элемента 3 неравнйзначности в даннОМ канале .формируется сигнал, который через интегрирующий элемент 5 поступает на вход элемента 7 яамяти. Интегрирующий элемент 5, который может -быть выполнен, яашример, в виде С-цепочки, исключает формирование на входе элемента 7 памяти ложных сипналов, обусловленных неодновременным поступлением сишалов на входы элемента неравнозначности. Сигнал с выхода интегрирующего элемента 5 поступает на вход элемента 7 памяти и устанавливает его в состояние «1. Управляющий сигнал с выхода элемента 7 памяти поступает на (Вход элемента 6 «ИЛИ - «И. Если в качестве элементов 6 используются схемы «И, то управляющий си;пнал с выхода элемента 7 памяти запрещает прохождение сигнала с неисправного блока 1 на вход восстанавливающего органа 4. Если в качестве элементов 6 используются схемы «ИЛИ, то управляющий сигнал с выхода элемента 7 памяти проходит на входы восстанавливающего органа 4 и

уменьшает его порог на «1. Например, если число резервируемых блоков 1 равно семи, а порог восстанавливающего органа 4 равен двум, то после отказа Пяти резервирующих блоков 1 срабатывают элементы 7 памяти и через элементы б «И отключают пять отказавших блоков 1. Устройство продолжает работать при двух оставщихся июправных блоках 1. Аналогично при числе резервируемых

блоков 1, рав(ном семи, и пороге восстанавливающего органа 4, равном шести, после отказа пяти блоков 1 пять элементов 7 памяти подают овои управляющие сигналы через элементы 6 «ИЛИ на входы восстанавливаюЩих

органов 4, уменьшая пороги восстанавливающих органов 4 до «1. И в этом случае устройство продолжает работать при двух оставшихся исправных блоках 1.

Из приведенных примеров следует, что при

иопользовании элементов «ИЛИ пороги восстанавливающих органов 4 должны быть равны т-)1, а при использовании элементов «И пороги восстанавливающих органов 4 долж1Ны быть равны двум. Отличие этих схем заключается в следующем. Первая схема обеспечивает защиту на выходе восстанавливающего органа от отказа типа «Ложньгй О в случае яеисправности одного из двух оставшихся блоков 1. Вторая схема соответственно обесиечивает защиту от отказа типа «Ложная 1.

Если элементы 7 памяти срабатывают

вследствие сбоя резервируемого блока 1, а

не вследствие окончательного его отказа, что

обнаруживается при формировании блоком 1

нормального сигнала в очередном цикле работы, непосредственно следующим за циклом, В котором зафиксирован сбой, отключенный канал вновь включается в схему устройства. Происходит это Следующим образом. При одПовременном поступлении сигналов на оба .входа элемента 8 «И - с выхода блока 1 и (С выхода мажоритарного элемента 2 - элемент 8 «И срабатывает и своим выходным сигналом возвращает элемент 7 памяти всостоякие «О. Тем самым разрешается прохождение сигнала с выхода блока 1 на вход воостаиав.ливающего органа 4, если в качестве элементов 6 используются схемы «И, или восстанавливается (увеличивается на 1) ПОрог восстанавливающего органа 4, если в качестве элементов 6 используются схемы «ИЛИ.

Таким образом, в предлагаемом устройстве сбои (самозстраняющиеся отказы) резервируемых блоков 1, а также элементов 7 памяти не приводят к необратимому снижению исходной .структурной избыточнОСти. После сбоя структурная избыточность восстанавливается, что существенно повышает помехоустойчивость, а следовательно, и -надежность резер1вированного устройства.

Формула изобретения

Резервированное устройство цо авт. св. № 314206, отличающееся тем, что, с целью повышения его помехоустойчивости и надежиости, оно содержит в каждом канале элемент «И, первый вход которого подключен к выходу мажоритарного элемента, второй вход соединен с выходом резервируемого

,блока, а выход элемента «И соединен с входом установки В состояние «О элемента памяти, причем выход воостанавливающего органа соединен с входом установки в «О резервируемого блюка.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное устройство | 1978 |

|

SU805319A2 |

| Адаптивное резервированное устройство | 1974 |

|

SU550638A1 |

| Резервированное устройство | 1979 |

|

SU819995A1 |

| РЕЗЕРВИРОВАННОЕ УСТРОЙСТВОE:?^'iJV. -, | 1971 |

|

SU314206A1 |

| Резервированное устройство | 1991 |

|

SU1785089A1 |

| Мажоритарно-резервированное устройство | 1978 |

|

SU742940A1 |

| Резервированная система | 1988 |

|

SU1584137A1 |

| Резервированное устройство | 1991 |

|

SU1830575A1 |

| Адаптивное резервированное устройство | 1983 |

|

SU1149264A1 |

| Резервированное устройство | 1980 |

|

SU928685A1 |

Авторы

Даты

1976-03-15—Публикация

1973-10-12—Подача