(54) РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное резервированное устройство | 1974 |

|

SU550638A1 |

| Резервированное устройство | 1973 |

|

SU506859A1 |

| Резервированное устройство | 1974 |

|

SU551644A1 |

| Резервированное устройство | 1982 |

|

SU1059710A1 |

| Резервированное устройство | 1980 |

|

SU928685A1 |

| Резервированная система | 1988 |

|

SU1584137A1 |

| Резервированное устройство | 1979 |

|

SU819995A1 |

| Адаптивное резервированное устройство | 1983 |

|

SU1149264A1 |

| Адаптивное резервированное устройство | 1981 |

|

SU962959A1 |

| Многоканальное резервированное устройство с перестраиваемой структурой | 1976 |

|

SU669501A1 |

Изобретение относится к автомати и вычислительной технике и может на ти применение в системах автоматического управления и контроля для повышения их надежности. По основному авт. св. 506859 известно резервированное устройство содержащее в каждом канале резервир емый блок, мажоритарный элемент кон роля, элемент неравнозначности, интегрирующий элемент, первый элемент памяти, элемент ИЛИ-И, восстанавлив щий орган и первый элемент И l . Недостаток известного устройства заключается в том, что оно теряет работоспособность после любого отказа одного из двух оставшихся работоспособных резервируемых блоков, поскольку процесс отключения отказавшего резервируемого блока или из менение порога срабатывания восстанавливающего органа продолжается и после того, как в устройстве осталось два работоспособных резервируемых блока. В связи с этим недостаточно используются структурные возможности устройства для повышения его Нсщежности. Недостатком известного устройства является и то, что оно теряет работоспособность в случае, если сигналы на выходах резервируемых блоков формируются с частотами, превышающими частоту форм1 рования полезных сигналов в два или более раз. Например, если такие отказы происходят вустройстве последовательно во времени, то после того как число отказавших резервируемых блоков станрвится равным порогу срабатывания восс: анавливающего органа, ложные сигналы проходят на выход устройства, и оно теряет работоспособность. Это обусловлено тем, что повторное включение в схему устройства резервируемого блока после его сбоя или отказа осуществляется при совпадении сигнала на его выходе с сигналом на выходе мажоритарного элемента контроля. В результате снижается надежность устройства. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в устройство по авт. св. №506859 в каждый канал введены второй элемент памяти, второй элемент И, элемент задержки и дополнительный мажоритарный элемент, входы которого соединены соответственно с выходами первых элементов памяти других каналов, .

.выход - с дополнительным входом лемента неравнозначности, выход пер ого элемента И соединен со счетным ходом второго -элемента памяти И чеез второй элемент И - со входом усановки в О первого элемента памяи, выход второго элемента памяти оединен со вторым входом второго элемента И, вход установки в О втоого элемента памяти соединен с выодом интегрирующего элемента, а выод восстанавливающего органа соединен через элемент задержки со входом становки в О резервируемого блока.

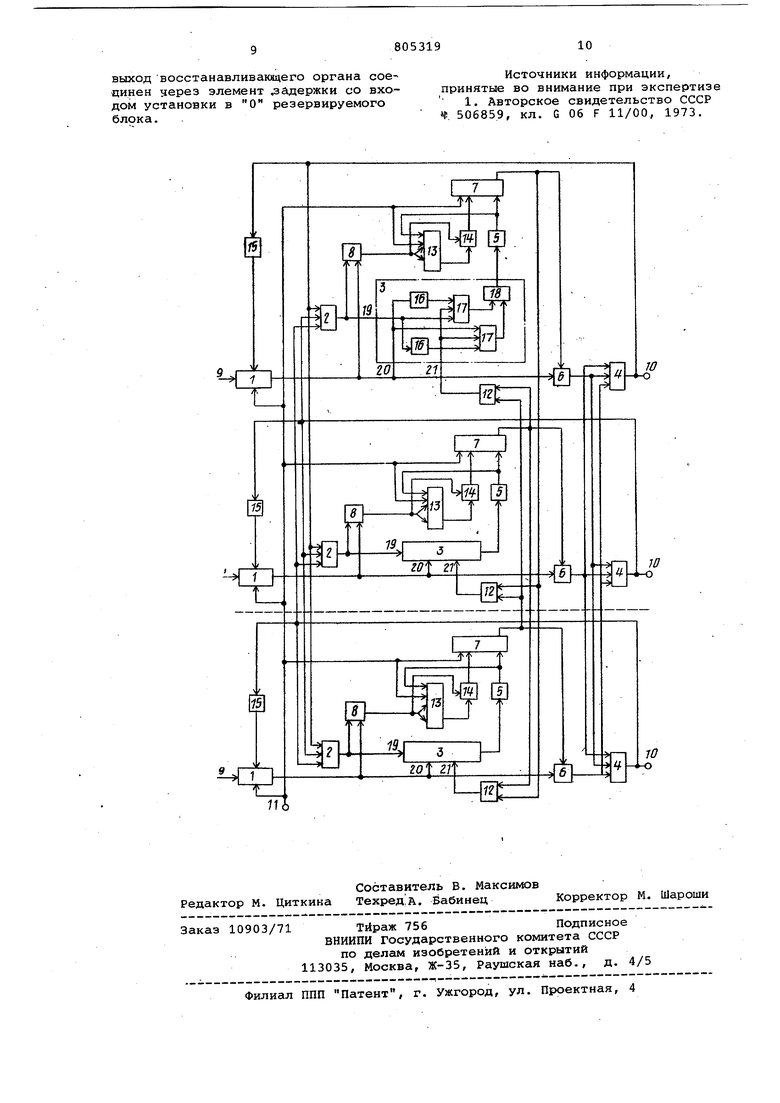

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит в каждом из m каналов резервируемый блок 1 (например счетное устройство), мажори-. тарный элемент 2 контроля, элемент 3 неравнозначности, восстанавливакяций орган 4., интегрирующий элемент 5, элемент б ИЛИ-И первый элемент 7 памяти, первый элемент 8 И, входы 9 резервируемых блоков 1, выходы 10 устройства, вход .11 начальной установки устройства, кроме того, устройство содержит в каждом канале дополнительный мажоритарный элемент 12, второй элемент 13 памяти, второй элемент 14 И и элемент 15 задержки. В состав элемента 3 неравнозначности каждого канала входят элементы 16 НЕ, элемент 17 И и элемент 18 ИЛИ. Входами элемента 3 неравнозначности являются входы 19-21.

Устройство работает следующим образом.

При включении питания первый элемент 1 памяти и второй элемент 13 памяти в каждом канале, а также резервируемый блок 1 (при необходимости) устанавливаются в состояние О сигналом начальной установки, поступакодим на вход 11 начальной установки устройства. В исходном состоянии сигналом с выхода первого элемента 7 памяти разрешено поступление сигнала с выхода резервируемого блока 1 через элемент б ИЛИ-И, а сигналом с выхода второго элемента 13 памяти запрещено поступление сигнала с выхода первого элемента 8 И через второй элемент 14 И. При правильной работе резервируемых блоков 1 сигналы с их выходов поступают через элемент 6 ИЛИ-И на входы восстанавлившощих органов 4 и далее - на выходал 10 устройства. Сигнал с выхода восстанавливающего органа 4 в каждом канале осуществляет (при необходимости) установку резервируемого блока 1 в состояние О через элемент. 15 задержки для подготовки устройства к следукяцему циклу |работы. Кроме того, сигнал с выхода восстанавливающего органа 4 в каждом канале поступает на входы мажоритарного элемента 2 контроля в своем ка

нале и всех остальных каналов. Так как сигналы на входах 19 и 20 элемента 3 неравнозначности совпадают во времени, то на вцходах элемента 18 ИЛИ формирование сигнала не происходит. Вследствие влияния времени срабатывания элементов 6 ИЛИ-И, восстанавливающего органа 4 и мажоритарного элемента 2 контроля возможна задержка сигнала на входе 19 элемента 3 неравнозначности, что может привести к формированию сигнала помехи на выходе элемента 18 ИЛИ. Исключение прохождения кратковременных помех с выхода элемента 18 ИЛИ на единичный вход первого элемента 7 памяти осуществляется с .помощью интегрирукадего элемента 5, которалй может быть выполнен, например, в виде КС-цепочки. Отказ или сбой какого-либо резервируемого блока 1 обнаруживается с помощью элементов 3 неравнозначности, на входы 19 и 20 которых соответственно поступают сигналы с внходов мажоритарного элемента. 2 контроля и резервируемого блока 1 в том же канале. В случае несовпадения сигналов на выходе мажоритарного элемента 2 контроля и резервируемого блока 1 с помощью соответствующей пары элементов 16 НЕ и элементов 17 И формируется сигнал, который через элемент 18 ИЛИ и интегрирующий элемент 5 поступает на единичный вход первого элемента 7 памяти и нулевой вход второго элемента 13 памяти. Сигналом с выхода интегрирукяцего элемента 5 первый элемент 7 памяти устанавливается в состояние 1, при этом на выходе первого элемента 7 памяти формируется управляющий сигнал, который поступает на вход элемента 6 ИЛИ-И. Если в качестве элементов б ИЛИ-И используются элементы И, то управляющий сигнал с выхода первого элемента 7 памяти запрещает прохождение сигнала с неисправного резервируемого блока 1 на входы восстанавливающих : органов 4.Если в качестве элементов ИЛИ-И используются схемы ИЛИ, то управляющий сигнал с выхода первого элемента 7 памяти проходит на входы восстанавливающих органов 4 и уменьшает их по.рог срабатывания на 1. В связи с этим при использовании элементов ИЛИ пороги восстанавливагацих органов 4 должны быть равны m-l, а при -использовании элементов И пороги восстанавливающих органов 4 должны быть раины 2.

Вели первый элемент 7 памяти срабатывает вследствие сбоя резервируемого блока 1, а не вследствие его окончательного отказа, ЧТО обнаруживается при формированиии блоком 1 нормального сигнала в очередных .циклах работы, отключенный канал вновь включается в схему устройства с помощью второго элемента 13 памяти, первого и

второго элементов 8 и 14 И. Это происходит следующим образом. При совпадении сигнала на выходе резервируемого блока 1 с сигналом на выходе мажори гарного элемента 2 контроля на выходе первого элемента 8 И формируется сигнал, который не проходит через второй элемент 14 И, поскольку последний закрыт сигналом с выхода второго элемента 13 Пс1мяти. После спада заднего фронта сигнала на выходе. первого элемента 8 И второй элемент 13 памяти переходит в состояние 1 и подготавливает второй элемент 14 И для прохождения следующего импульса, формируемого на выходе первого элмента 8 И в следующем цикле работы.Если после этого в следующем цикле работы устройства на выходе резервируемого блока 1 формируется сигнал, совпада ощий с сигналом на выходе мажоритарного элемента 2 контроля что свидетельствует о восстановлении работоспособности резервируемого блока 1, то на выходе первого элемента 8 И снова формируется сигнал, который проходит, через открытый второй элемент 14 И на вход установки первого элемента 7 памяти в состояние О. Тем самым разрешается прохождение сигнала с выхода резервируемого блока 1 на входы восстанавливающих органов 4, если в качестве элементов б ИЛИ-И используются элементы И, или восстанавливается (увеличивается на 1) порог срабатывания восстанавливающих органов 4, если в качестве элементов 6 ИЛИ-И использовались элементы ИЛИ. В исходное состояние второй элемент 13 памяти устанавливается после спада заднего фронта сигнал на выходе первого элемента 8 И.

По мере отказа резервируемых блоков -1, например при отказах типа ложная 1 или ложный О, первые элементы 7 памяти в отказавших каналах устанавливаются в состояние 1 и подготавлив ают к срабатыва 1ию мажоритарные элементы 12 во всех каналах кроме своего. Пороги срабатьавания мажоритарных элементов 12 выбираются равнь1ми т-2, чтобы обеспечить форми рование.сигнала на их выходах в правильно работаняцих каналах после того как в устройстве осталось два работоспособных резервируемых бпбка 1. При этом в каждом из двух оставшихся работоспособных каналов сигнал с выхода мажоритарных элементов 12 поступает на вход 21 элемента 3 неравнозначности и запрещает срабатывание элементов 17 И. Тем самым запрещается дальнейшее с рабатывание первых элементов 7 памяти в оставшихся двух работоспособных каналах при несовпадении сигналов на выходах резервируемых блоков 1 и мажоритарных элементов 2 контроля, В случае, если в качестве элементов б ИЛИ-И испольэуются элементы ИЛИ, два оставшихся работоспособ|Ных резервируемых блока 1 оказыва1Ьтся соединенными по схеме ИЛИ, а в случае использования элементов И - по схеме И. Если последующий отказ в первом случае был типа ложный О, а во втором случае - типа ложная 1, то устройство продолжает нормально функционировать при одном оставшемся работоспособном канале. В отказавших каналах функ0ционирование элементов 3 неравнозначности не запрещается. Это необходимо для того, чтобы при отказе, например типа ложная 1, который все время присутствует на выходе неисправ5ного резервируемого блока 1,. не исключалась возможность формирования сигналов на выхода элемента 3 неравнозначности при несовпадении сигналов на его входах 19 и 20 для подтвержде0ния единичного состояния первого элемента 7 памяти и нулевого состояния второго элемента 13 памяти. Это происходит следующим образом. Если на выходе отказавшего резервируемого блока 1 все время присутствует сиг5нал ложная 1, а в устройстве осталось всего два работоспособны х канала,.то.и момент формирования сигнала на выходах 10 устройства, в свою очередь, на выходах первого элеменDта 8 И также формируется сигнал, который приводит к установке в состояние второго Элемента 13 памяти. . Но в момент отсутствия сигналов на выходах 10 устройства и, Следователь5но, на выходах мажоритарных элементов 2 контроля снова формируется сигнал несоответствия на. выходах: элемента 3 неравнозначности в том канале, в котором на выходах резервируемого блока 1 присутствует постоянный

0 сигнал ложная 1, что приводит к подтверждению единичного состояния первого элемента 7 п-амяти и нулевого состояния второго элемента 13 памяти сигналом с выхода интегрирующего эле5мента 5. Тем самым исключается возможность подключения в схему устройства неисправного резервируемого блока 1.

Устройство обеспечивает сохране0ние работоспособности при одном работоспособном канале и в случае, если на выходах отказавших резервируемых блоков 1 формируются сигналы с частотой, превышающей частоту следова5ния полезных сигналов два или более раз. Это происходит следующим образом. Если, например, .частота следования сигналов на выходе первого отказавшего резервируемого блока 1

0 превышает частоту полезных сигналов в два раза, то в момент появления сигнала типа ложная 1 на входе 20 элемента 3 неравнозначности в этом канале фиксируется несоответствие

5 сигналов, и первый элемент 7 пгиляти в этом канале устанавливается в состояние 1, Следующий сигнал на выходе этого отказавшего резервируемого блока 1 уже совпадает по времени с сигналами, формируемыми на выходах исправных резервируемых блоков 1 и, следовательно, с сигналами на выходах мажоритарных элементов 2 контроля во всех каналах, что приводит к установке в состояние 1 второго элемента 13 памяти в отказавшем канале. Очередной сигнал на выходе отказавшего резервируемого блока 1 опять не совпадает с сигналами на вы ходах исправных резервируелйлх блоков 1, в результате чего формируется сигнал на выходе элемента 3 неравнозначности в этом канале, и второй элемент 13 памяти устанавливается в состояние . В результате отказавший резервируелий блок 1 не допускается в схему устройства. Аналогичным образом осуществляет работа устройства и в случае, если на выходах отказавшего резервируемо го блока 1 формируются сигналы с ча -тотой, превышающей частоту следования полезных сигналов более чем в .два р«дза. По мере отказа в последующие моменты времени других резервируемых блоков 1 отказавшие резервируемые блоки 1 постепенно исключаютс из схемы устройства до тех пор, пока в .устройстве не останется два работоспособных блока, как было рассмотрено выше. Для искл10ченр Я влияния сигналов помех, которые могут сформироваться на выходе первого элемента 8 И в мо мент установки неисправного резерви емого блока 1 в состояние О сигна лом с выхода восстанавливающего органа 4, длительность задержки, формируемой элементом 15 задержки, дол на превышать длительность полезных сигналов, формируемых на выходах ре зервируемых блоков 1. Элемент 15 за держки может быть выполнен, например, в виде задержанного мультивибратора (кипп-реле) и дифференцирующей цепи, которая используется для формирования импульса в момент появления заднего фронта сигнала на выходе кипп-реле. В связи с этим, если в момент установки в состояние О неисправного резервируемого блока 1 на его выходе появляются сигналы помех, то они не проходят на выход пер вого . 8 И и, следовательно на счетный вход второго элемента 13 памяти. В то же время указанные сигналы помех в случае их появления поступают через элемент 3 неразнозначмости в отказавшем канале для подтверждения единичного состояния первого элемента 7 памяти и нулевого состояния второго элемента 13 памяти Таким образом, в предлагаемом устройстве за счет введения дополнительных элементов и их связей, во-, первых, возможно сохранение работо-. способности устройства при одном работоспособном резервируемом блоке 1. Это происходит в случае, если последний отказ одного из оставшихся исправных резервируемых блоков 1 был типа ложный О при использовании в качестве элементов 6 ИЛИ-И элементов ИЛИ, или тила ложная 1 при использовании элементов И. Наибольший выигрыш в надежности достигается, если разервируекше блоки 1 имеют неодинаковую вероятность отказов типа ложная 1 и ложный О. Во-вторых, сохраняется работоспособность устройства при одинаковых отказах резервируемых блоков 1 типа ложная 1, например в случае формирования на выходе резервируемых блоков 1 ложных сигналов с частотой, превышающей частоту формирования полезных сигналов. Это обеспечивается тем, что второй элемент 13 памяти позволяет снова ввести в схему устройства ранее отказавший резервируемый блок 1 в случае, е.сли на выходе резервируемого блока 1 дважды формируется правильный сигнал и в промежутках между моментами формирования полезных сигналов отсутствуют ложные сигналы с любой частотой следов ния. Тем самым повышается надежность устройства. Технико-экономическая эффективность от использования предлагаемого устройства определяется уменьшением потерь в системе, использующей данное устройство, за счет повышения его надежности. Формула изобретения Резервированное устройство по авт. св. №506859, отличающееся тем, что, с целью повышения надежности устройства, в каждый его канал введены второй элемент памяти, второй элемент И, элемент задержки и дополнительный мажоритарный элемент, входы которого соединены соответственно с выходами первых элементов памяти других каналов, а выход - с дополнительным входом элемента неравнозначности, выход первого элемента И соединен со счетным входом второго элемента памяти и через второй элемент И - со входом установки в .О первого элемента памяти, выход второго элемента памяти соединен со вторым входом второго элемента И, вход установки в О второго элемента памяти соединен с выходом интегрирующего элемента, а

выход восстанавливающего органа сое динен зерез элемент задержки со входом установки в О резервируемого блока.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-02-15—Публикация

1978-08-07—Подача