(54) РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное устройство | 1973 |

|

SU506859A1 |

| Адаптивное резервированное устройство | 1983 |

|

SU1149264A1 |

| Резервированное устройство | 1979 |

|

SU809674A1 |

| Резервированное устройство | 1980 |

|

SU898634A1 |

| Резервированное устройство | 1978 |

|

SU805319A2 |

| Резервированное устройство | 1991 |

|

SU1785089A1 |

| ТРЕХЭЛЕМЕНТНОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2007 |

|

RU2347264C2 |

| Адаптивное резервированное устройство | 1974 |

|

SU550638A1 |

| Резервированная система | 1982 |

|

SU1089771A1 |

| Резервированное устройство | 1977 |

|

SU661878A1 |

1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для повышения надежности и помехоустойчивости сложных резервированных систем.

Известны резервированные устройства, содержащие резервируемые блоки, индикаторы отказов на каждом из каналов, мажоритарный элемент и блоки формирования веса компенсирующего сигнала Ij,

Однако в этих устройствах каждый сбой резервируемых блоков будет принят за полный отказ блока и соответствующим образом будет форсироваться вес компенсирующего сигнала. Кроме того, поочередные сбои одного резервируемого блока будут приниматься за очередные отказы резервируемых блоков устройства.

Наиболее близким по технической сущности к изобретению является резервированное устройство, содержа1цее в каждом из каналов резервируемый блок, через схему И соединенный с восстанавливающими органами всех каналов, элемент памяти, выход которого подключен ко второму входу элемента И, мажоритарный элемент контроля, входы которого соединены с выходами восстанавливающих органов всех каналов, а выход подключен к одному входу элемента неравнозначности, второй вход которого подключен к выходу резервируемого блока 2.

Недостатком известного устройства является то, что оно не выключает окончательно из устройства отказавшего блока. Так как известное устройство при наличии сбоя или полного отказа одного из резервируемых блоков запрещает проход выходного сигнала

отказавщего блока на вход восстанавливающих органов только на следующем такте (после обнаружения отказа блока) работы устройства, тО при выдаче отказавщим блоком одинаковых логических сигналов (или только 1, или только 0) и при примерно

одинаковой частоте 1 и О на выходе устройства сигналы отказавщего резервируемого блока будут проходить на входы восстанавливающих органов именно тогда, когда они не совпадают с выходными сигналами исправных блоков. Тем самым ухудщаются условия работы восстанавливающих органов, и это может привести к появлению неправильного сигнала на выходах .одного или нескольких восстанавливающих органов.

Целью изобретения явля/ется 1овЬ шение помехоустойчивости устройства.

Эта цель достигается тем, что резервированное устройство, содержащее в каждом из каналов резервируемый блок, через первый элемент И, соединенный с восстанавливающими органами всех каналов, элемент памяти, выход которого подключен ко второму входу первого элемента И, мажоритарный элемент контроля, входы которого соединены с выходами восстанавливающих органов всех каналов, а выход подключен к одному входу первого элемента неравнозначности, второй вход которого подключен к выходу резервируемого блока, содержит в каждом из каналов второй элемент неравнозначности, второй и третий элементы И, резерсивный счетчик. Выход первого элемента неравнозначности подключен к первым входам второго элемента неравнозначности и второго элемента И, вторые входы которых подключены к щине тактовых импульсов. Выход второго элемента И подключен к прямому входу реверсивного счетчика. Выход второго элемента неравнозначности через третий элемент И подключен к реверсивному входу реверсивного счетчика, а второй вход третьего элемента И подключен к выходу нулевого содержимого реверсивного счетчика. Основной выход реверсивного счетчика подключен ко входу элемента памяти, выход которого подключен к весовым входам восстанавливающих органов всех каналов.

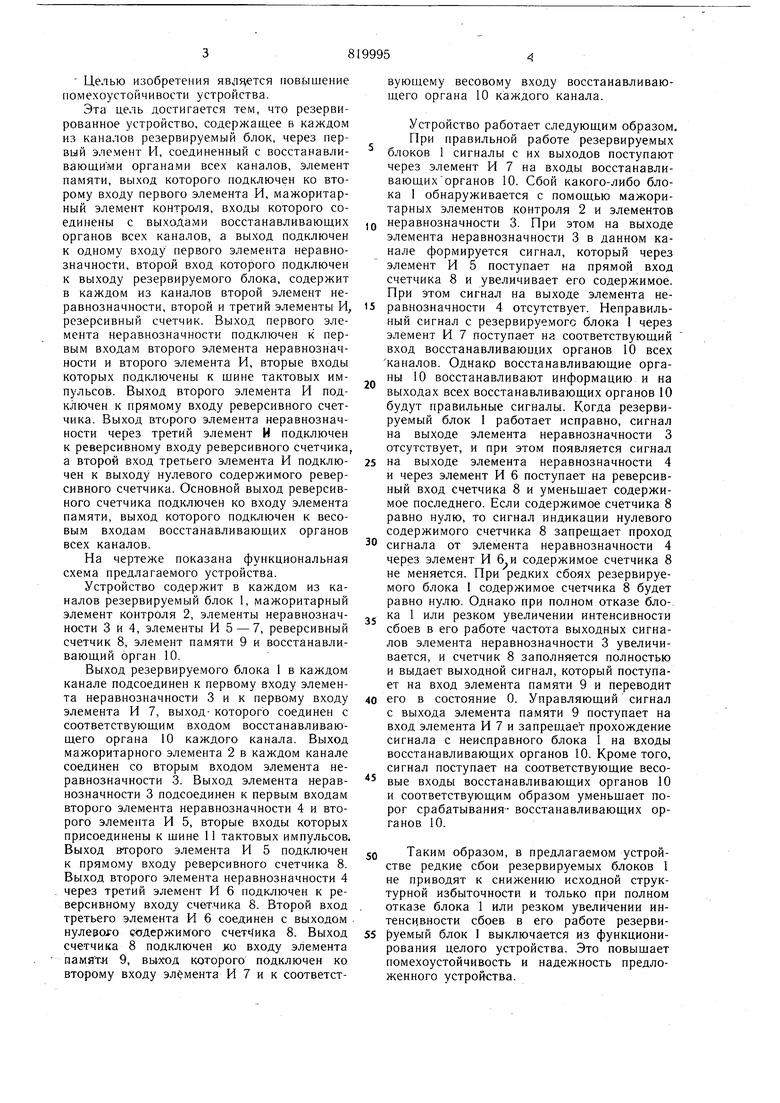

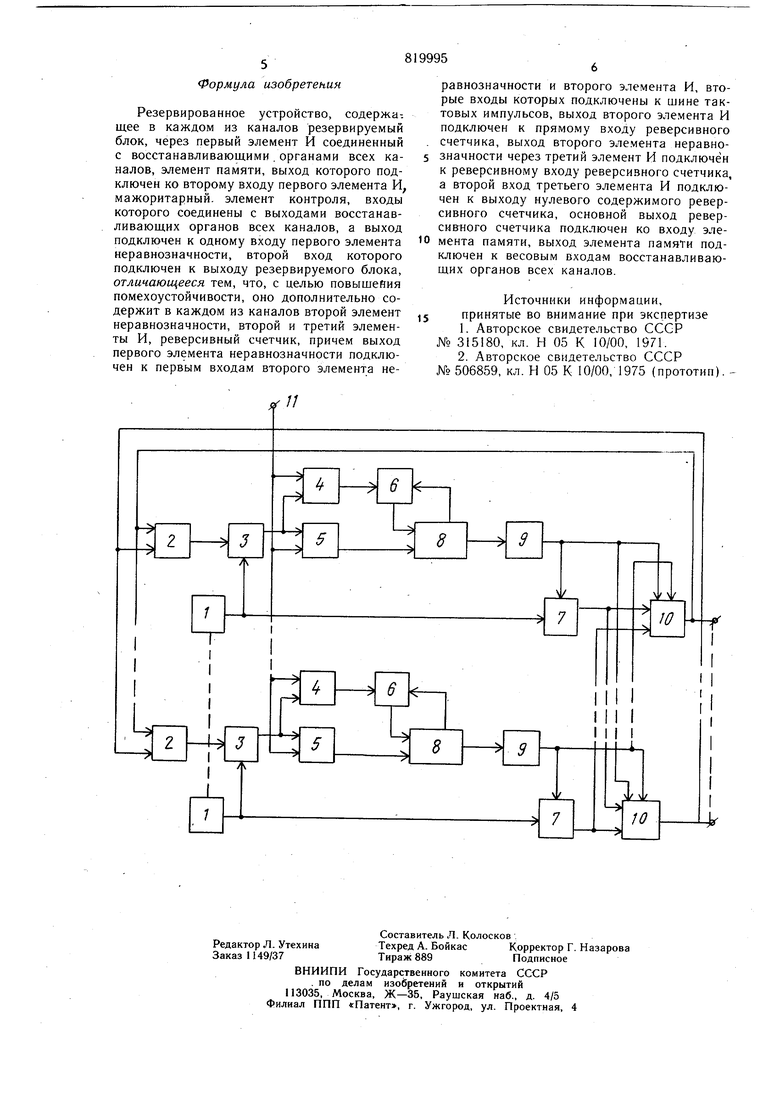

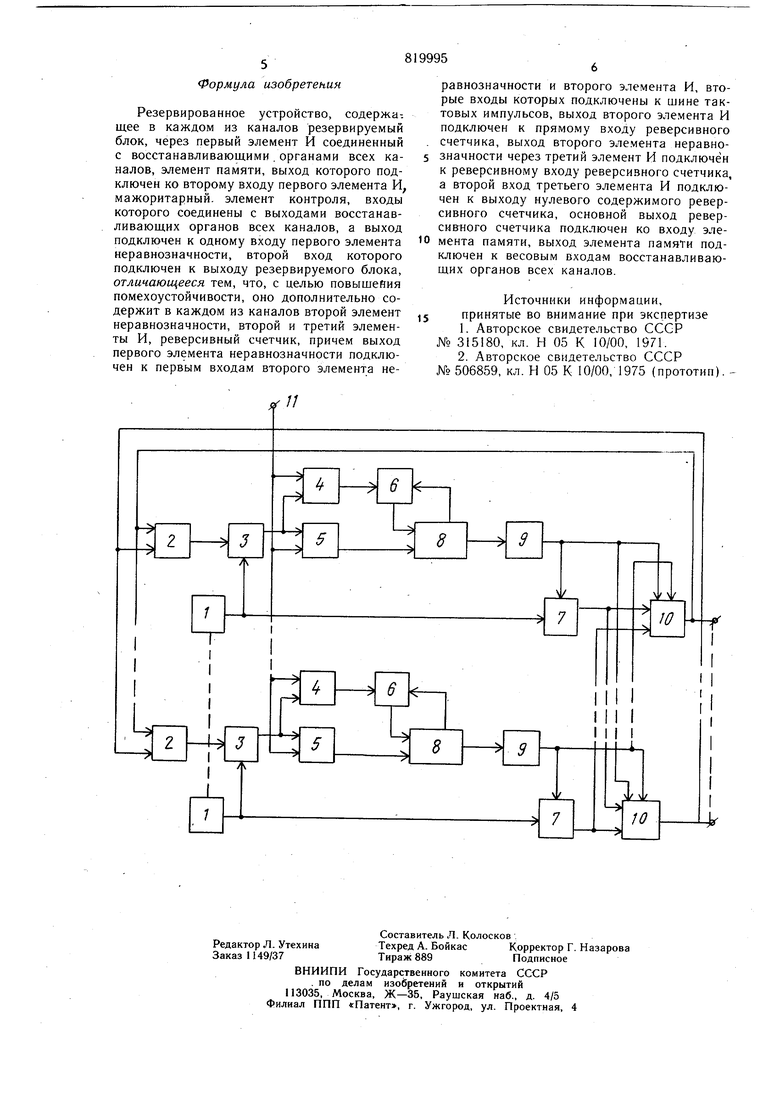

На чертеже показана функциональная схема предлагаемого устройства.

Устройство содержит в каждом из каналов резервируемый блок 1, мажоритарный элемент контроля 2, элементы неравнозначности 3 и 4, элементы И 5 - 7, реверсивный счетчик 8, элемент памяти 9 и восстанавливающий орган 10.

Выход резервируемого блока 1 в каждом канале подсоединен к первому входу элемента неравнозначности 3 и к первому входу элемента И 7, выход- которого соединен с соответствующим входом восстанавливающего органа 10 каждого канала. Выход мажоритарного элемента 2 в каждом канале соединен со вторым входом элемента неравнозначности .3. Выход элемента неравнозначности 3 подсоединен к первым входам второго элемента неравнозначности 4 и второго элемента И 5, вторые входы которых присоединены к шине 11 тактовых импульсов. Выход второго элемента И 5 подключен к прямому входу реверсивного счетчика 8. Выход второго элемента неравнозначности 4 через третий элемент И 6 подключен к реверсивному входу счетчика 8. Второй вход третьего элемента И 6 соединен с выходом . нулеео о содержимого счет(ика 8. Выход счетчика 8 подключен .ко входу элемента памят.и 9, вых-од которого подключен ко второму входу элемента И 7 и к соответствующему весовому входу восстанавливающего органа 10 каждого канала.

Устройство работает следующим образом. При правильной работе резервируемых блоков 1 сигналы с их выходов поступают через элемент И 7 на входы восстанавливающих органов 10. Сбой какого-либо блока 1 обнаруживается с помощью мажоритарных элементов контроля 2 и элементов

неравнозначности 3. При этом на выходе элемента неравнозначности 3 в данном канале формируется сигнал, который через элемент И 5 поступает на прямой вход счетчика 8 и увеличивает его содержимое. При этом сигнал на выходе элемента неравнозначности 4 отсутствует. Неправильный сигнал с резервируемого блока 1 через элемент И 7 поступает на соответствующий вход восстанавливающих органов 10 всех каналов. Однако восстанавливающие органы 10 восстанавливают информацию и на выходах всех восстанавливающих органов 10 будут правильные сигналы. Когда резервируемый блок 1 работает исправно, сигнал на выходе элемента неравнозначности 3 отсутствует, и при этом появляется сигнал

5 на выходе элемента неравнозначности 4 и через элемент И 6 поступает на реверсивный вход счетчика 8 и уменьщает содержимое последнего. Если содержимое счетчика 8 равно нулю, то сигнал индикации нулевого содержимого счетчика 8 запрещает проход

сигнала от элемента неравнозначности 4 через элемент И 6. и содержимое счетчика 8 не меняется. При редких сбоях резервируемого блока 1 содержимое счетчика 8 будет равно нулю. Однако при полном отказе бло, ка 1 или резком увеличении интенсивности сбоев в его работе частота выходных сигналов элемента неравнозначности 3 увеличивается, и счетчик 8 заполняется полностью и выдает выходной сигнал, который поступает на вход элемента памяти 9 и переводит

0 его в состояние 0. Управляющий сигнал с выхода элемента памяти 9 поступает на вход элемента И 7 и запреилает прохождение сигнала с неисправного блока 1 на входы восстанавливающих органов 10. Кроме того, сигнал поступает на соответствующие весовые входы восстанавливающих органов 10 и соответствующим образом уменьшает порог срабатывания- восстанавливающих органов 10.

0 Таким образом, в предлагаемом устройстве редкие сбои резервируемых блоков 1 не приводят к снижению исходной структурной избыточности и только при полном отказе блока 1 или резком увеличении интенсивности сбоев в его работе резерви5 )уемый блок 1 выключается из функционирования целого устройства. Это повыщает помехоустойчивость и надежность предложенного устройства.

Формула изобретения

Резервированное устройство, содержащее в каждом из каналов резервируемый блок, через первый элемент И соединенный с восстанавливающими . органами всех каналов, элемент памяти, выход которого подключен ко второму входу первого элемента И, мажоритарный, элемент контроля, входы которого соединены с выходами восстанавливающих органов всех каналов, а выход подключен к одному входу первого элемента неравнозначности, второй вход которого подключен к выходу резервируемого блока, отличающееся тем, что, с целью повышения помехоустойчивости, оно дополнительно содержит в каждом из каналов второй элемент неравнозначности, второй и третий элементы И, реверсивный счетчик, причем выход первого элемента неравнозначности подключен к первым входам второго элемента неравнозначности и второго элемента И, вторые входы которых подключены к шине тактовых импульсов, выход второго элемента И подключен к прямому входу реверсивного счетчика, выход второго элемента неравнозначности через третий элемент И подключён к реверсивному входу реверсивного счетчика, а второй вход третьего элемента И подключен к выходу нулевого содержимого реверсивного счетчика, основной выход реверсив ного счетчика подключен ко входу элемента памяти, выход элемента памяти подключен к весовым Входам восстанавливающих органов всех каналов.

Источники информации, принятые во внимание при экспертизе

№ 506859, кл. Н 05 К 10/00, 1975 (прототип).

Авторы

Даты

1981-04-07—Публикация

1979-05-22—Подача