1

Изобретение относится к вычислительной технике и может быть применено в схемах адресной выборки запоминающих устройств.

Известны дешифраторы, содержащие схему предварительной дещифрадии с усилителями управляющих токов, элементы связи с односторонней проводимостью и входные и выходные щккы.

Однако малое быстродействие известных дешифраторов обусловлено наличием многообмоточнь х : рансформаторов.

Целью изобретения является повышени быстродействия и уменьшение объема оборудования.

Это достигается тем, что в. дешифраторе допо чнительно установлен преобразоввтель входного кода в наборы нескольких кодов с числом разрядов, меиьшимчисла разрядов входного кода. Причем входы преобразователя входного кода в Ha6opvi нескол1жих кодов с входными шинами, а выходы подключены к кс- noBLiNj входам схем предв ;рктельной деЬиифрсции, усилители угсравл юших токов

которых через элементы с односторонней , проводимостью соединены с выходными шинами.

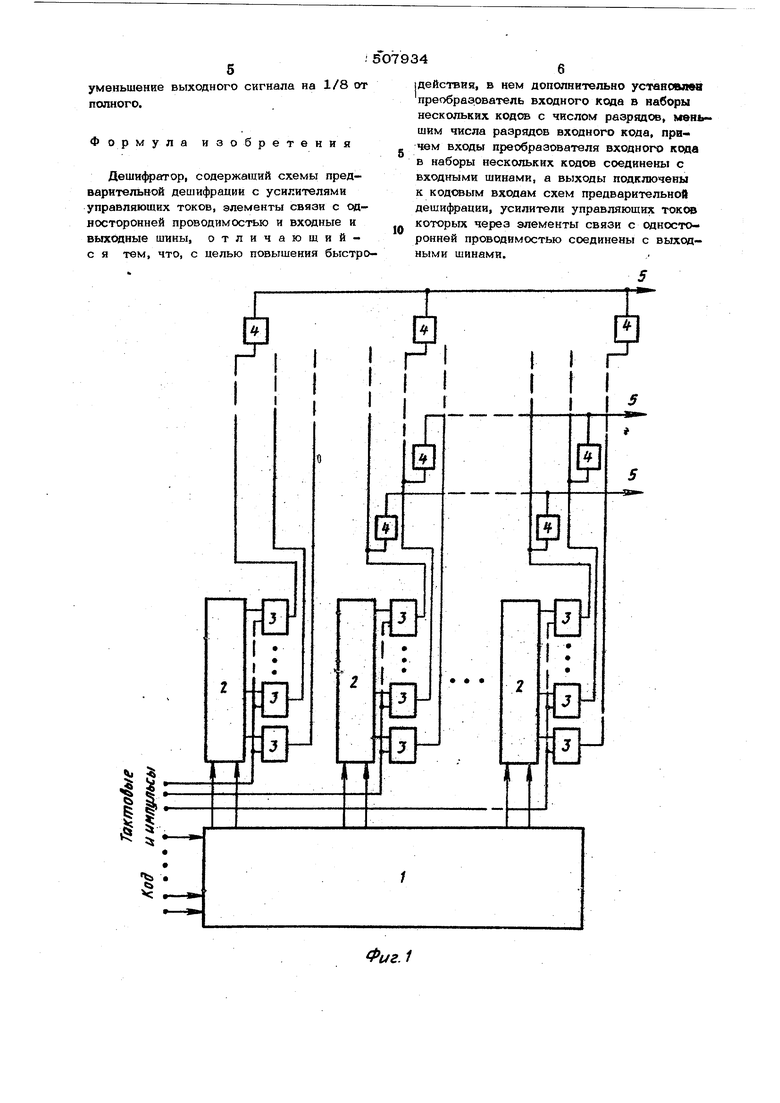

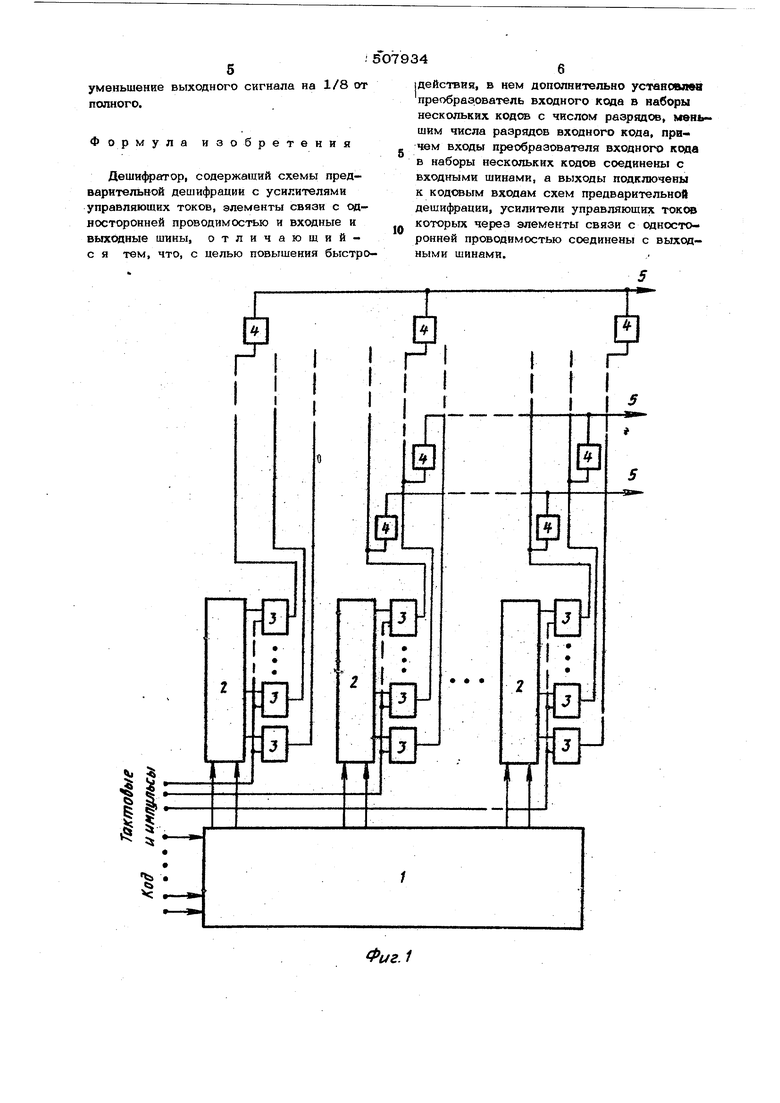

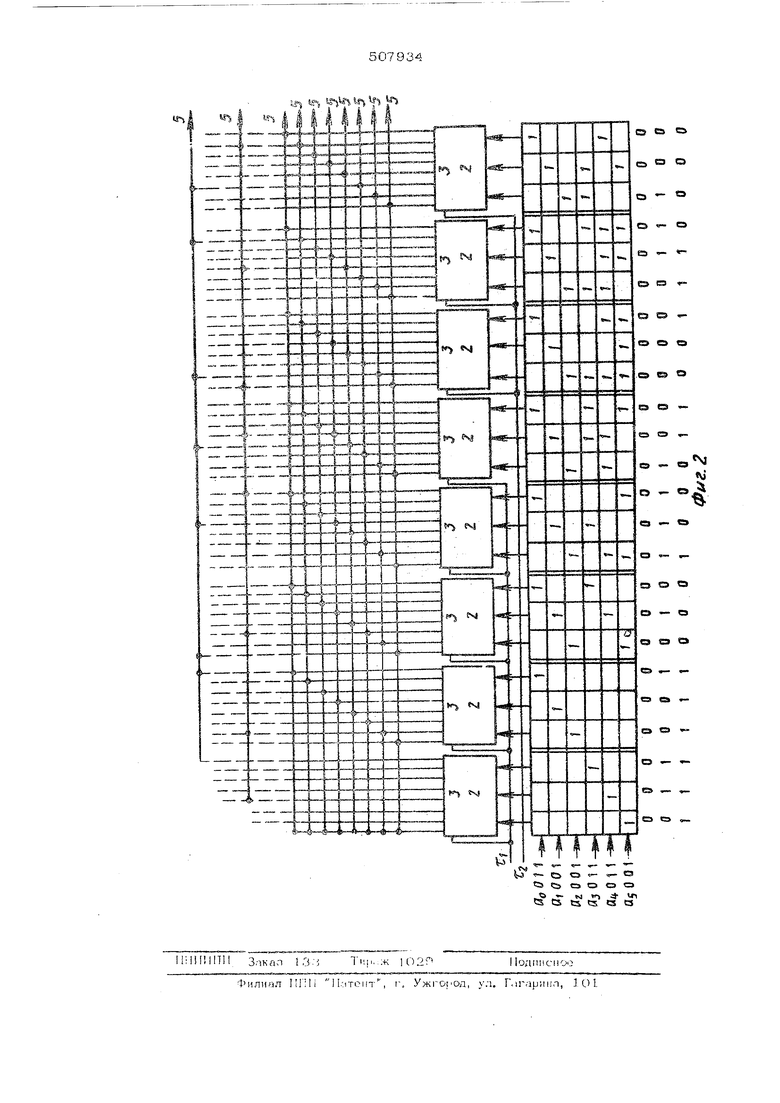

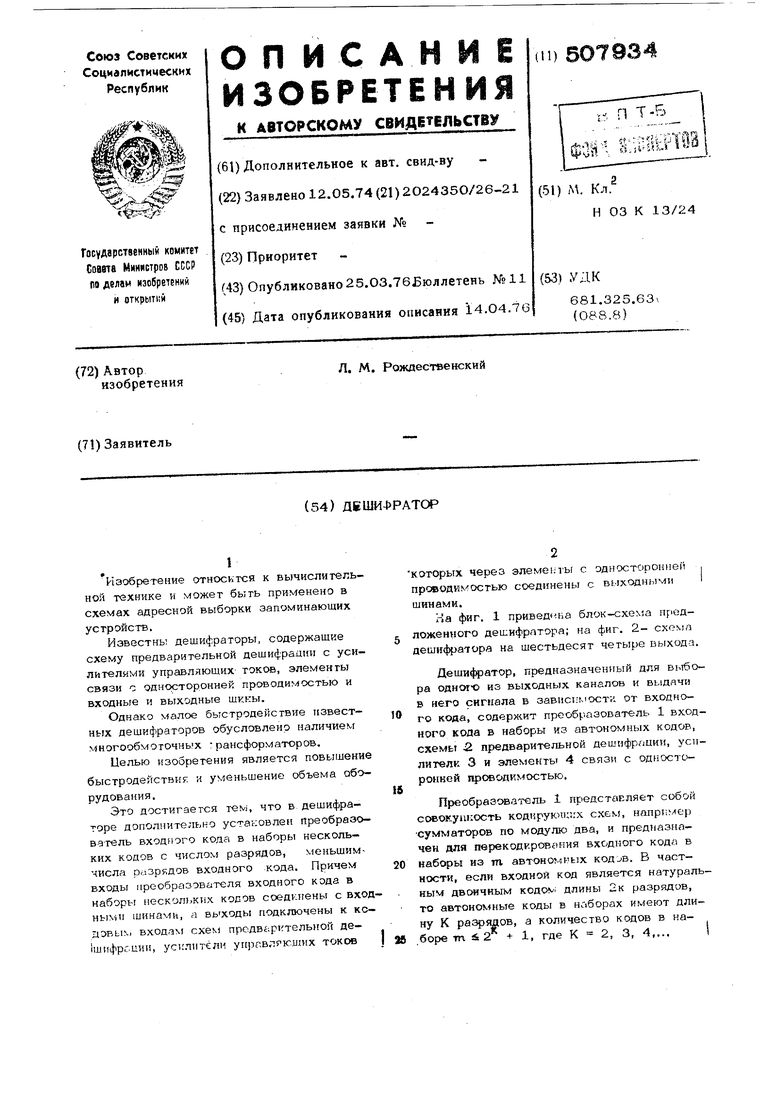

На фиг. 1 привед - на блок-схех а предложенного дешифратора; на фиг. 2- схема дешифратора на шестьдесят четыре выхода.

Дешифратор, предназначенный для выбора одног-о из выходных каналов и выдачи в него сигнала в зависимости от входного кода, содержит преобразователь 1 входного кода в наборы из автономных кодов, схемьт -2 предварительной дешифрации, усилители 3 и элементы 4 связи с од 1остороикей ироводимостью.

Преобразсжатель 1 представляет собой ссжокуикость кодирующих cxe, нaпpI /Iep сумматоров по модулю два, и предназначен для перекодкрования входного кодп в набсфы из тп, автономных . В частности, если ВХОДНОЙ код является натуральным двоичным кодо длины 2к разрядов, го автономные коды в наборах имеют длину К разрядов, а количество кодов в на.боре-mi 2 -t- 1, где К 2, 3, 4,...

Преобразсжатель соединен со схемами 2 так, что входы каждой из них подклю51ЮТСЯ к выходам преобразователя для риема одк то из кодов набора. Каждая схема 2 предварительной деширации представляет собой независимую хему выбора определенных или одного пределенного каналов из многих идентичых в зависимости от поданного на нее т преобразователя 1 кода. Если указаный код яюляется натуральным двоичным, - разрядным кодом, то этими схемами могут быть известные дешифраторы на 2 выходов.

На выходах схем 2 предварительной дешифрации установлены усилители 3 со схемами ссжпадения на два входа, предназначенными для управления запуском усилителей и регулирования уровня напряжения выходного сигнала дешифратора. Выход каждого усилителя 3 через элементы 4 соединен с несколькими выходными шинами 5.

Дешифратор работает следующим образом.

При подаче на дешифратор входного кода в преобразователе 1 происходит перекодирование его в набор кодов, каждый из которых поступает на входы соответствующей схемы 2 предварительной дешифрации. В зависимости от поданных кодов на выходах схем 2 предварительной дешифрации появляются разрешаюшие потенциалы, которые подготавливают связанные с этими выходами усилители 3 к запуску. После одновременного запуска тактирующими импульсами выбранных усилителей токи от этих усилителей через элементь: связи 4 поступбцот на выходные шины 5 дешифратора. На одной из них, где связи отображают данный набор кодов, происходит сложение токов и формирование на нагрузке нормированного сигнала полной амплитуды. На остальных выходах дешифратора возможно появление сигнала помехи от воздействия меньшего числа усилителей. Регулирование амплитуды сигнала на выходе дешифратора осуществляется путем блокирования; запуска определенного числа выбранных усилителей схем 2 предварительной дешифрации.

Схема дешифратора на шестьдесят четыре выхода (фиг. 2) имеет преобразователь 1, который изображен в виде таблицы из шести строк и двадцати четырех столбцов с единицами в определенных точках их пересечения.

Преобразователь 1 содержит двадцать четыре сумматора по модулю два и предназначен для перекодирования входного . шестнразрядного двоичного кода в наборьт из восьми трехразрядных кодсж.

На фиг. 2 сумматоры представлены

столбцами, где единицами отмечено наличие связи сумматоров с определенными

разрядами входного кода: а, о.,а

а количество единиц в столбце равно числу входов у сумматоров. Например, первый,

второй шестой сумматоры имеют по

одному входу, и электрическая схема каждого из них не содержит ни одного элемента, так как каждая шина входного кода непосредственно соединена с соответствующим входом схем 2 предварительной дешифреции. Седьмой двухвходовый сумматор реализует функцию: OL-Q. va-cx 1;

1-5

a.-agVajj-ag tQ. -i.

Преобразователь содержит девять двух0

входовых сумматоров. Трехвходовый и четырехвходовый сумматоры по модулю два могут быть выполнены соответственно из двух и трех двухвходовых сумматоров. Электрическая схема преобразсжателя может

5 быть выполнена из десяти микросхем, содержащих по три сумматора по модулю два в каждом.

Схемами 2 предварительной аешкфра- ции являются известные дешифраторы на

0 три входа и восемь выходов, которые имеют по восемь усилителей 3 на выходе и каждый из усилителей через элементы связи соединен с восемью выходными шинами 5 дешифратора. Элементы связи с односторонней проводимостью (например, диоды) на фиг. 2 изображены точками.

При подаче на входы дешифратора любой двоичной комбинации, длиной шесть разрядов, на преобразователе происходит

0 перекодирование этой последовательности в набор из восьми трехразрядных кодов. После дешифрации каждого кода на схемах 2 появляется потенциал, подготавли- ваюший один из усилителей 3. При одновременной подаче импульсов tr. и t срабатывают восемь усилителей, токи от которых через элементы связи поступают непосредственно на одну выбранную шину, где формируют сигнал полной амплитуды.

Если эти импульсы подаются раздельно, то на этой же шине формируются выходные сигналы амплитудой: 5/8 и 3/8 от полной соответственно. Одновременно

5 во всех случаях на невыбранных шинах возникает помеха амплитудой 1/8 от полного сигнала. При выходе из строя любого одного элемента дешифратор продолжает функционировать, однако при этом

возможно увеличение помехи до 2/8 или

уменьшение выходного сигнала на 1/8 от полного.

Формула изобретения

Дешифратор, содержащий схемы предварительной дешифрации с усилителями управляющих токов, элементы связи с односторонней проводимостью и входные и выходные шины, отличающийс я тем, что, с целью повышения быстрошействня, в нем дополнительно устаяоал в преобразователь входного кода в наборы нескольких кодов с числом разрадов, меньшим числа разрядов входного кода, при «ЮМ входы преобразователя входного кода в наборы нескольких кодов соединены с входными шинами, а выходы подключены к кодсаым входам схем предварительной дешифрации, усилители управляющих токов которых через элементы связи с односторонней проводимостью соединены с выходными шинами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1977 |

|

SU695364A1 |

| Устройство для сопряжения процессора с устройствами ввода-вывода | 1983 |

|

SU1129602A1 |

| СПОСОБ И УСТРОЙСТВО СИНТЕЗА, ПЕРЕДАЧИ, ПРИЕМА, АНАЛИЗА И ОЦЕНКИ МНОГОВАРИАНТНЫХ ПО ФОРМЕ, МНОГОПОЗИЦИОННЫХ И ЛОКАЛЬНЫХ ПО СПЕКТРУ СИГНАЛОВ | 2000 |

|

RU2160509C1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Модуль интеллектуальной электроэнергетики | 2016 |

|

RU2630777C1 |

| Устройство для записи цифровой информации | 1987 |

|

SU1490690A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU839046A1 |

| Цифро-аналоговый многофункциональный преобразователь | 1982 |

|

SU1062732A2 |

| АБОНЕНТСКИЙ ПУНКТ В СИСТЕМЕ БЕСПРОВОДНОЙ ЦИФРОВОЙ ТЕЛЕФОННОЙ СВЯЗИ | 1990 |

|

RU2154360C2 |

| ИНФОРМАЦИОННО-ИЗМЕРИТЕЛЬНЫЙ КАНАЛ ГИДРОАКУСТИЧЕСКОЙ ЦИФРОВОЙ ПРИЕМНОЙ СИСТЕМЫ | 1994 |

|

RU2077066C1 |

Фиг.1

Авторы

Даты

1976-03-25—Публикация

1974-05-12—Подача