итерации подключен к управляюи1ему входу дешифратора множителя.

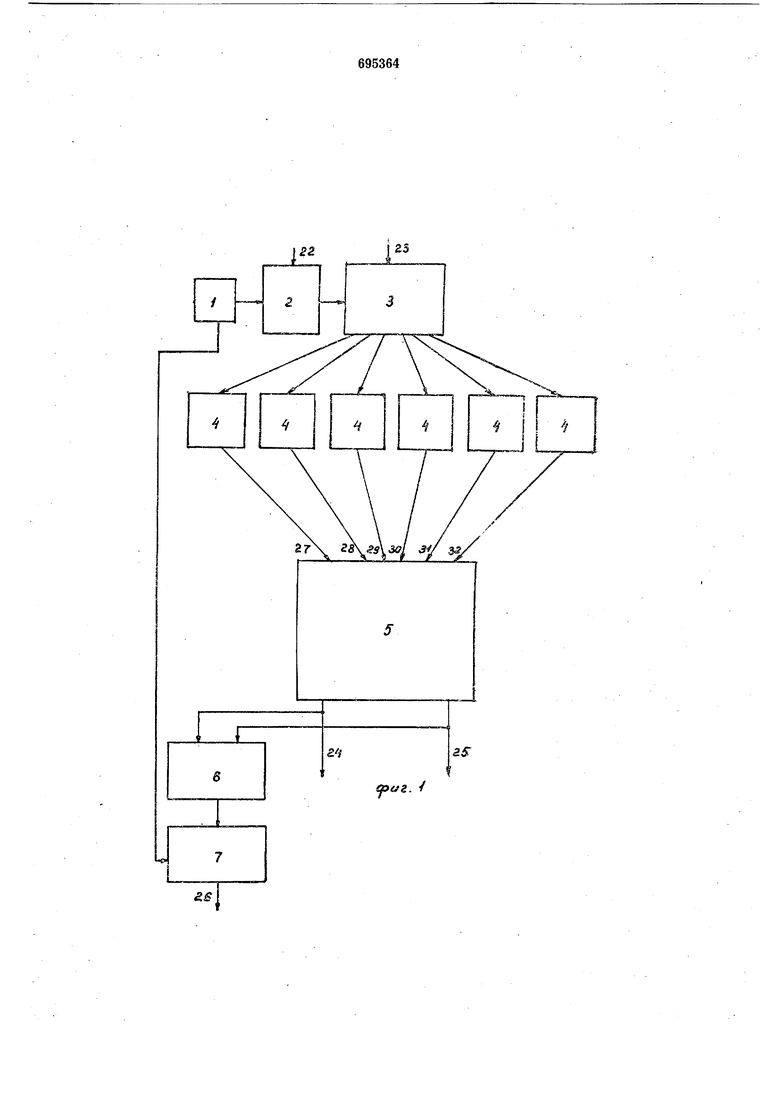

На фиг. 1 представлена схема устройства для умножепия; на фиг. 2 - схема дерева сум.матора.

В состав устройства входят счетчик итераций 1, дешифратор множителя 2, коммутатор кратных 3, регистры кратных 4, дерево сумматоров 5 с сохранением переносов; сумматор с расиростраиением переносов 6, регистр младшей части произведения 7, трехвходовые сумматоры с сохранением переносов 8-13, буферные регистры 14-16 первого уровня, буферные регистры 17-19 второго уровня, буферные регистры 20,21 третьего уровня (они же выходные регистры сумм и переносов дерева сумматоров 5); входная шина множителя 22, входная шина множимого 23,

выходная шина сумм старшей части произведения 24, выходная шина переносов

старшей части произведения 25, выходная

шина младшей части произведения 26,

в.ходные шины дерева сумматоров 27-32.

Итерации умножения в предложенном

устройстве начинаются с иодачи на вход

коммутатора кратных 3 по входной шине

23 множимого, а на вход дешифратора

множителя 2 по входной шине 22 множителя (в случае умножения чисел с плаваюш,ей точкой - нормализованных мантисс множимого и множителя). Счетчик итераций 1 управляет последовательностью

дешифрации групп разрядов множителя в дешифраторе 2 и записью цифр младшей части произведения в регистр 7. Производится дешифрация младших двенадцати разрядов множителя. Дешифрация каждой

пары разрядов множителя производится в соответствии со следуюшей таблицей.

Перенос в i Выходной сигнал дешифратора множителя, принимающий елипичное значение

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1983 |

|

SU1129606A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1348836A1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| Устройство для умножения двоичныхчиСЕл B дОпОлНиТЕльНыХ КОдАХ | 1979 |

|

SU813420A1 |

| Устройство для умножения | 1978 |

|

SU705448A1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

Здесь: ПК - сигнал, управляющий подачей в соответствующий регистр кратного 4 множимого в прямом коде; Л1 - сигнал, управляющий подачей в регистр кратного 4 множимого, сдвинутого влево па один разряд; ОК - сигнал, управляющий подачей в регистр кратного 4 множимого в обратном коде. Прочерк в графе таблицы означает, что все выходные сигналы дешифратора находятся в нулевом состоянии.

После коммутации в коммутаторе 3 шесть кратных множимому принимаются на регистры кратных 4. С регистров кратных 4 кратные поступают на входы дерева сумматоров 5, где производится их суммирование. Для звеличеиия быстродействия применяется метод конвейерной обработки информации в дереве, сумматоров 5. Для этого введены три уровня буферных регистров. Первый уровень составляют регистры 14-16, второй уровень-регистры 17-19, третий уровень - регистры 20и2Ь которые являются также выходными регистрами сумм и переносов старшей части произведения.

В то время, как информация первой итерации, обработанная на логике первого, уровня дерева сумматоров 5 (сумматоры

1К

J1I

О К

ПК

Л1

ОК

8, 9 и 10), поступает на буферные регистры 14-16 первого уровня, на дешифраторе множителя 2 производится дешифрация следующих двенадцати разрядов множителя (начинается вторая итерация). Когда информация первой итерации после обработки на втором уровне дерева сумматоров 5 (сумматоры И и 12) поступает на буферные регистры 17-19 второго уровня, кратные множимому, сформированные во второй итерации, принимаются на регистры кратных 4 и поступают на входы дерева сумматоров 5 по входным щинам дерева сумматоров 27-32.

Одновременно с приемом информации первой итерации в виде сумм и переносов частичного произведения на буферные регистры 20, 21 третьего уровня осуществляется дешифрация очередной группы разрядов множителя (начинается третья итерация), а информация второй итерации прииимается на буферные регистры 14-16 первого уровня. Таким образом, осуществляется совмещение во времени итераций умножения.

Результат итераций умножения (частичное произведение) в виде сумм и переносов, полученных на регистрах 20 и 21 дерева сумматоров 5, сдвигается на двегнадцать разрядов вправо и прибавляется к результату следующей итерации на стадии его формирования. По мере выполнения итераций на регистрах 20 и 21 ироизводится накапливание старшей части произведения в коде с сохранением переносов.

Выдвинутые двеиадцать разрядов частичного произведения в виде сумм и переносов поступают по выходным шинам 24 и 25 на входы сумматора 6, где происходит приведение переносов. Полученные три шестнадцатиричные цифры младшей части произведения запоминаются в соответствующих разрядах регистра 7. Записью на этот регистр цифр младшей части произведения управляет счетчик итераций 1. Сумматор 6 формирует также единицу переноса из вьь двинутой части частичного произведения, которая может возникнуть при приведении переносов. Эта единица добавляется в пос.ледний разряд регистра 21 переносов частичного произведения. Умножение чисел с фиксированной точкой выполняется за три итерации. Умножение чисел с плавающей точкой выполняется за пять итераций.

После окончания итераций старшая часть результата в коде с сохранением переносов сформирована в регистрах 20, 21 сумм и переносов дерева сумматоров 5. Младшая часть произведения сформирована в регистре младшей части произведения 7.

При перемножении чисел с фиксированной точкой и в случае перемножения чисел с плавающей точкой, когда не требуется результат расширенного формата, младшая часть результата игнорируется.

Использование данного устройства в составе арифметическо-логического блока процессора позволяет выполнять наряду с операциями умножения чисел с фиксированной точкой и операциями умножения коротких тл длинных операндов с плаваюшей точкой такие операции, как преобразование длинных сомножителей с плавающей точкой (длина манти.ссы - 56 двоичных разрядов) в произведении расщиренного формата (длина мантиссы 112 двоичных разрядов) и операции умножения операндов с плавающей точкой расширенного формата

(

Формула изобретения

Устройство для умножения, содержащее счетчик итераций, дешифратор множителя, коммутатор кратных, регистры кратных, дерево сумматоров, причем входы дешифратора множителя и коммутатора кратных соединены с шинами множителя и множимого

соответственно, выход дешифратора множителя подключен к другому входу коммутатора кратных, выходы которых подключены ко входам регистров кратных, выходы

которых подключены к входам дерева сумматоров, выходы которого соединены с выходными шинами старшей части произведения, отличающееся тем, что, с целью повышения точности, устройство содержит

сумматор с распространением переносов и регистр младшей части произведения, причем входы сумматора с распространением переносов подключены к выходам дерева сумматоров, а выход подключен к входу регистра младшей части произведения, управляющий вход которого подключен к выходу счетчика итераций, а выход - к выходной щине младшей части произведения, выход счетчика итераций подключен куправляющему входу дешифратора множителя.

Источники информации, принятые во внимание при экспертизе:

«Советское радио, 1970, с. 133-180.

ai

W V-3J/

as:

ag. /

271 2S| 2913 i 3/1

H 1- V

7

7

/-

/

/7

e.

CptfS.

Авторы

Даты

1982-01-07—Публикация

1977-06-06—Подача