1

Изобретение относится к вычислительной технике и может -быть применено для контроля сумматоров ЭВМ.

Известно устройство для контроля сумматора, содержащее первый усилитель и связанные с его входом суммирующие резисторы. Известное устройство характеризуется недостоверностью получаемой информации об обнаружении ощибок из-за большого разброса уровня выходных напряжений логических элементов.

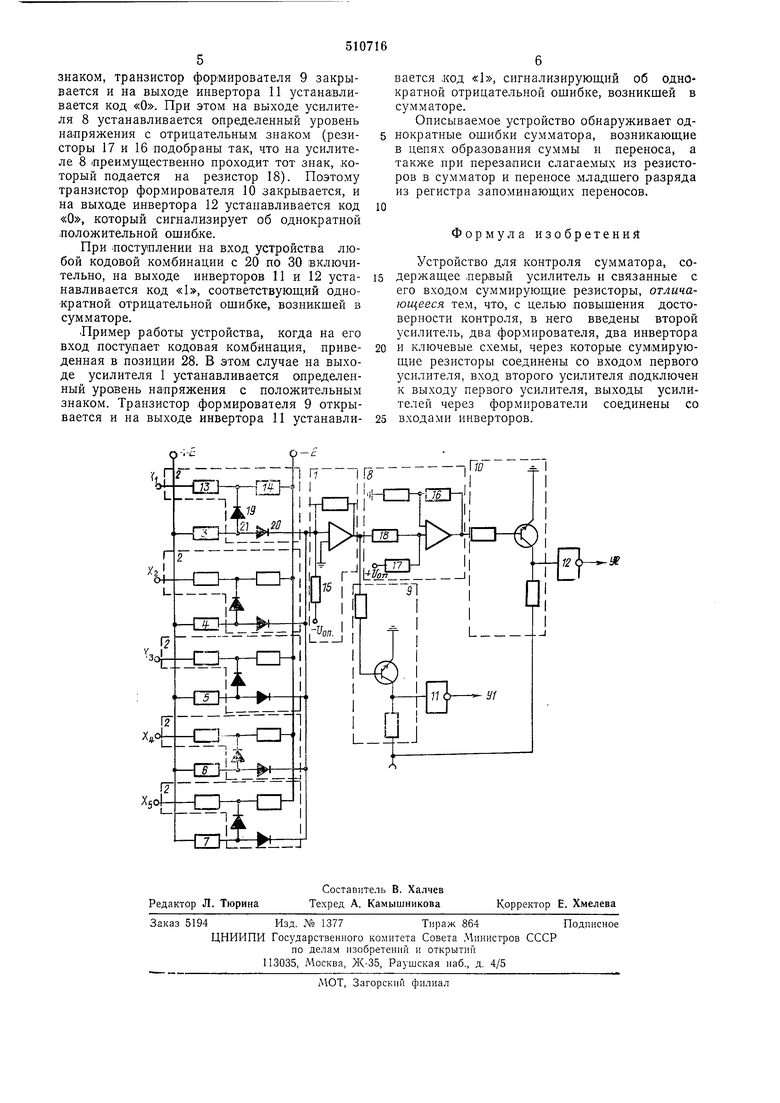

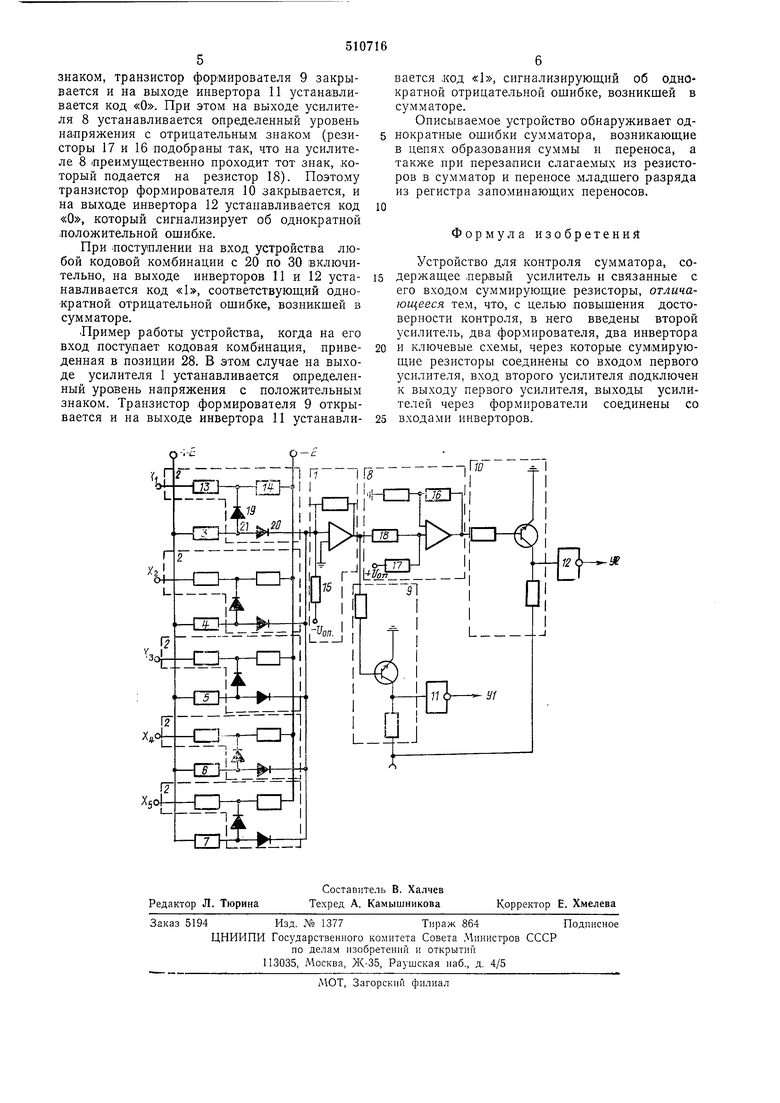

Цель изобретения - повысить достоверность контроля. В описываемом устройстве это достигается тем, что в пего введены второй усилитель, два формирователя, два инвертора и ключевые схемы, через которые суммирующие резисторы соединены со входом первого усилителя, вход второго усилителя подключен к выходу первого усилителя, выходы усилителей через формирователи соединены со входами инверторов.

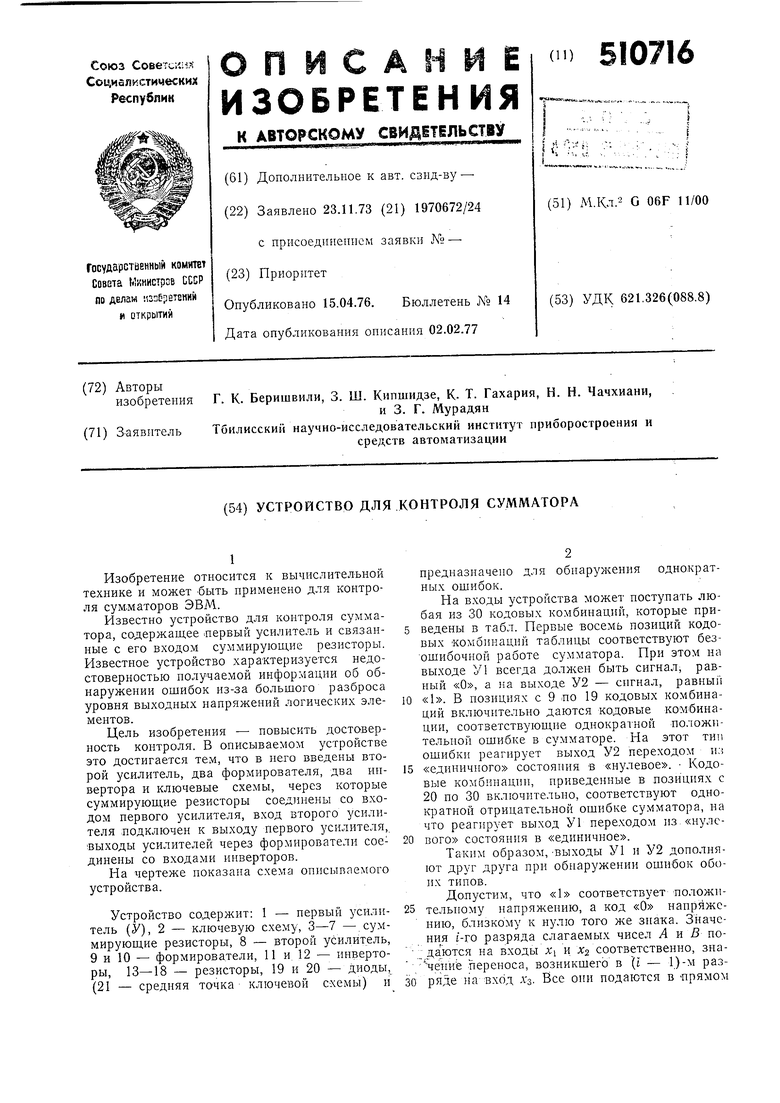

На чертеже показана схема описываемого устройства.

Устройство содержит: 1 - первый усилитель (У), 2 - ключевую схему, 3-7 -.суммирующие резисторы, 8 - второй усилитель, 9 и 10 - формирователи, 11 и, 12 - инверторы, 13-18 - резисторы, 19 и 20 - диоды, (21 - средняя точка ключевой схемы) и

предназначено для обнаружения однократных ощибок.

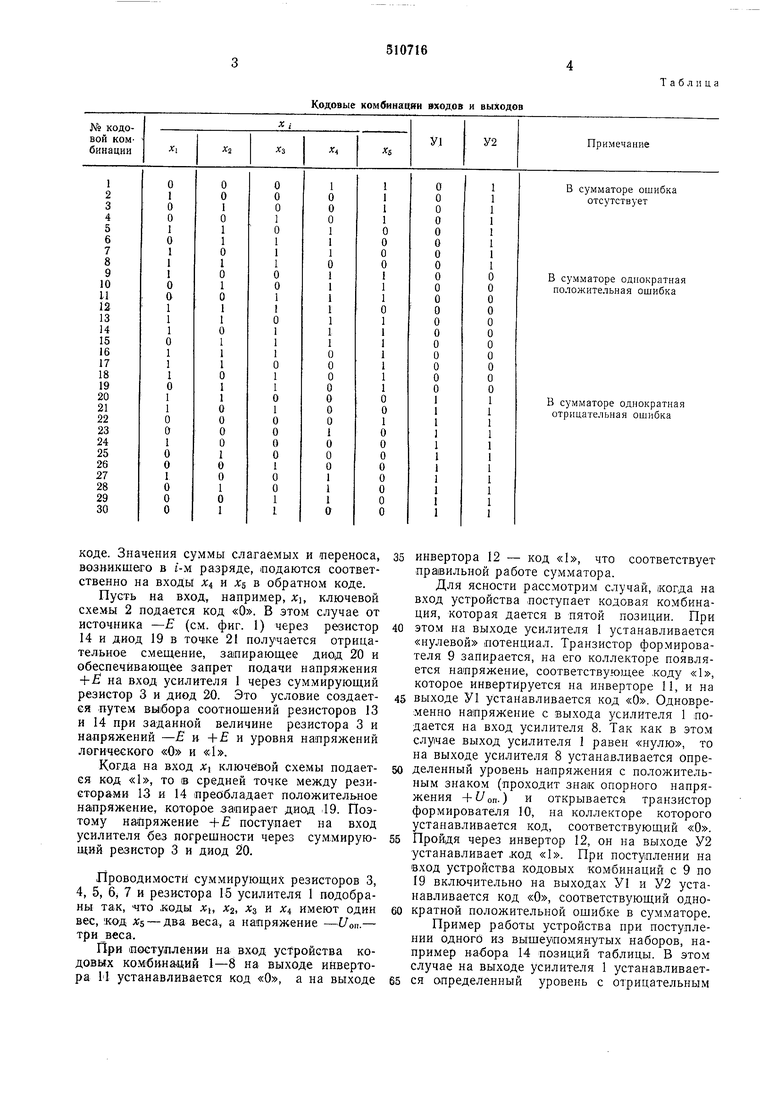

На входы устройства может поступать любая из 30 кодовых комбинаций, которые приведены в табл. Первые восемь позиций кодовых комбинаций таблицы соответствуют безощибочной работе сумматора. При этом на выходе У1 всегда быть сигнал, равный «О, а на выходе У2 - сигнал, pasHbiii

«1. В позициях с 9 по 19 кодовых комбинаций включительно даются кодовые комбинации, соответствующие однократной положительной ошибке в сумматоре. На этот тип ошибки реагирует выход У2 переходом и;;

«единичного состояния в «ну.тевое. Кодовые комбинации, приведенные в позициях с 20 по 30 включительно, соответствуют однократной отрицательной ошибке сумматора, на что реагирует выход У1 переходом пз,«нулсвого состояния в «единичное.

Таким образом, -выходы У1 п У2 дополняют друг друга при обнаружении ощибок обоих типов.

Допустим, что «Ь соответствует положительиому напряжению, а код «О напряжению, близкому к нулю того же знака. Значения i-ro разряда слагаемых чисел Л и В пода ся на входы Xi и х соответственно, зпачениё переноса, возникшего в (I - 1)-м разряде на ВХОД лз. Все они подаются в прямом

Кодовые комбинацяи вход.ов и выходов

Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ | 1972 |

|

SU335689A1 |

| Формирователь импульсов | 1986 |

|

SU1411945A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Формирователь импульсов | 1989 |

|

SU1751843A1 |

| Устройство для контроля качества дискретного канала связи | 1990 |

|

SU1702533A1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1446695A1 |

| Суммирующий аналого-цифровой преобразователь | 1988 |

|

SU1617638A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1601754A1 |

| УСТРОЙСТВО для СРАВНЕНИЯ ДВУХ ПАРАЛЛЕЛЬНЫХ ДВОИЧНЫХ КОДОВ | 1969 |

|

SU254202A1 |

коде. Значения суммы слагаемых и переноса, возникшего в i-м разряде, подаются соответственно на входы х и Х5 ъ обратном коде.

Пусть на вход, например, х, ключевой схемы 2 подается код «О. В этом случае от источника -Е (см. фиг. 1) через резистор 14 и диод 19 в 21 получается отрицательное смещение, затирающее диод 20 и обеспечивающее запрет подачи напряжения +Ё на вход усилителя 1 через суммирующий резистор 3 и диод 20. Это условие создается путем вы1бора соотношений резисторов 13 и 14 при заданной величине резистора 3 и напряжений -Е и + и уровня напряжений логического «О и «1.

Когда на вход Xi ключе вой схемы подается код «1, то в средней точке между резисторами 13 и 14 преобладает положительное напряжение, которое запирает диод il9. Поэтому на1пряжение +Е поступает на вход усилителя без погрешности через суммирующий резистор 3 и диод 20.

Проводимости суммирующих резисторов 3, 4, 5, 6, 7 и резистора 15 усилителя 1 подобраны так, что коды Xi, х, л;з н х имеют один вес, код Х , - два веса, а напряжение -f/on.- три веса.

При поступлении на вход устройства кодовых комбинаций 1-8 на выходе инвертора М устанавливается код «О, а на выходе

инвертора 12 - код «I, что соответствует правильной работе сумматора.

Для ясности рассмотрим случай, когда на вход устройства поступает кодовая комбинация, которая дается в пятой позиции. При

этом на выходе усилителя 1 устанавливается «нулевой потенциал. Транзистор формирователя 9 запирается, на его коллекторе появляется напряжение, соответствующее коду «1, которое инвертируется на инверторе 11, и на

выходе У1 устанавливается код «О. Одновременно напряжение с выхода усилителя 1 подается на вход усилителя 8. Так как в этом случае выход усилителя 1 равен «нулю, то на выходе усилителя 8 устанавливается определенный уровень напряжения с положительным знаком (проходит знак опорного напряжения 4-f/on.) и открывается транзистор формирователя 10, на коллекторе которого устанавливается код, соответствующий «О.

Пройдя через инвертор 12, он на выходе У2 устанавливает код «I. При поступлении на вход устройства кодовых комбинаций с 9 по 19 включительно на выходах У1 и У2 устанавливается код «О, соответствующий однократной положительной ошибке в сумматоре. Пример работы устройства при поступлении одного из вышеупомянутых наборов, например на.бора 14 позиций таблицы. В этом случае на выходе усилителя 1 устанавливается определенный уровень с отрицательным

Авторы

Даты

1976-04-15—Публикация

1973-11-23—Подача