Изобретение относится к устройствам контроля и может использоваться для анализа состояния каналов связи, подверженных воздействию помех, приводящих к появлению ошибок группового характера (каналы с памятью).

Поток ошибок в дискретном канале может быть аппроксимирован стационарной цепью Маркова с двумя состояниями, для которой матрица переходных вероятностей имеет вид

Р Роо POI г РюРи

(D

где PIJ - вероятность перехода из i-ro состояния в J-e (i, ,1).

Факт группирования отражается выполнением известного математического соотношения (1):

Роо Рои РП Рю.(2)

Частным случаем модели Маркова является канал без памяти (с независимым

характером искажений), для которого математическое описание определяется условием (1):

Poo Pro; Pii Poi.(3)

Каждое из соотношений (2) и (3) представляет собой группу из двух совместных событий, поэтому обобщенная количественная оценка может быть получена на основе произведения двух частных показателей, вычисляемых их тождественным преобразованием. Один из вариантов тождественных преобразований позволяет получить для неравенства (2):

Роо

П

Р01

и для (3)

Роо

Р01

1

PIU, Рю

Р11

Рю

1

1

СО

с

VJ о ю ел

00

со

Окончательная формула оценки будет Роо ;Рп

POI Рю.

(4)

Таким образом, в качестве критерия принятия решения о памяти канала можно

рекомендовать показатель (4) и следующее правило принятия решения: если у 1 . то принимается решение, что канал без памяти ; в противном случае( ) - канал с памятью. Так как

Poo-1-Poi:Pn-1-Pio.(5)

то возможна запись следующего вида:

Poo-Si РоП

Pn-Sa Рю ),

где Si, ,2,3 Тогда выражение (4)

будет

„ Si POI S2 Рю1ел

Y PoTHPlo (6)

Значение (6) связано со степенью памяти (уровенем памяти) канала, т.е. каждому значению(6) соответствует определенный уровень памяти канала, что позволяет, анализируя (4) или (6), идентифицировать состояние канала в зависимости от памяти.

Согласно (2), элементы матрицы (1) с учетом (5) оцениваются так:

Р Р(0.2т). р1 -Р(0.2т)

Роо Р() р11-2- (0,т)

(7)

где Р(0, Jm) - вероятность правильного приема кодового блока (комбинации) длины jmO5). После соответствующих преобра- зований с учетом (5) и (7) получим

1 -2Р(0.гп)-Р(0.2т). П11 - Р (0,т)

Pni- Р(0.т)-Р(0.2т)(в}

р°1Р(0,т)(8)

Р,п- Р(0.т)-Р(0.2т) Г1°1-Р(0,2т)

Тогда значение (4) можно определить, подставляя (8) в (4), как

P(0.2m)1-2-P(0.m) + P(0.2m) (0,m)-P(0,2m)f

W50

Следовательно, идентификация канала по указанному выше критерию (9) требует произвести оценивание вероятности P(0,Jm) правильного приема кодового блока (комбинации) длиной jm(,2). которая g5 может быть определена любым из известных способов. Вероятность Р(0,т) пред- ставляет собой частоту появления случайной величины ci(. 2,...), принимающей значение 1 (правильный прием кодового блока длины т) и 0 ( в противном случае), которая, согласно (3), определяется как

Р(о.т) 1+-п- + х -р-п, (10)

где п - длина интервала наблюдения. Преобразуем (10) следующим образом:

xi -f ... +хп -1 хп

Dnт

нпПП

и умножим и разделим первое слагаемое на величину (п-1). Тогда получим

л

Рп

1

Х1 + ... +ХП

1 + -

П

пп - 1

кончательная оценка будет иметь вид

ХП - Рп -1

Рп Р п 1 +

п

(11)

где рп-1 оценка, полученная на предыдущем шаге (п-1).

Вероятность Р(0,2т) представляет собой частоту появления случайной величины zi(H1.2,...), принимающей значение 1 (правильный прием двух соседних кодовых блоков, т.е. на длине 2т) и 0 (в противном случае, т.е. когда хотя бы один или два подряд следующих блока искажены), которая с учетом ранее рассмотренных тождественных преобразований будет

P(0,2m)

ii +... +zn -1 + zn n - 1

Z1 + .. +Zn -1

п - 1

+

n

in n

35

A, Zn - q n - 1

Ч п 1 „

(12)

0

5

0

5

Цель изобретения - повышение оперативности контроля состояния канала связи.

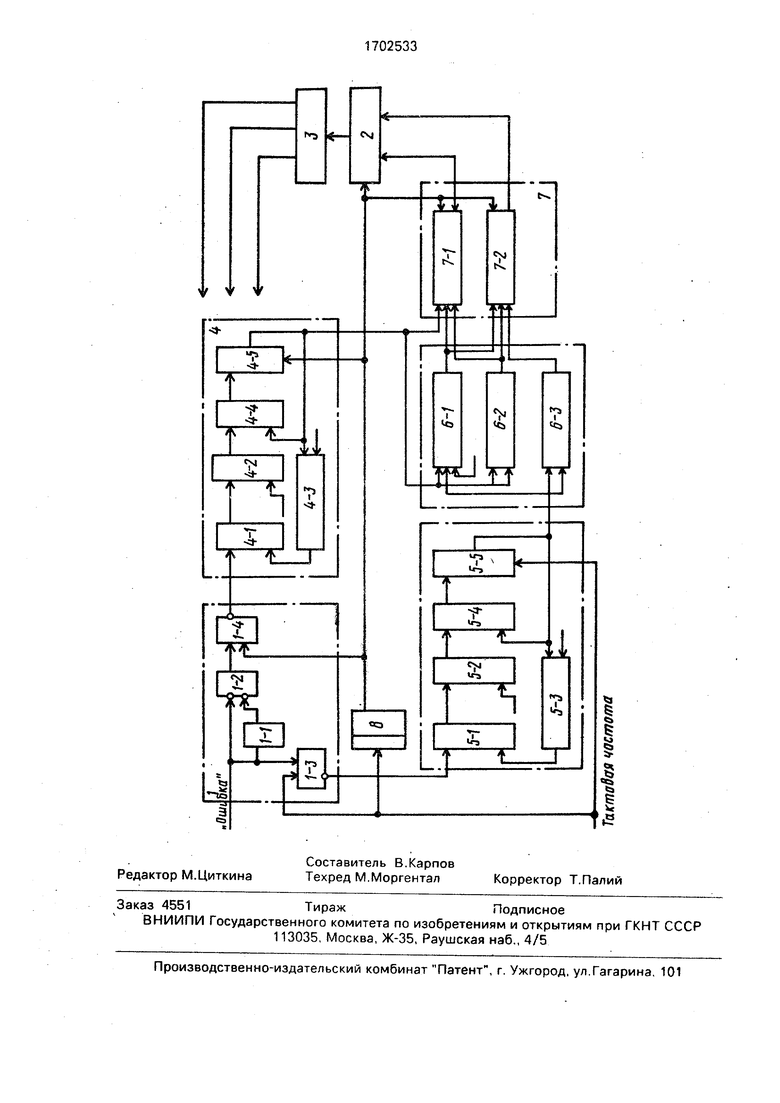

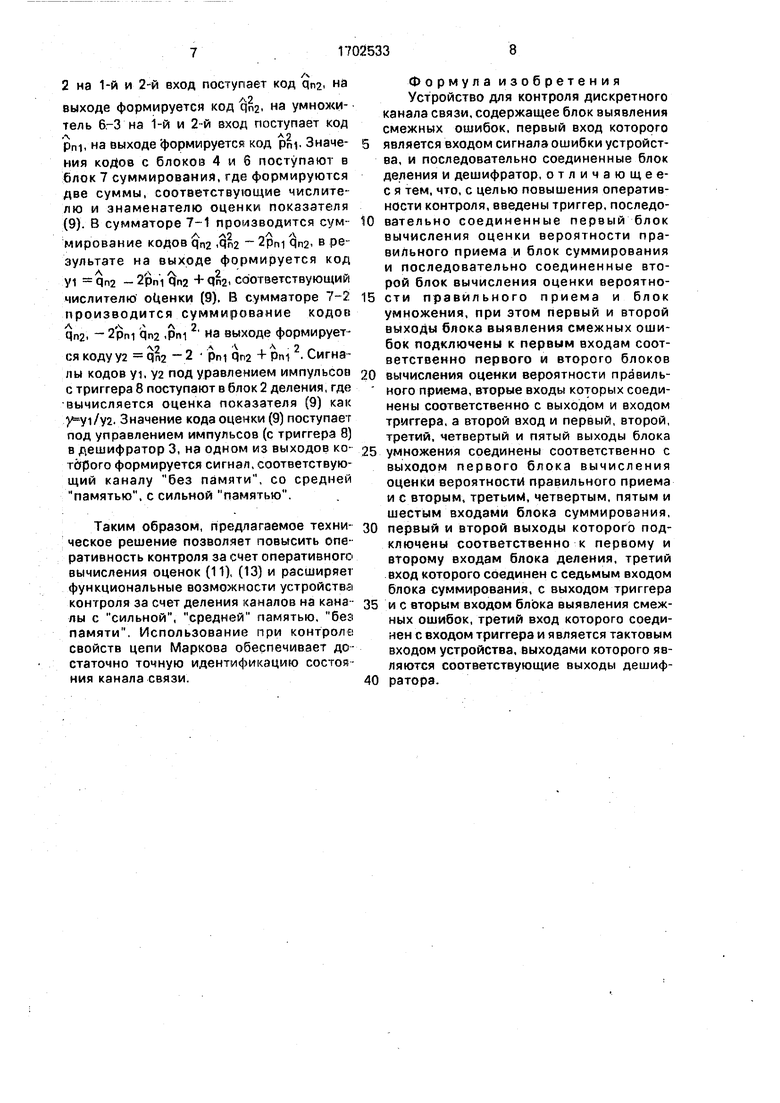

Устройство для контроля качества дискретного канала связи изображено на чертеже.

Устройство содержит блок 1 выявления смежных ошибок, блок 2 деления, дешифратор 3. блоки 4, 5 вычисления оценки вероятности правильного приема, блок 6 умножения, блок 7 суммирования, триггер 8. Блок 1 содержит элемент задержки 1-1, элементы И 1-2, 1-3, 1-4. Блоки 4, 5 вычисления оценки вероятности правильного приема содержат сумматоры 4-1, 5-1. умножители 4-2, 4-3, 5-2, 5-3, сумматоры 4-4, 5-4, регистры 4-5, 5-5. Блок 6 умножения содержит умножители 6-1,6-2,6-3. Блок 7 суммирования содержит сумматоры 7-1. 7-2.

Устройство для контроля качества дискретного канала связи работает следующим образом.

Сигналы из дискретного канала связи через блок выявления ошибок (на чертеже не показан) поступают на блок 1, выполняющий функции формирования случайных последовательностей признаков приема на длине одной кодовой комбинации xi и на длине двух кодовых комбинаций zi, На входе блока 1 - сигнал xi, соответствующий признаку правильного приема (при ) или обнаруженной ошибки (). Этот сигнал, стробируемый тактовой частотой, через элемент И 1-3 в виде признака х с инверсного выхода поступает в блок 5 вычисления оценки вероятности правильного приема, где формируется оценка (11). Одновременно элементы И 1-2, 1-3, 1-4 формируют случайную последовательность , каждое значение которой при правильном приеме двух смежных кодовых комбинаций (правильный прием на длине двух Смежных кодовых комбинаций) и - в противном случае (когда хотя бы одна или две подряд смежные комбинации искажены). Таким образом, эти элементы формируют сигнал в соответствии с функцией F xi-ixj+ xi, ,2,.. . Формированиесигнала xi-1 осуществляется путем задержки сигнала элементом задержки 1-1 на время передачи (приема) кодовой комбинации. Сигнал Zi с выхода элемента И 1-2 поступает на вход И 1-4, где тактируется сигналом с выхода триггера 8. Этот сигнал формируется из сигнала Тактовая частота путем деления его на два триггером 8. С инверсного выхода И 1-4 значение сигнала zj под управлением импульсов триггера 8 (в два раза реже) поступает в блок 4. Следовательно, блок 1 формирует две последовательности сигналов xi и zi, поступающие в блоки 4 и 5 с различной частотой: xi поступает в два раза чаще, чем zi, поэтому и блок 4 вычисляет оценку (12) в два раза реже, чем блок 5 вычисляет оценку (11).

Рассмотрим работу блока 5 вычисления оценки вероятности правильного приема.

Перед началом работы в регистре 5-5 устанавливается начальное значение оценки (11) ро, которое может быть произвольным, т.к. через несколько тактов это значение примет реальную величину, или может быть выбрано как среднее значение вероятности правильного приема кодовой комбинации длины т, предварительно вычисленное после снятия статистики ошибок реального канала. Значение xi поступает на вход сумматора Ь-1, на другой вход которого подается код величины оценки р0. предварительно в умножителе 5-3 умноженный на код. С выхода сумматора 5-1 формируется код, соответствующий значению (xi-fJo). который в умножителе 5-2 умножается на код (1/ni). На 1-й выход сумматора 5-4 поступает код с умножителя 5-2, равный 5 (xi-po)/ni, на 2-й вход- код ро. в результате с сумматора 5-4 в регистр 5-5 записывается значение оценки (11) на 1-м шаге:

(xi-pNo).

0 При следующем поступлении значения Х2 производятся вычисления аналогично отмеченным выше, в результате на выходе регистра 5-5 получим код р2 pi+(x2-pi)/ni. Таким образом, продолжая

5 аналогичные вычисления после каждого шага испытания xi на выходе регистра 5-5 будут формироваться коды оценки (11). каждый из которых сигналом тактовой частоты будет считываться с регистра 5-5 в

0 блок б умножения.

Аналогично работает блок 4, однако входным сигналом для него является zi, a частота работы в два раза реже. Перед на5 чалом работы в регистре 4-5 устанавливается начальное значение оценки (12) qV выбираемое произвольно или как среднее значение вероятности правильного приема на длине двух кодовых комбинаций, предва0 рительно вычисленное после снятия статистики ошибок реального канала. Значение zi поступает на вход сумматора 4-1, на другой вход - код оценки q0, предварительно умноженный в умножителе 4-3 на код. На

5 выходе сумматора 4-1 - код (), который в умножителе 4-2 умножается на код (1 /па). В результате этого на 1-й вход сумматора 4-4 поступает код (zi-qo)/n2, который суммируется с кодом q0, а итоговая сумма

0 (zi-qo)/n2 записывается в регистр 4-5. При поступлении сигнала Z2 в блок 4 процесс вычисления повторяется аналогично, в результате в регистр 4-5 записывается значение q2 qi+ (z2-qi)/n2.

5 Продолжая аналогичные вычисления с поступлением каждого последующего значения zi, на выходе регистра 4 5 получим коды оценки (12) после каждого испытания; каждый из кодов сигналом с выхода

0 триггера 8 (в два раза реже, чем тактовая частота) считывается с регистра 4-5 в блок 6 умножения.

В дальнейшем на основе вычисленных 5 оценок (11) и (12) производится вычисление оценки показателя (9) следующим образом. На умножитель 6-1 поступают коды qn2. Рги и код (-2), в результате на выходе формируется код -2qn2 Pni, на умножитель 62 на 1-й и 2-й вход поступает код Qnj. на

л9

выходе формируется код qn2- на умножитель 6-3 на 1-й и 2-й вход поступает код Pni. на выходе формируется код pni- Значения кодов с блоков 4 и б поступают в блок 7 суммирования, где формируются две суммы, соответствующие числителю и знаменателю оценки показателя (9). В сумматоре 7-1 производится суммирование кодов дП2 .Qn2 2pni Чп2- в Ре зультате на выходе формируется код yi qn2 -2pn1qn2 + Qn2. соответствующий числителю оЦенки (9). В сумматоре 7-2 производится суммирование кодов

qn2, - 2рщ Qn2 -Pni 2- на выходе формирует VOА. ЧА У

СЯ КОДУ У2 Qn2 - 2 Pni Qn2 + Pn1 . СиГНЭлы кодов yi. y2 под уравлением импульсов с триггера 8 поступают в блок 2 деления, где вычисляется оценка показателя (9) как } У1/У2. Значение кода оценки (9) поступает под управлением импульсов (с триггера 8) в дешифратор 3, на одном из выходов которого формируется сигнал, соответствующий каналу без памяти, со средней памятью, с сильной памятью.

Таким образом, предлагаемое техническое решение позволяет повысить оперативность контроля за счет оперативного вычисления оценок (11), (13) и расширяет функциональные возможности устройства контроля за счет деления каналов на каналы с сильной, средней памятью, без памяти, Использование при контроле свойств цепи Маркова обеспечивает достаточно точную идентификацию состояния канала связи.

Формула изобретения Устройство для контроля дискретного канала связи, содержащее блок выявления смежных ошибок, первый вход которого

является входом сигнала ошибки устройства, и последовательно соединенные блок деления и дешифратор, отличающее- с я тем, что, с целью повышения оперативности контроля, введены триггер, последовательно соединенные первый блок вычисления оценки вероятности правильного приема и блок суммирования и последовательно соединенные второй блок вычисления оценки вероятности правильного приема и блок умножения, при этом первый и второй выходы блока выявления смежных ошибок подключены к первым входам соответственно первого и второго блоков

вычисления оценки вероятности прёвиль- ного приема, вторые входы которых соединены соответственно с выходом и входом триггера, а второй вход и первый, второй, третий, четвертый и пятый выходы блока

умножения соединены соответственно с выходом первого блока вычисления оценки вероятности правильного приема и с вторым, третьим, четвертым, пятым и шестым входами блока суммирования,

первый и второй выходы которого подключены соответственно к первому и второму входам блока деления, третий вход которого соединен с седьмым входом блока суммирования, с выходом триггера

и с вторым входом блока выявления смежных ошибок, третий вход которого соединен с входом триггера и является тактовым входом устройства, выходами которого являются соответствующие выходы дешифратора.

I I

I

.«3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля качества канала связи | 1990 |

|

SU1709544A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА СВЯЗИ | 1991 |

|

RU2050693C1 |

| Устройство контроля дискретных каналов | 1989 |

|

SU1707770A1 |

| Устройство передачи и приема шумоподобных сигналов | 1989 |

|

SU1707771A1 |

| Устройство для контроля качества канала связи | 1990 |

|

SU1716610A2 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1601754A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

| Устройство для оценки качества канала связи | 1983 |

|

SU1117847A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение оперативности контроля. Устр-во содержит блок 1 выявления смежных ошибок, блок 2 деления, дешифратор 3, блоки 4, 5 вы исле- ния оценки вероятности правильного приема, блок 6 умножения, блок 7 суммирования, триггер 8. Оперативная оценка вероятности правильного приема кодовых блоков одинарной и двойной длины и используемая модель Маркова позволяют идентифицировать состояние дискретного канала после приема каждого кодового блока. 1 ил.

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-12-30—Публикация

1990-06-28—Подача