1

Изобретение относится к электросвязи и может использоваться в системах передачи ч приема дискретной информации.

Известно устройство для фазового пуска, содержапдее счетчик ошибок и регистр сдвига с сумматором в цепи обратной связи, причем выходы регистра сдвцга через селекторы подключены к входам блока управления.

Однако известное устройство имеет низкую помехоустойчивость вследствие ограниченного числа корректируемых ошибок по сравнепию с нотенциально возможным числом.

Цель изобретения - повышение номехоустойчивости.

Это достигается тем, что в предлагаемом устройстве между выходом счетчика ошибок и соответствующим входом блока управления включен блок последовательной регистрации, к другому входу которого подключен выход одного из селекторов через последовательно соединенные дополнительные ключи, схему логического сложения PI распределитель.

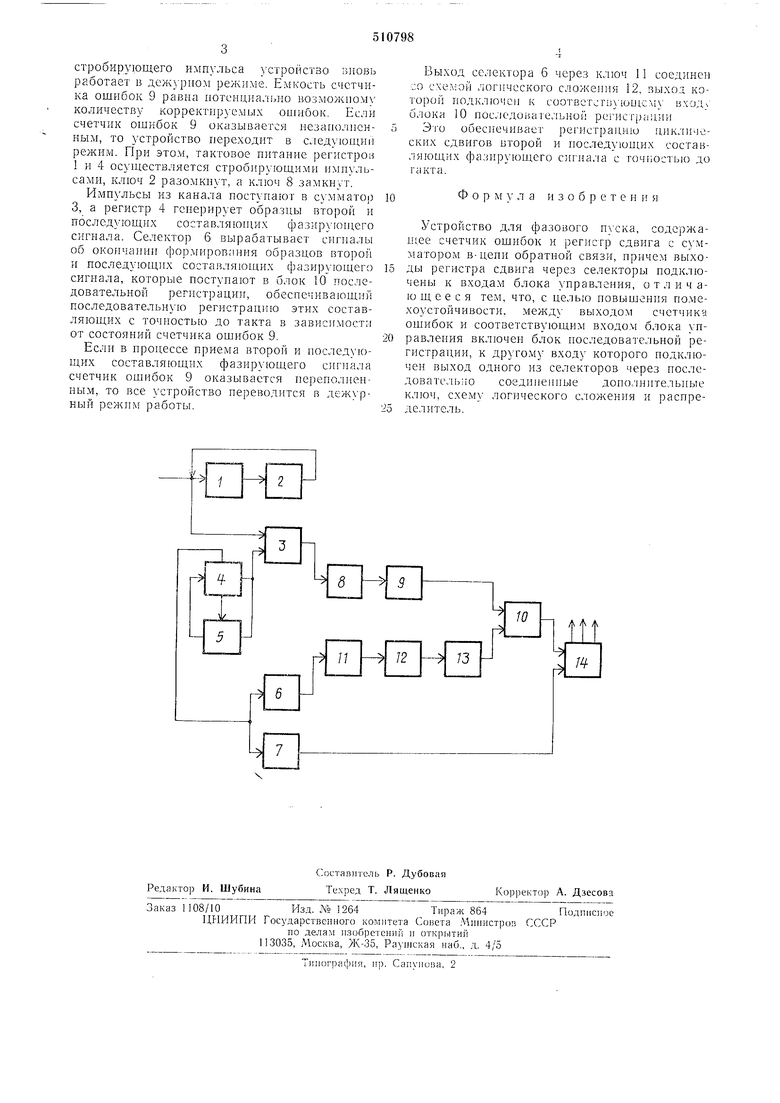

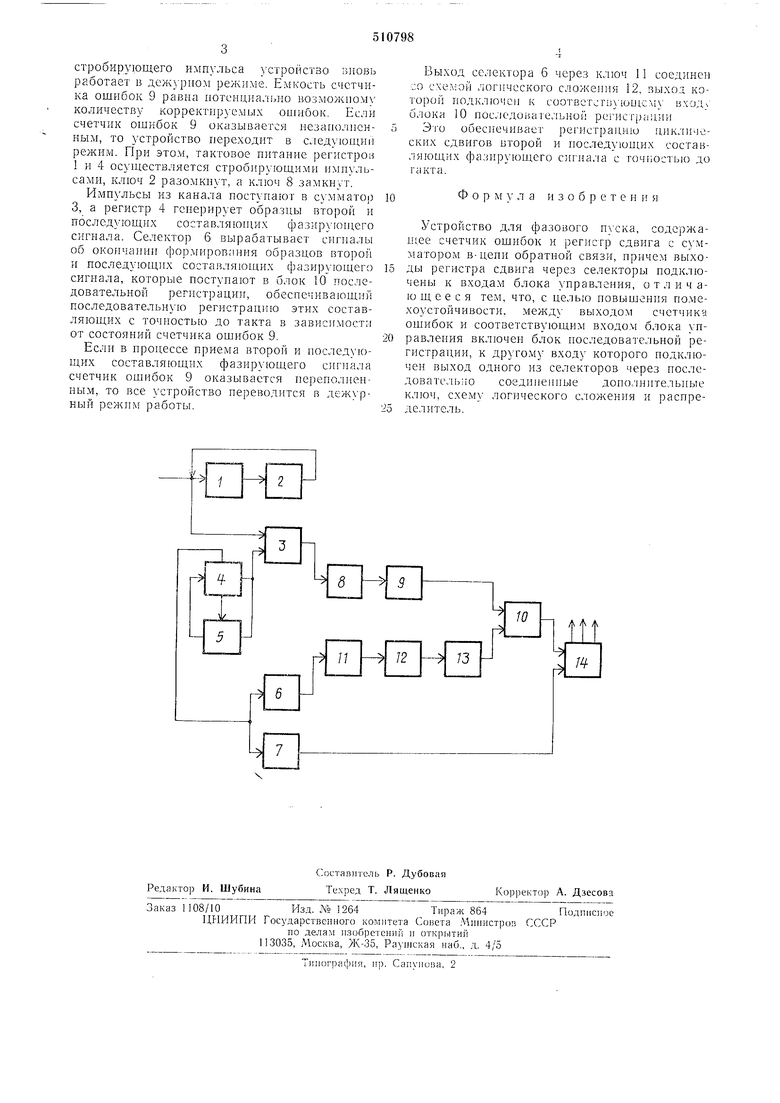

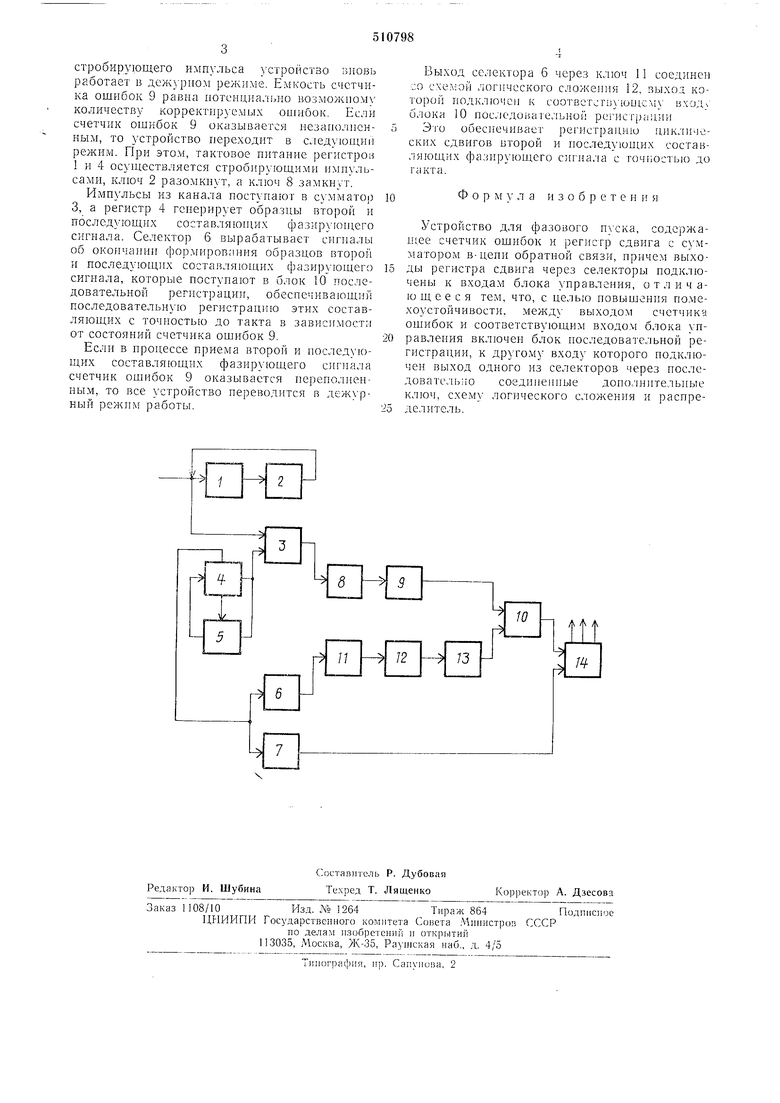

На чертеже приведена структурная схема предлагаемого устройства.

Устройство фазового пуска состоит из регистра памяти 1. выход которого через ключ 2 соединеп со своим входом и одним из входов сумматора 3, к другому входу которого подключен последовательный выход регистра 4 Сдвига с сумматором 5 в цепи обратной связи

и параллельно подключенными к нему селекторами 6 и 7. Выход сумматора 3 через последовательно соединенные ключ 8 и счетчик ошибок 9 подключен к одному из входов блока 10 последовательной регистрации, к другому входу которого подключен выход селектора 6 через носледовательно соедипенные дополнительные ключ 11, схему логического сложения 12 и распределитель 13. Выход блока 10 последовательной регистрации подключен к одному из входов блока 14 управления, к другому входу которого подключается выход селектора 7.

Устройство работает следующим образом.

В дежурном режиме импульсы из канала связи поступают в регистр памяти 1. Стробирующие импульсы вырабатываются блоком 14 управления, обеспечивающим временное согласование работы отдельных элементов схемы. в промежутках между двумя стробирующими импульсами производится сравнение анализируемой информации, хранящейся в данный момент в регистре памяти 1, с образцом первой составляющей фазирующего сигнала, генерируемым регистром 4 с сумматором 5 в цепи обратной связи. Клточи 2 и 8 при этом замкнуты. Сравнение обеспечивается сумматором 3. Если в результате нроизведениого сравнения, счетчик ошибок 9 оказывается переполненнылг, то с приходом следуюн его

строоирующего импульса устройство вновь работает в деж рг10.м режплае. Емкость счетчика ошибок 9 равна потенциально возможному количеству корректируемых оип-гбок. Если счетчик ошибок 9 оказывается незанолненкым, то устройство переходит в с.тедуюниш режим. При этом, тактовое нитанпе регистров и 4 осу1цествляется стробнруюш,ими нмнульсамп, ключ 2 разомкнут, а ключ 8 замкнут.

Импульсы из канала постунаюг в сумматор 3, а регистр 4 генерирует образцы второй и последующих составляющих фазируюн1.его сигнала. Селектор 6 вырабатывает снгналы об окончании фор.мировллия образцов второй и последуюших составляющих фазирующего сигнала, которые поступают в блок 10 носледовательной регнстрации, обеснечивающнй последовательную регистрацию этих составляющих с точностью до такта в зависимости от состояний счетчика ошибок 9.

Если в процессе приема второй и последуюищх составляюших фазируюшего сигнала счетчик ошибок 9 оказывается нереполненным, то все устройство нереводнтся в дежурный режим работы.

Выход селектора 6 через ключ 11 соединен со схемой логического сложения 12, выход которой подключен к СООТВеТСПЛЮШСМу В.ХОДн

блока 10 последо;и1тельной pcj-HCTpaiuni Это обеснечивает регнстрацню циклических сдвигов второй и последуюищх составляюших фазируюндего сигнала с точностью до гакта.

Формула изобретен и я

Устройство для фазового , содержащее счетчик ошибок и регистр сдвига с сумматором в-цени обратной связи, нричем выходы регистра сдвига через селекторы подключены к входам блока управления, отличающееся тем, что, с целью повышения помехоустойчивости, между выходом счетчика ошибок и соответствующим входом блока управлеиия включеп блок последовательной регистрации, к друго.му входу которого подключен выход одного из селекторов через последователь ;io соединенные донолннтельиые ключ, схему логического сложения и раснределитель.

г

Ш

г

Авторы

Даты

1976-04-15—Публикация

1973-07-16—Подача