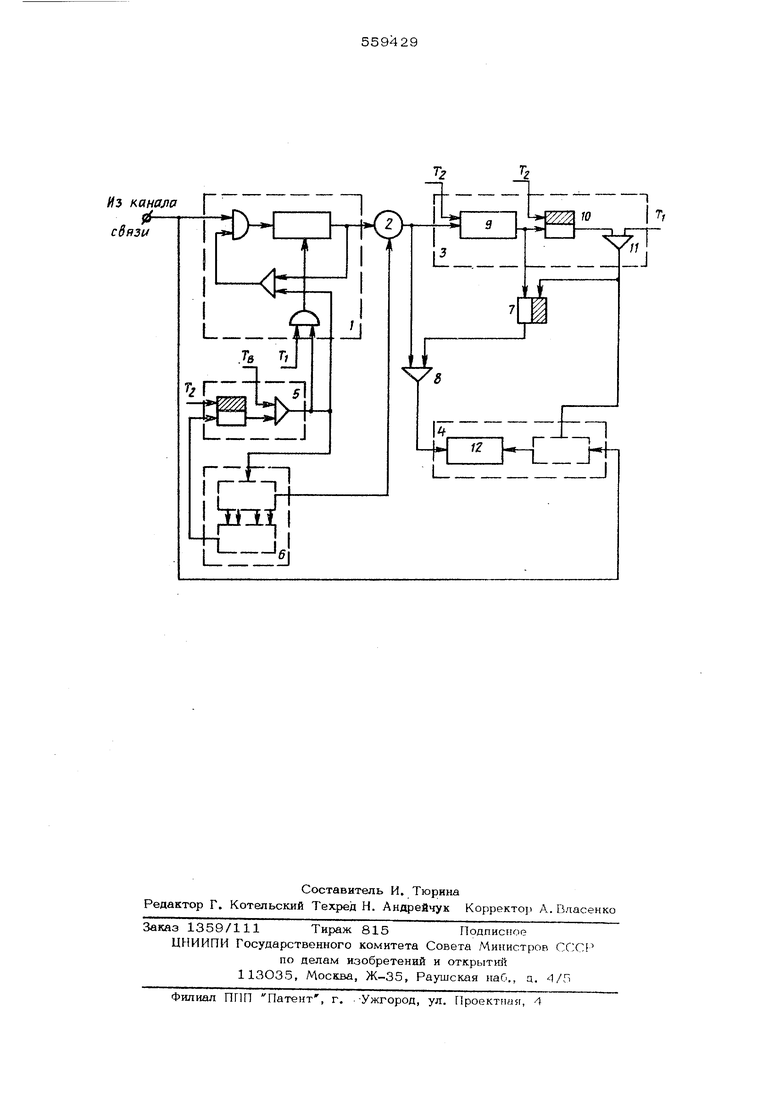

пояключев к соответствующему вхояу формирователя 5.

Соответствующие выходы детектора 3 подключены к входу вычитания приемника тестовой информации 4 через после до вательно соепиненные триггер 7 и элемент И 8. К друпому входу элемента И 8 подключен выход сумматора 2 по модулю два.

Устройство работает следующим образом

Посимвольно принятая из канала связи последовательность, хранящаяся в блоке памяти 1, сравнивается в сумматоре 2 по модулю два с последовательностью, выработаннсА генератором 6. Управляющими щш блока памяти 1 и генератора 6 яьляются сигналы формирователя 5, запускаемого тактовым импульсом малой скорости Т . При появлении на выходе регистра сдвига 9 детектора ошибок 3 единицы, записанной в него тактовым импульсом T.J, , аа время формирования пачки сдвига &-Ь, меньшее промежутка между тактовыми импульсами Т и T.J , триггер 10 детектора ошибок устанавливается в состояние, при котрром запрещается прохождение импульса Т через элемент И 11 детектора ошибок для фазового пуска в приемник тестовой информации 4.

ЕСЛИ число совпадений в принятой из канала связи и выработанной генератором 6 последовательностях меньше f , то единица на выходе регистра сдвига 9 в данном такте не появится. Тактовый импульс Т , прохождение которого через элемент И 11 обусловлено установкой триггера 10 в единичное состояние при помоши тактового имульса Tj, , поступит для фазового пуска в приемник тестовой информации. 4, а также установит триггер 7 в единичное состояние

В следующем такте с запуском формирователя 5 сигналы несовпадения с сумматора 2 по модулю два через элемент И 8 станут поступать на вход вычитания счетчика ошибок 12 приемника тестовой информации 4 до тех пор пока не появится единица на выходе регистра сдвига 9. Таким образом, на вход вычитания счетчика ошибок 12 поступит ( - f ) импульсов, т.е. устройство фактически формирует разность между максимально попустимым числом искажений фазирующей последовательности в

канале связи и числом искажений, наблюдаемым в действительности. Поэтому счетчик ошибок 12 предварительно должен быть установлен в состояние Р . Если же фазирующан последовательность передается 1 раз, то счетчик ошибок 12 должен быть предварительно установлен в состояние Vt. По окончании фазирования приемник начинает анализ тестовой информации с выдачей импульсов ошибок на вход суммирования счетчика ошибок 12.

Тезщико-экономическая эффективность изобретения обусловлена возможностью повысить точность подсчета ошибок для оценки качества работы канала связи при передачи по нему тест-сигнала не только за время передачи тест -сигнала, но и за время вхождения приемника в цикловой синхронизм. При большом уровне помех в канале связи и при длительном времени вхождения пр.иемника в синхронизм получение дополнительной информации о количестве ошибок за время фазирования позволяет оценить качество работы канала за весь

сеанс связи.

Формула изобретения

Устройство для подсчета ошибок в фазирующей по циклу последовательности, содержащее последовательно соединенные блок памяти, сумматор по модулю два, детектор ошибок и приемник тестовой информации,

соединенный с первым входом блока памяти, к другим входам которого подключены выходы формирователя пачки высокочастот ных импульсов, соединенного также с вторым входом сумматора по модулю два через генаратор сигналов фазового пуска,

другой выход которого подключен к соответ-ствуюшему входу формирователя пачки высокочастотных импульсов, отличающееся тем, что, с целью повышения

точности подсчета ошибок, в него введены триггер и элемент И, а соответствующие ВЫХОДЫ детектора ошибок подключены к входу вычитания приемника тестовой информации через последовательно соединенные

триггер и элемент И, к другому входу которого подключен выход сумматора по модулю два.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство избирательного вызова и передачи кодограмм | 1983 |

|

SU1136326A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Система формирования и приема телевизионного сигнала при передаче изображения | 1988 |

|

SU1555909A2 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ПО ЦИКЛАМ | 1970 |

|

SU275106A1 |

Авторы

Даты

1977-05-25—Публикация

1975-07-07—Подача