Изобретение относится к устройствам для радиосвязи.

Известны устройства для приема сигнала фазового пуска, содержащие регистр памяти принимаемых элементарных посылок, генератор сигнала фазового пуска, формирующий на повыщенпой частоте сигнал фазового пуска за время одной элементарной посылки, перемножитель и детектор ощибок. Такие устройства сложны н выполняются на логических элементах, работающих на новышенной частоте.

Целью изобретения является упрощение устройства нрпема сигнала фазового пуска при уменьшении частоты высокочастотных управляющих импульсов без увеличения числа непринятых п ложных сигналов фазового пуска.

Для этого в предлагаемом устройстве фазирования параллельные выходы регистра сдвига генератора сигнала фазового пуска через селектор конца первой части сигнала фазового пуска подсоединены ко входу блокировкн формирователя пачки высокочастотных управляющих импульсов. При этом вход низкочастотных управляющих импульсов устройства подключен через коммутатор, связанный по цепи управления с парафазным выходом детектора ощибок, ко входу синхронизации считывания и входу установки в исходное состояние генератора сигнала фазового пуска. Благодаря этому уменьщается объем памяти блока памятн принимаемых высокочастотных управляющих импульсов до величины, определяемой допустимой величиной вероятности ложного фазирования. Отрезок принимаемой последовательности п„ не искажается, и на его основе генерируются последующие символы последовательности. Обычно принимают п„ 1§2 (« + ), где /I - длина носледовательности. В известном устройстве допускается искажение некоторого числа символов из jV, т. е. п„ символов ирииимаются без исправления ощибок, а последующие N - с исправлением. В этом случае требуемое значение вероятности правпльиого выделения фазы носледовательностп обеспечивается многократным заполнением регистра генератора, для чего необходимо использовать последовательности больщой длииы, что в системах передачи данных нежелательно.

Ири искаженни одного из символов и правильном приеме всех последующих символов выделение фазы последовательности не производится, причем .

Правильность выделения фазы может быть

определена для любого отрезка длинной последовательности символов при условии, что без ощпбок принимаются не только п„, но и все Л последующих символов. При таком варианте последовательного приема для обеспеМО использовать длинные последовательности.

Предлагаемое устройство осуществляет последовательный прием при («+), причем ошибки исправляются независимо от их расположения по длине последовательности.

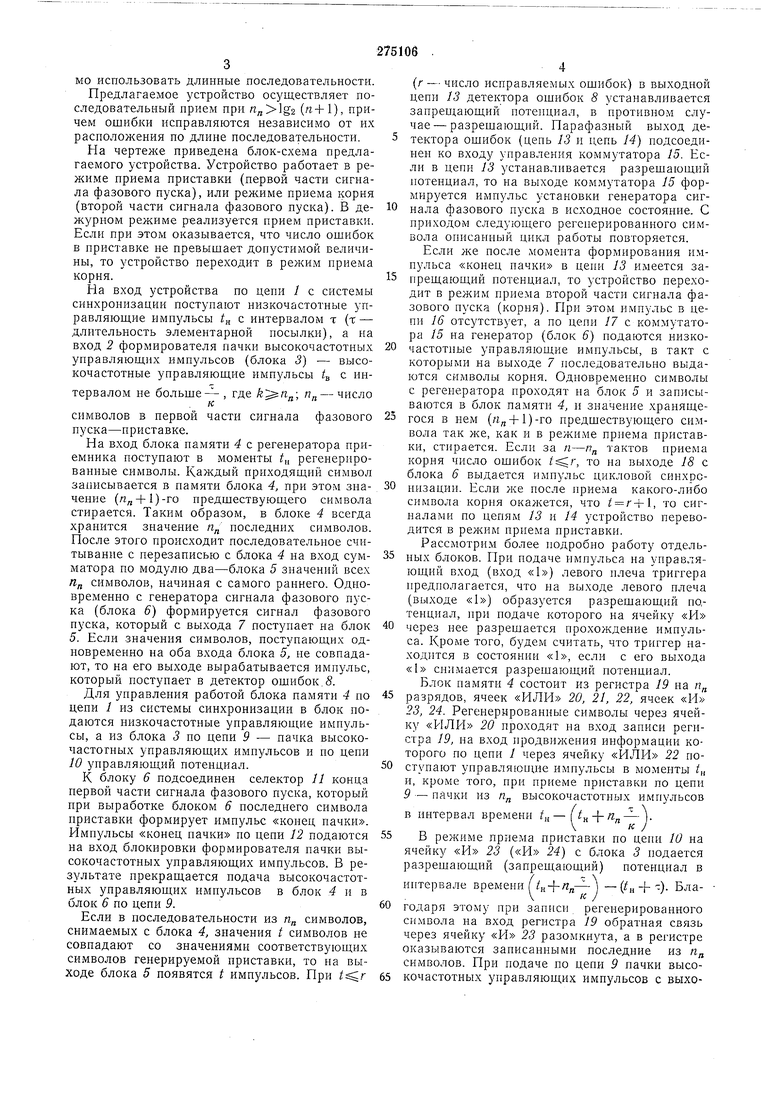

На чертел е приведена блок-схема предлагаемого устройства. Устройство работает в режи.ме приема приставки (первой части сигнала фазового пуска), или режиме приема корня (второй части сигнала фазового пуска). В дежурном режиме реализуется прием приставки. Если при этом оказывается, что число ошибок в приставке не превышает допустимой величины, то устройство переходит в режим приема корня.

На вход устройства по цепи 1 с системы синхронизации поступают низкочастотные управляюш.ие импульсы „ с интервалом т (t - длительность элементарной посылки), а на вход 2 формирователя пачки высокочастотных управляюш;их импульсов (блока 3) - высокочастотные управляюш,ие импульсы /в с интервалом не больше-, где ге„; п„ - число

символов в первой части сигнала фазового пуска-приставке.

На вход блока памяти 4 с регенератора приемника поступают в моменты t регенерироваииые символы. Каждый приходящий символ записывается в иамяти блока 4, при этом зиачение (я„Н-1)-го предшествующего символа стирается. Таким образом, в блоке 4 всегда храиится значение п„ последних символов. Носле этого происходит последовательиое считывание с перезаписью с блока 4 на вход сумматора по модулю два-блока 5 значений всех /г„ символов, начиная с самого раннего. Одновременно с генератора сигнала фазового пуска (блока 6) формируется сигнал фазового пуска, который с выхода 7 поступает на блок 5. Если значения символов, поступающих одновременно на оба входа блока 5, не совпадают, то на его выходе вырабатывается импульс, который поступает в детектор ошибок,S.

Для управления работой блока памяти 4 по цепи / из системы синхронизации в блок подаются низкочастотные уиравляющие имиульсы, а из блока ,3 по цепи 9 - пачка высокочастотных управляющих импульсов и ио цепи 10 уиравляющий потеициал.

К блоку 6 подсоединен селектор 11 конца первой части сигнала фазового пуска, который ири выработке блоком 6 носледнего символа нрнставки формирует импульс «коиец пачки. Импульсы «конец начки по цепи 12 подаются на вход блокировки формирователя пачки высокочастотных управляющих импульсов. В результате прекращается подача высокочастотных управляющих имиульсов в блок 4 и в блок 6 по цепи 9.

Если в последовательности из и„ символов, снимаемых с блока 4, значения t символов не совпадают со значениями соответствующих символов генерируемой приставки, то иа выходе блока 5 появятся t импульсов. Нри

(/- - число исправляемых ощибок) в выходной цепи 13 детектора ощибок 8 устанавливается запрещающий поте1щиал, в противном случае- разрещающий. Парафазный выход детектора ошибок (цепь 13 и цепь 14) подсоединен ко входу управления коммутатора 15. Если в цепи 13 устанавливается разрешающий потенциал, то на выходе коммутатора 15 формируется импульс установки генератора сигнала фазового пуска в исходное состоянне. С приходом следующего регенерированного символа описаииый цикл работы повторяется.

Если же иосле момента формироваиия импульса «конец пачки в цепи 13 имеется запрещающий потенциал, то устройство переходит в режим приема второй части сигнала фазового иуска (корня). При этом импульс в цепи 16 отсутствует, а по цепи 17 с коммутатора 15 на генератор (блок 6} подаются низкочастотные управляющие импульсы, в такт с которыми на выходе 7 последовательио выдаются символы корня. Одновременно символы с регенератора проходят на блок 5 и записываются в блок памяти 4, и значение хранящегося в нем (л„ + 1)-го предшествующего символа так же, как и в режиме приема приставки, стирается. Если за п-/7„ тактов приема корня число ошибок , то иа выходе 18 с блока 6 выдается имнульс цикловой синхронизации. Если же после приема какого-либо символа корня окажется, что t r+, то сигналами по цепям 13 и 14 устройство переводится в режим приема ириставки.

Рассмотрим более подробио работу отдель5 иых блоков. При подаче импульса иа управляющий вход (вход «1) левого илеча триггера предполагается, что на выходе левого плеча (выходе «1) образуется разрещающий по,теициал, ири иодаче которого на ячейку «И через нее разрешается прохождение импульса. Кроме того, будем считать, что триггер иаходится в состоянии «1, если с его выхода «1 сии.мается разрещающий потенциал.

Блок иамяти 4 состоит из регистра 19 на п„ разрядов, ячеек «ПЛП 20, 21, 22, ячеек «И 23, 24. Регенерированные символы через ячейку «ИЛИ 20 проходят на вход записи регистра 19, на в.ход продвижения информации которого ио цепи 1 через ячейку «ИЛИ 22 иоступают управляюпще импульсы в моменты 1„ и, кроме того, при приеме приставки по цепи 9 - пачки из л„ высокочастотиых импульсов

в интервал времени /„-(н +

В приема приставки по цепи 10 иа ячейку «И 23 («И 24} с блока 3 подается разрещающий (запрещающий) потенциал в

н + «„-) -(Л, + )- Блаинтервале времени

годаря этому при записи регеиерироваиного символа на вход регистра 19 обратная связь через ячейку «И 23 разомкнута, а в регистре оказываются записанными последиие из я„ символов. При подаче по цепн 9 пачки высокочастотных управляющих импульсов с выхода ячейки «ИЛИ 21 снимаются иа сумматор по модулю два значения последних из л„ символов.

В режиме приема корня на ячейку «И 23 по цепи 10 все время поступает запрещающий потенциал, а через ячейку «Р1ЛИ 22 на регистр 19 - только низкочастотные управляющие импульсы. Поэтому сигналы на выходе ячейки «И 23 отсутствуют. В то же время на ячейку «И 24 с блока 3 по цепи 25 поступает разрешающий потенциал, и поэтому регенерированные символы проходят через «И 24, «ИЛИ 21 на вход блока 5.

Генератор сигнала фазового пуска (блок 6) включает в себя регистр 26 на 5 lg2(rt+l) разрядов с сумматором по модулю два в цепи обратной связи, ячейку «ИЛИ 27, селекгор 28 и ячейку «И 29. В режиме приема приставки на вход установки в исходное состояние регистра 26 ироходят низкочастотные управляющие импульсы в моменты /„ по цепи 16, на вход продвижения информации регнстра - пачка из п„ высокочастотных управляющих импульсов по цепи 9 через ячейки «ИЛИ 27. Наличие сумматора по модулю два в цепи обратной связи регистра обеспечивает формирование на выходе 7 отрезка рекуррентной носледовательностн, соответствующего приставке сигнала фазового иуска. Иосле формирования последнего снмвола приставки срабатывает селектор 11, представляющи собой дещифратор на S выходов, подсоединенных к вр ходам ячеек регистра 26.

В режиме приема корня импульс в цепи 16 отсутствует, а но цепи 17 поступают низкочастотные уиравляющне импульсы через ячейку «ИЛИ 27 иа вход продвижения информации регистра 26. При этом на выходе 7 формируются символы корня. После генерирования последнего символа корня срабатывает селектор 28, представляющий собой дешифратор иа S входов. Если после суммирования последнего символа корня с регенерированным символом окажется, что число ошибок , то ио цепи 14 с детектора ошибок 8 на иотеициальный вход ячейки «И 29 иостуиает разрешающий иотенциал, а имиульс с селектора 28 ироходит через ячейку «PI 29 на выход устройства.

Детектор ошибок 8 состоит из счетчика 30 с коэффициентом счета г+, ячейки «И .3/ и триггера 32. Имиульсы с выхода сумматора по модулю два через ячейку «И 31 поступают на вход счетчика 30. Если во время приема приставки число импульсов с блока 5 окажется равным г+1, то на выходе счетчика 30 появится импульс, который проходит иа вход «1 триггера 32. Поэтому с выхода «О триггера 32 на ячейку «И 31 поступит запрещающий потенциал. Низкочастотный управляющий имиульс в момент t, проходит иа вход «О триггера 32. Таким образом, к моменту начала следующего цикла приема приставки на

ячейку «И 31 с триггера 32 поступает разрешающпй потенцпал, а счетчик 30 находится в нулевом состоянии.

Аналогично работает детектор ошибок ири приеме корня. К. выходам «1 и «О триггера 32 подсоединены выходные цепи 13 и 14 дегектора ошибок.

Формирователь пачки высокочастотных управляющих имиульсов (блок 3) содержит

триггер 33 и яче1и у «И 34, коммутатор 15 содержит ячейки «И 35 и 36.

Если за время очередного цикла приема приставки число ощибок , то в момент /„ импульс, проходящий через цепь / и ячейку

«И 35, устаиавливает триггер 33 в состояиие «О и выдается по цеии 16 в блок 6. К выходам «I I «О триггера 33 подсоедпнены цепи 25 и 10. Кроме того, вы.ход «О триггера 33 подключен к ячейке «И 34, через которую высокочастотпые управляющее имиульсы ироходят по цепи 9 в блоки 6 и 4. С иодачей ио 12 иа вход «1 триггера 33 импульса «конец иачкп прохождение высокочастотных уиравляюи;,их имп льсов через ячейку «И 34

прекращается.

В режиме приема корня но цеии 14 иостуиает заиреп1,ающий потепциал, поэтому триггер 33 остается в состояпии «1 и на ячейку «И 34 подается запрещающий потенциал. По

цепи 14 на ячейку «И 36 ироходит разрещаюmini потепцпал п низкочастотные управляющие импульсы подаются через ячейку «И 36 по цепи 17 на блок 6.

35

Предмет изобретения

Устройство фазирования ио циклам с исиравлепием ощибок при рекуррентном сигнале фазового иуска, содержащее блок намятп

ирииимаемых символов, генератор сигнала фазового иуска с регистром сдвига, сумматор ио модулю два ирииимаемых и генерируемых символов, связанный с детектором ошибок, формирователь пачки высокочастотных управляющих имиульсов, отлича1О1цеес.н тем, что, с целью уменьшения памяти блока памятп принпмаемых символов до величины, оиределяемой допустимой величииой вероятности ложного фазирования, нрн одиоврел енном

уменьшении частоты высокочастотиых унравляющих импульсов без ухудшения помехоустойчивосги фазирования, параллельные выходы регистра сдвига генератора сигнала фазового пуска подсоединены через селектор конца

первой части сигнала фазового иуска на вход блокировки формирователя пачки высокочастотных управляющих имиульсов, а вход иизкочастотных уиравляющих импульсов устройства подключеи через коммутатор, связаиный

по цепи уиравлення с парафазным выходом детектора ошибок, ко входу синхронизации считывания и входу установки в исходное состояние генератора снгнала фазового иуска.

Даты

1970-01-01—Публикация