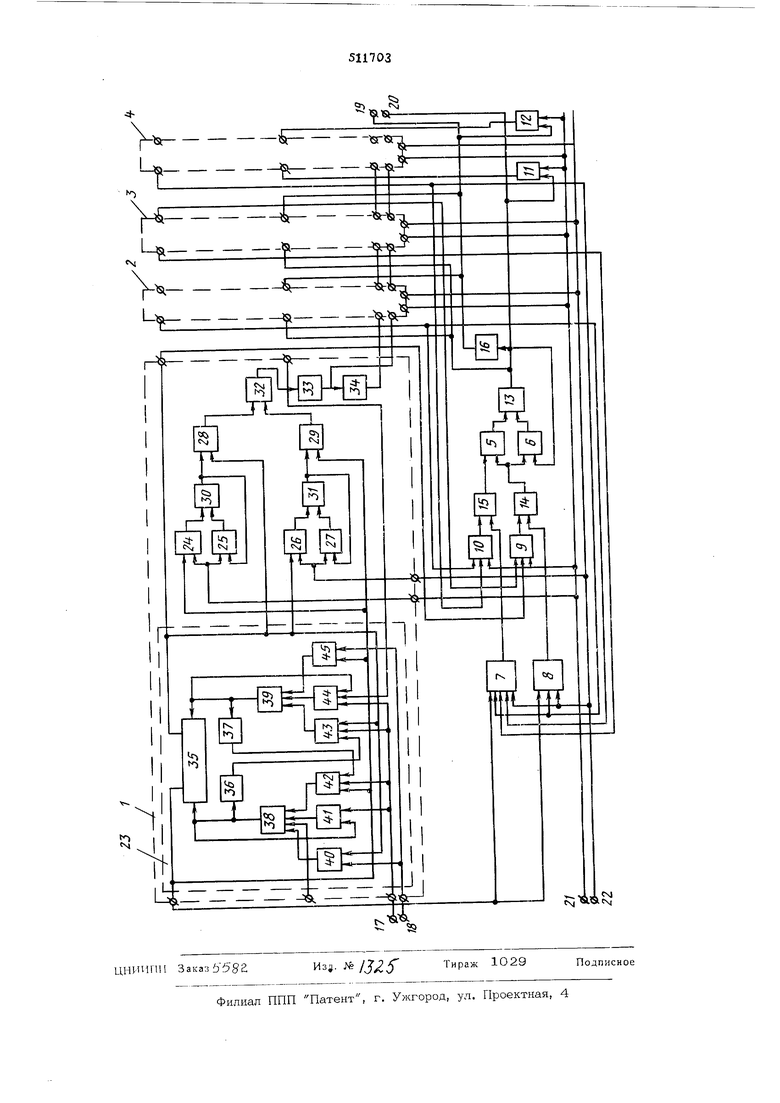

Изобретение относится к автоматике и вычислительной технике. Известны потенциальные счетчики, со- держащие четырехразрядный триггерный двоичный счетчик, шины сложения и вычитания, схемы И, схемы ИЛИ. Целью изобретения является уменьшение вероятности ложного срабатывания триггеров в процессе двоично-десятичного счета. Для этого выход первой схемы ИЛИ, соединен со входами сброса второго и третьего триггеров двоичного счетчика, с выходом потенциального счетчика, с первыми входами первой и второй схемы И, Второй вход первой схемы И соединен с шиной сложения, а выход - со входом сброса четвертого триггера двоичного счетчика. Второй вход второй схемы И соединен с первым входом третьей схемы И и через вторую схему ИЛИ подключен к выходам двух схем И, входы одной из которых соединены с шиной сложения и с нулевыми выходами первого и третьего триггеров двоичного счетчика, а входы другой - с ши ной вычитания и с единичными выходами первого и четвертого триггеров двоичного счетчика. Второй вход третьей схемы И через третью схему ИЛИ подключен к выходам двух схем И, входы одной из которых соединены с шиной сложения и единичными выходами второго и четвертого триггеров двоичного счетчика, а входы другой с шиной вычитания и с единичными выходами всех триггеров двоичного счетчика. Выходы второй и третьей схем И соединены со входами первой схемы ИЛИ. На чертеже приведена функциональная схема потенциального счетчика. Потенциальный счетчик содержит четырехразрядный двоичный счетчик с разрядами 1-4, схемы И 5-12, схемы ИЛИ 13-15, схему НЕ 16, входные клеммы 17 и 18, выходные клеммы 19 и 20, шины 21 сложения и вычитания 22. В состав каждого разряда входит двоичная пересчетная схема 23, схемы И 24- 29, схемы ИЛИ 30-32 и схемы НЕ 33 и 34. Схема 23 каждого разряда счетчика содержит триггер 35 схемы НЕ 36, 37, схемы ИЛИ 38, 39 и схемы И 40-45,

счетчкж работает сле-йую щим образам 8

Входные подаются ни вхоляьш клеммы 17 и 18,, При gTOK-s на клемму 17 cHTHajSbs е йнве| сного выхода зхожНё ного фйггервв а ва sf. 18 « о Ердалог входного tpijrrspa, В процесс© подачй 8:й;одкЬй: сйгнал&б осуу-, ществляется жк. Г1ересчет с йомощью четьи I рехразршэдаого очетчикаа В каяшом разрйй4 № двоичная пересчетавя схема 33 ос гщвствярЦ-. вт пересчет подаваемой вводной не ;ледова|-. твя&йостй ко модущо два, а Скемь 24 29, схемы ИЛИ и сжмм НЕ | 33 н 34 предназначены -для осужествленнй Ш реверсивного режима ра6о1Ъ счетчвка и передачи cHTtianoB в слеД5 юпгай разряд

В реж1Ше сложения на выходе скемы , MI11F ЗО имеет Meci-o ттэвдательный ур(. вень напряжения, который йойаетсй на одш 2С шз входов схемы Mf 28, на щэугой вход ;которой поступают с ггнапы с,нулевого вы хода Tpicrrepa 35 разряда it которые про-, ходят на BbiJct)fl схек4Ь ИЛИ 32 я йалее йа йкод схемы 33; выход которой 21 связан о входной клвымой 18 разряда 2 и со входом схемы 34„ ; С вьжояа НЕ 34 сигвапь ripc кояят на входную клемму 17 разрйда 2 . ;.е |©тчяка. В, рехчиме сложения csjrHaj-tbs на , ВЫХОД етеемы Й 29 не проходят, так кагг ка выходе схемь 31 имеет место .йулевой уровень напряжения ; В. режйМе вычйтанкя ка вьгеоде сжемь5 |. 31 поддерживается вьюоккй ypOBeHbj iKOTOpHE нодаетсй на вход схемы И Я9о При этом на выход схемы 29 прохо« ;Дйт снгкаль5 с единичког1э выхода триггера ,35 разряда ,1, Очевидно, что в Данном ре 1Жйм« Сигналы на выЛсод схемы 28 не проходят,

- При поступлении в процессе нересчета йа вход схемы десятого 1мпульса потвн |айальные сигналы с единзр-шыж выход в тр . 35 разрядов 2 и 4 открывают схему (И iO и сигнал с ее выхода подается ч&-е :рез схему 15 на один из входов схемы И 5 на другой вкод которой череФ схему ИЛИ 14 подаетсярйзрешающкй с нап с выхода схемы И 9 На-входы схемы И 9 при этом подаются вью окне по™ тендиальные- уровни с нулевых выходов трио |гвров,35 разрядов 1 и 3, которые после поступления десятого импульса находятся i в нулевом состоянии.

- При подаче высоких уровней сш-налов на. входы схемы о на выходе- схемы 13 воспроизводито сигнал переноса, кото« рый непосредственно и через схему 16

Ьролоййт на Быходазые клеммы 19 и 20 Дсн

« ®ахшльного счеЯшга,

Ош временяо С15гнал с выхода схемы - ИЛИ 13 подается на входы схем /ИЛИ (38 ш с вьпг,ода схемы НЕ 16 - иа вяоды Ьоотва-гетвующшс схем И 44 пересчетных

Ьхем 23 но модулю два разрядов 2 3 и

через саемы W 11 я 12, с0язанны© с.щйной 21 опоженнЯв на В21од разряда 4, При ; 1

этом tpiirrepbi 35 разрядов 2 и 4 5 танаёй| : Лйваются в нупевое cocTOsiiHet а триггер

3S разр5вда 3 лоддеригта тся в нулевом -j : состоянгш прк переводе тршгтерй 3S разр ,да 2 из l S .I

; . rioCdia установки траггеров 35 в нулевЕ е состояние сигнал на выходе сжемы ЙЛИ i 13 продолжает действовать, Tat как кмее MGCiO обратная свазь с вьсаода сяемы И/1И

13 на вход схемы 6„ При подаче дующего за десятым имиульсо-л. входного i сигнала начинает осуществпятьсэ новьгй .,

пересчета. При этом меняется уровень С1ггнала с выхода схемы ИЛИ 13 н с Bbi

зсода схемы НЕ . 16. вследствие перехода | : Tptirrepa 35 разряда 1 иэ нулевого в едти яичное состояние,

Далее счетчшс тцэодолжает считать тл пу/шсы в ттрдалом натгравлении до момента

перевода его из режима сложения в режшуГ;

вычитания. Это осуществляется снятием j ; йотенциальнШО уровня с шины 21 сложен|ф| и подачей cssTHana на шину 22 вычитаний , Г

начиная с этого MOMejjTa осущес-шлаетсзй , -i считывание инфор -гацйи,, заП85санной в ре жиме сложения

По достижению нулевого состояния при подаче следующего входного и шyльca все : триггеры 35 счетчика переводятся в состол Д ние -i, В этом сщ«1ае высокие потенциаЛь ные уровни с. ещШичных выходов тр.иггйй)в 35 разрядов открывают схему 7 и сигнап с ее выхода подается через схе- му PiЛИ 25 на один из входов схемы РГ б, на f yroft вход которой через cx&f . му ИЛИ 14 также подается разрешающий ; сигнад.,с .вьБСОДа схемы И З, При этим . i на входы схемы И 8 подаются высокие ; потенциальные уровни с единичных выходов

триггеров 35 разрядов i и 4. При подаче высоких уровней сигналов на входы схемы

: -fpi 5 на вьпсоде схемы ИЛИ 13 воспро-изводится сигнал займа, который непосред-. ственко и через схему НЕ 16 проходит на выходные клеммы 319s 20 и через них

«. в след токций двоично-десятичный разряд,

Одновременно сш-нал с выхода схемы ЙЛИ 13 подается на входы схем ИЛИ

., 38 и схем И 44 пересчетных схем 23

по меяупю два разряда 2 и 3. При этом

триггеры 35 разрядов 2 и 3 устанавйив готся в нулевое состояние, а триггеры 35 разрядов 1 и 4 поддер} /иввются в едиянчвом состоянии при переводе трагге$ вв 35 разрядов 2 и 3 из в О.

. Сигнал на входе схемы ИЛИ 13 должает действовать nocrte установка трмгЦ

, Это осуществляется &следствя© того, что триггеры Зб разрядов 1 4 находятся в единичном состоянии, а также,: за счет наличия обратной связи с выхода

cjteMH ИЛИ 13 на вход схемы И 6 Пря йодаче следующего входного сигнала начинает осуществляться новый цикл п&реёчета. При этом меняется уровень сигшпа с 1Хбдв схемы ИЛИ 13 и с да схемы НЕ 1в.вследствие перехода триггера 35 разряда 1 йз единичного в

нулевое состояние.

Ф о р мула изтб ре тения

Потенциальный счетчик, содержащий четырехразрядный триггерный двоичный чик, щявы сложения и вычитаний; ,4Ь

ч I, И, cxetebJ , о т л и ч а ю а ю щ и и с h тем, что, с делью умень- шения веротности ложного срабатывания

триггеров в процессе двоично-десятнчного счета, первой схемы.ИДИ соединен со входами сброса второго и третьего триггеров двоичного счетчика, с выходом потенциального счетчика, с первык и входа ми первой я второй схемы И , второй вход первой схемы И соединен с шиной сложения, а выход со входом сброса 4eTiвертого триггера двоичного счетчика, второй вход схемы И соединен с первым входом третьей схемы И иjЧерез,вторую схему ИЛИ подключен к выходам Двух схем И , входы одной из которых соеди1ШНЫ с шиной сложения и с нулевыми выходами первого и третьего триггеров двоичного счетчика, а входы другой « с шиной вь читания и с единичными вьссодами перво го и четвертого триггеров двоичного счет чика, второй вход третьей схемы через третью схему ИЛИ подключен к вы И, входы из кото

ходам двух схем

рых соединены с игиной| сложения и с еди-jничными выходами второго и четвертого i. , j триггеров двоичного счетчика, а входы jtx)e- с Щиной вычитания и с единичными въыходами всех триггеров двоичного счетчика,} выходь второй и третьей схемы И соединен со входами первой схемы ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь цифрового кода в частоту следования импульсов | 1976 |

|

SU738158A1 |

| Реверсивный двоично-десятичный счетчик | 1974 |

|

SU525251A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| ДВОИЧНЫЙ РЕВЕРСИВНЫЙ СЧЕТЧИК | 1971 |

|

SU311405A1 |

| РЕВЕРСИВНАЯ ДВОИЧНО-ДЕСЯТИЧНАЯ ДЕКАДА | 1972 |

|

SU414745A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для дифференцирова-Ния чАСТОТы СлЕдОВАНия иМпульСОВ | 1978 |

|

SU798881A1 |

| Распределитель импульсов для управления шестифазным шаговым двигателем | 1990 |

|

SU1709490A1 |

| Реверсивный двоично-десятичный счетчик | 1973 |

|

SU455493A1 |

Авторы

Даты

1976-04-25—Публикация

1972-10-26—Подача