1

Иэобрете ше относится к автоматике и вычислительной технике.

Известны логические элементы, содержащие иходноЙ многоэмиттерный транзистор, коллектор которого соединен со входом сложного инвертора, вьшолненного на транзисторах.

Такие логические элементы являются аотенщяальнымн и не могут вьгаолнять импульсна-потенциальных . логических фунций, что ВО МНОГИХ случаях необходимо.

Цель изобретения - обеспечение им.пульсно-потенциального функционирования логическогю элемента, в частности вы лолнение логической функции

Т)

(Mi Иг

М,

Т.

Поставленная цель достигнута благодаря тому, что один или несколько эммиттеров ВХОДНОГО многоэммиттерного тран:зистора подключены к общей шине через по(Слецовательно соединенные резистор и излучающий диод дополнительно введенного оптрона, фотоприемник которого включен

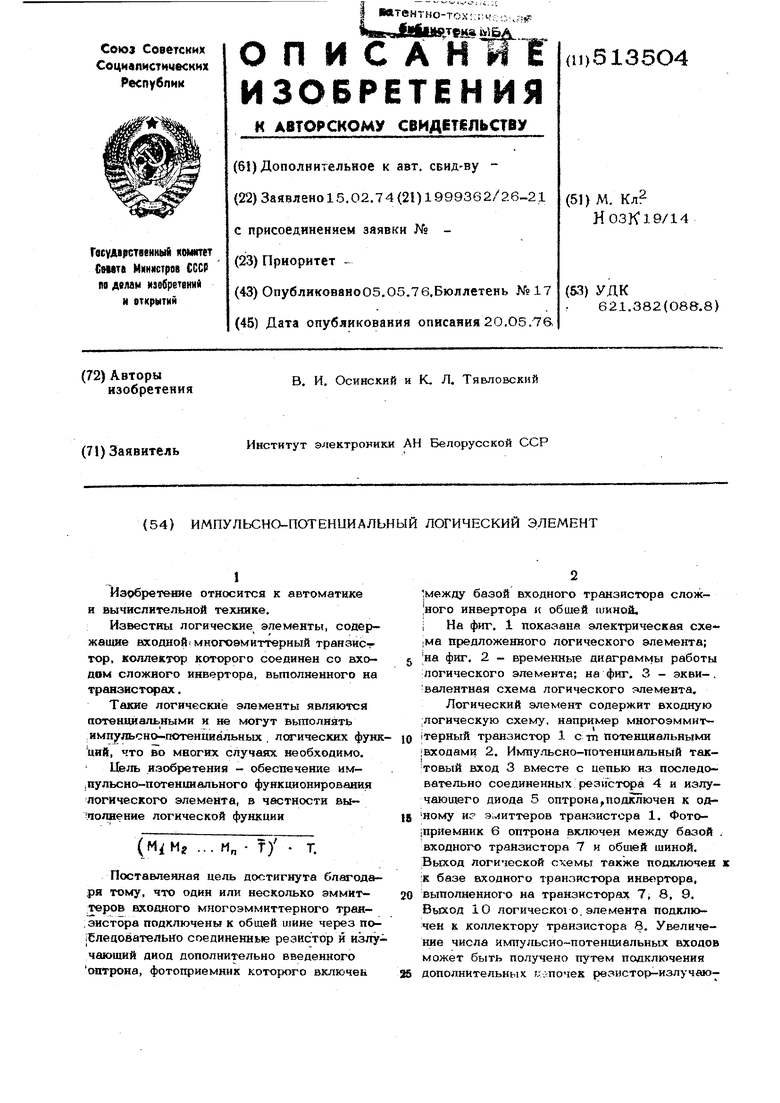

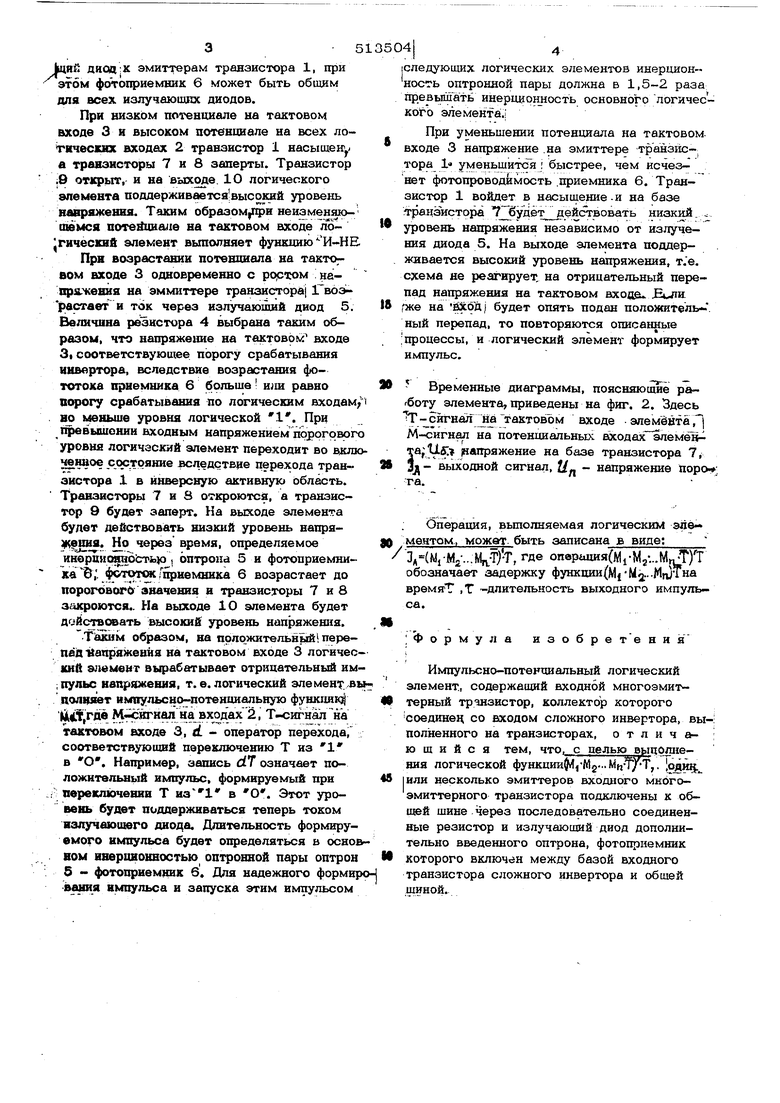

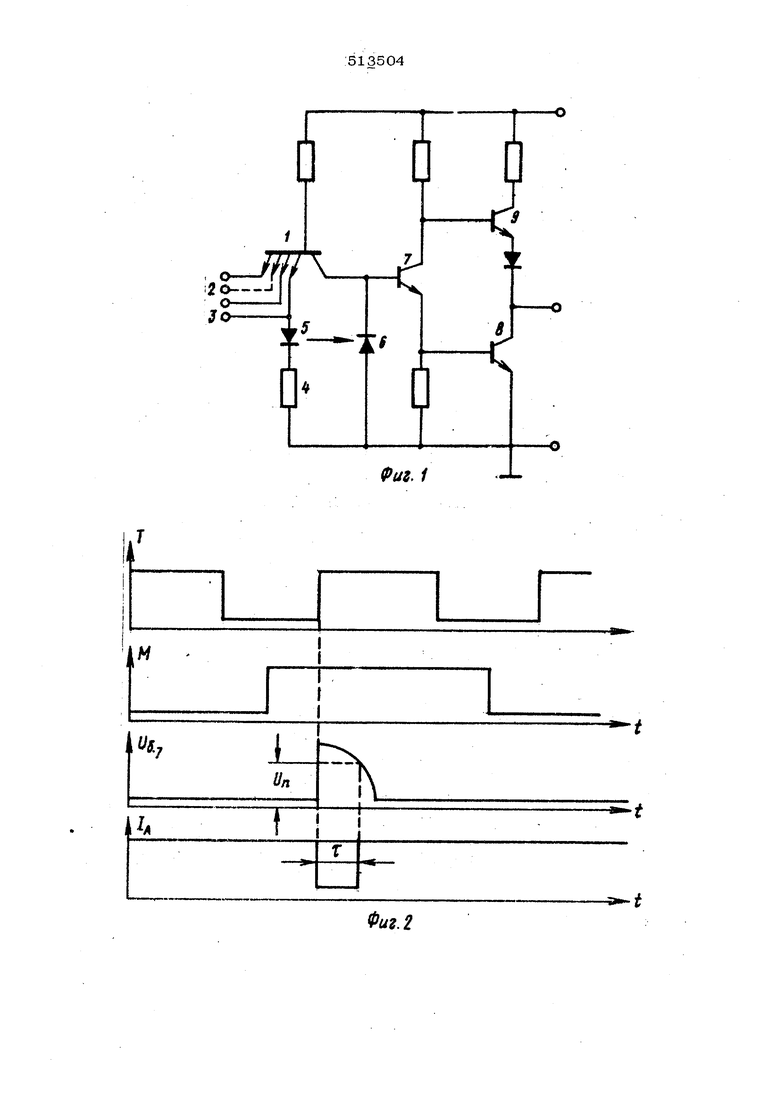

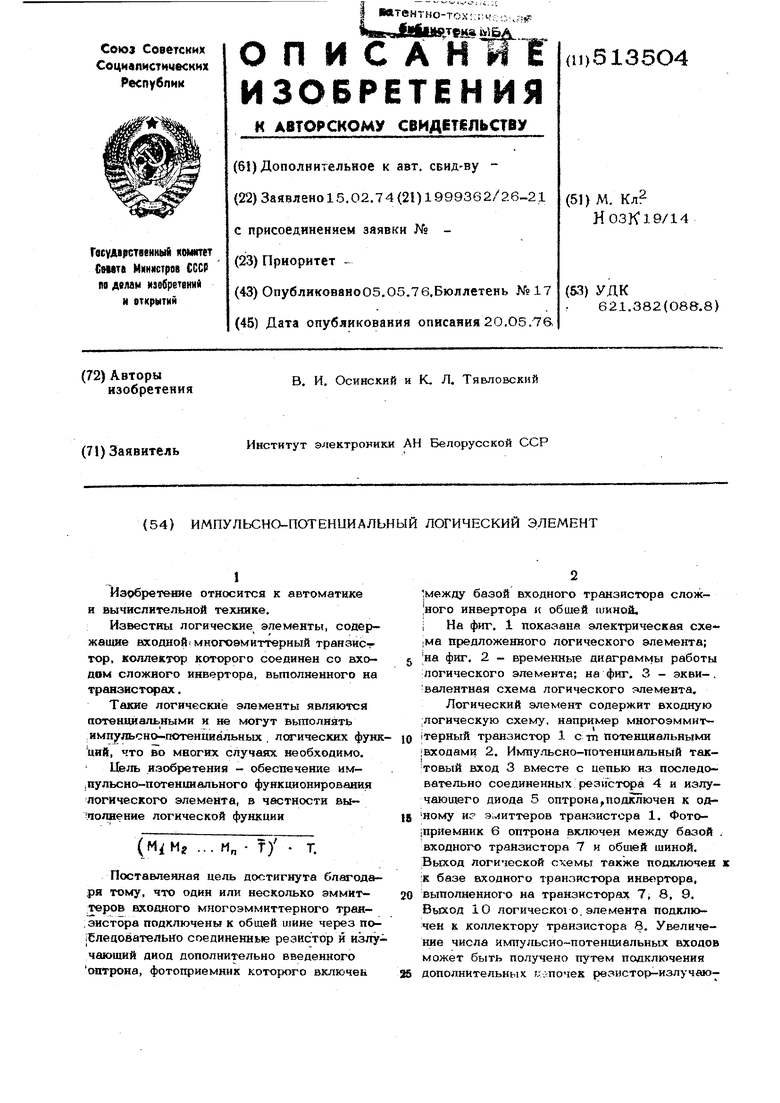

1между базой входного транзистора слож|ного инвертора н обшей шиной, I Ha фиг. 1 показана электрическая схе- Ма предложенного логического элемента; |на фиг. 2 - временные диаграм1иы работы логического элемента; на фиг. 3 - экви-. валентная схема логического элемента.

Логический элемент содержит входную :логнческую схему, например многоэммит1терный транзистор 1 с тп потенциальными входами 2. Импульсно-потенциальный тактовый ВХОД 3 вместе с цепью из последовательно соединенных резистора 4 и излучающего диода 5 оптрона,подключен к одному иг эмиттеров транзистора 1. Фото|приемник 6 оптрона включен между базой . ВХОДНОГО транзистора 7 и обиюй шиной. Выход логической схемы также подключен к ;к базе входного транзистора инвертора,

выполненного на транзисторах 7, 8, 9. Выход 10 логического, элемента подключен к коллектору транзистора 8. Увеличение числа импульсно потенциапьнь1Х входов может быть получено путем подключения

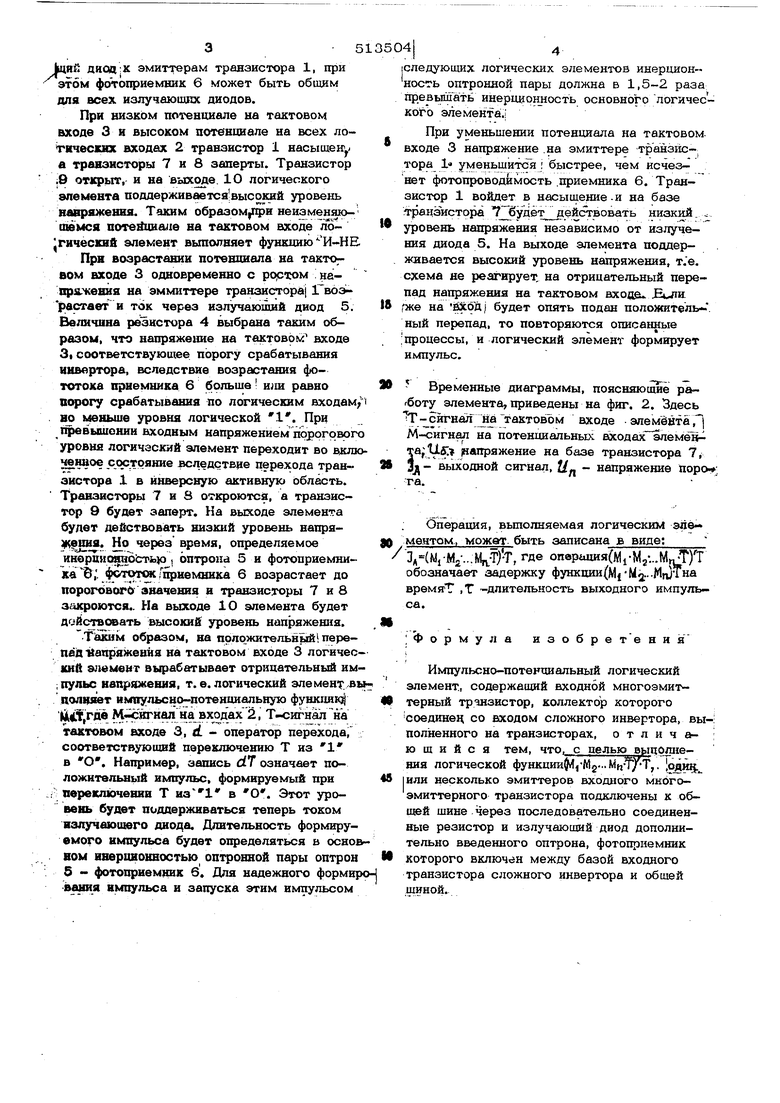

дополнительных кепочек резистор-излучаю:й диод-к эмиттерам транзистора 1, при этом фотоприемник 6 может быть общим для всех излучаюишх диодов. При низком потенциале на тактовом входе 3 и высоком потенциале на всех логических входах 2 транзистор 1 насыщен а траизисторы 7 и 8 заперты. Транзистор ;9 открьтт, и на выходе. 10 логического элемента поддержнваетсавысоювй уровень навряжения. Таким образом,1фн неизменяющемся потевЬшале на тактовом входе логический элемент выполняет функциюИ-НЕ При возрастании потенциала на тактогвом входе 3 одновременно с рортом : напряжения на эммиттере транзистора 1 воз { астает и ток через излучающий диод 5. Величина резистора 4 выбрана таким образом, что напряже1ше на тактовокс входе 3| соответствующее порогу срабатывания инвертора, вследствие возрастания фототока приемника 6 больше равно порогу срабатывания по логическим входам . во меньше уровня логической . При превышонии входным напряжением пороговог уровня логический элемент переходит во еклю ®WO сос;гряние вследствие перехода транзистора 1 в инверсную активную область. Транзисторы 7 и 8 откроются, а транзистор 9 будет заперт. На выходе элемента будет действовать низкий уровень напряНо через время, определяемое JtTbjo ) оптрона 5 и фотоприемнихаВ;. фотрт Гпрнемника 6 возрастает до порогового значения я транзисторы 7 и 8 закроются.. На выходе 10 элемента будет дойствоаать высокий уровень напряжения. TiaKUM образам, на положительный перепев Напряжения на тактовом входе 3 логичес кий элемент вырабатывает отрицательный им ; пульс напряжения, т. е. логический злемент/в полцяет и Л1ульсно-потеншсальную функцяМ iiitirjcie Мт-сктиал на входах 2, Т-сигнал на тактовом входе 3, d. - оператор перехода, соответствующий переключению Т из в О . Например, запись CLT означает положительный импульс, формируемый при г- пореключенкн Т из в О. Этот уровень будет поддерживаться теперь током излучающего диода. Длительность формируемого импульса будет определяться в осно вом иверциоывостью оптронной пары оптрон 5 - фотоприемник 6. Для надежного форми ватя импульса и запуска этим импульсом ледующих логических элементов инерционность оптронной пары должна в 1,5-2 раза превышать инерщ1он ность основного логического элемента. При уменьшении потенциала на тактовом входе 3 напряжение .на эмиттере транэ11х:тора 1 уменьшится i быстрее, чем исчезнет фотопроводимость .приемника 6. Транзистор 1 войдет в насыщение -и на базе транзистора 7 удёт дейс гвовать низкий. уровень напряжения независимо от излучения диода 5. На выходе элемента поддерживается высокий уровень напряжения, т.е. схема не реагирует, на отрицательный перепад напряжения на тактовом вхоц fжe на ВЗсод) будет опять подан положитель ный перепад, то повторяются описанные процессы, и логический элемент формирует импульс. Временные диаграммы, поясняющие работу элемента, приведены на фиг. 2. Здесь -c HTHaJfjiaтактовом входе элемента, М-сигнал на потенциальных аходазс элемёнTa;tl5; (напряжение на базе транзистора 7, Зд - выходной сигнал, 2/ - напряжение та. : Операция, вьшолняемая логическим эле- ментом, может быть записана в виде; ,-М2...ад-Т, где операция(М1.М,,....М„;Т)Т обозначает задержку функшш(М|М2...-Мц)чна времяТ , Т -длительность выходного импульса. Формула изобретения Импульсно-потекциальный логический элемент, содержащий входной многоэмиттерный транзистор, коллектор которого соединен со входом сложного инвертора, выполненного на транзисторах, о т л и ч а- ; ю щ и и с я тем, что, с целью выдолнения логической функции |М2- Мц-Т/Т,. IOJH |или несколько эмиттеров входного мнЬгоэмиттерного транзистора подключены к общей шине через последовательно соединенные резистор и излучающий диод дополнительно введенного оптрона, фотоприемник которого включен между базой входного транзистора сложного инвертора и обшей шиной.

Фиг. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсно-потенциальный логический элемент | 1978 |

|

SU758523A1 |

| Оптоэлектронный модуль | 1987 |

|

SU1444940A1 |

| Интегральный динамический элемент | 1971 |

|

SU559381A1 |

| Формирователь импульсов | 1981 |

|

SU1018213A1 |

| Интегральный динамический элемент | 1980 |

|

SU906005A2 |

| Оптоэлектронный модуль | 1986 |

|

SU1368987A1 |

| Интегральная логическая схема | 1979 |

|

SU1001479A1 |

| Стабилизированный источник питания постоянного тока | 1990 |

|

SU1711138A1 |

| Синхронный @ -Триггер | 1985 |

|

SU1336208A1 |

| Согласующее устройство | 1977 |

|

SU660213A1 |

Фиг. 2

ОИ О О

М

9

tft.J

Авторы

Даты

1976-05-05—Публикация

1974-02-15—Подача