(5) ИНТЕГРАЛЬНАЯ ЛОГИЧЕСКАЯ СХЕМА

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1982 |

|

SU1058061A1 |

| Интегральная логическая схема | 1979 |

|

SU860314A1 |

| Маломощный транзисторный логический элемент | 1988 |

|

SU1598157A1 |

| Интегральная логическая схема (ее варианты) | 1984 |

|

SU1228260A1 |

| Логический элемент | 1985 |

|

SU1275758A1 |

| Интегральный транзисторно-транзисторный логический элемент | 1980 |

|

SU902261A1 |

| Двойной инвертор с минимальной асимметрией | 1984 |

|

SU1499483A1 |

| Транзисторный логический элемент | 1988 |

|

SU1621165A1 |

| Интегральная логическая схема | 1979 |

|

SU1001480A1 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

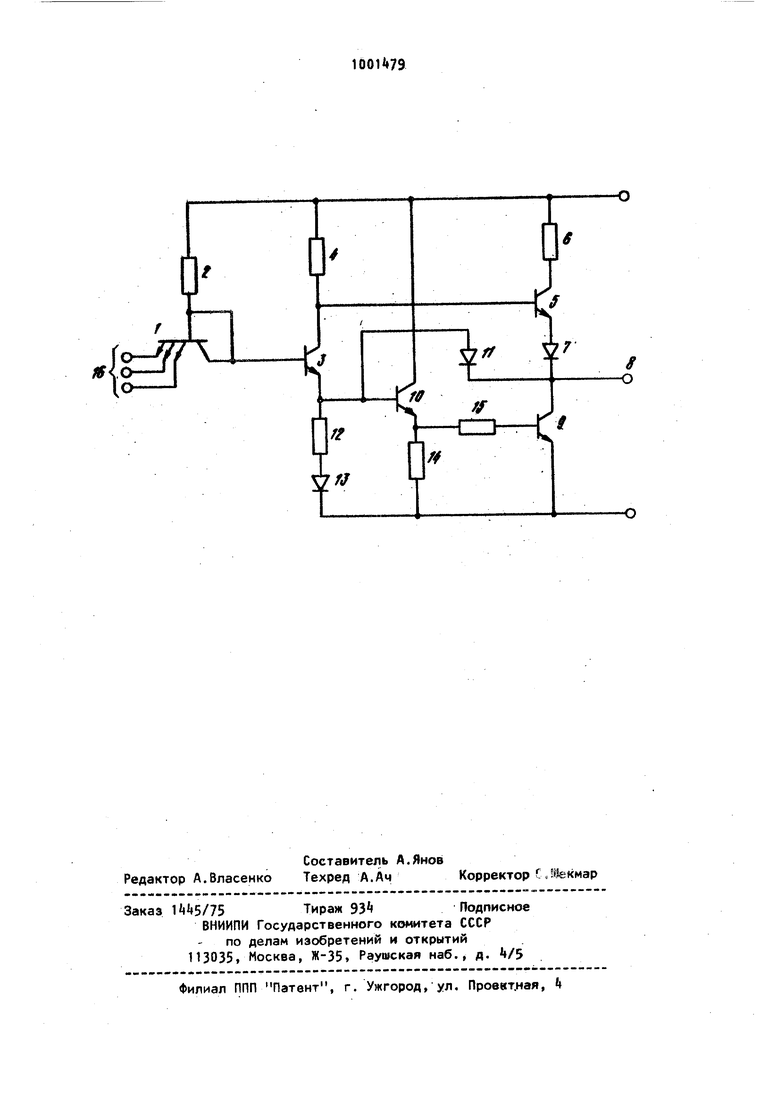

Изобретение относится к микроэлек ронике и может быть использовано в вычислительной технике и в система дискретной автоматики. Известен инвертор, в котором повы шеиие быстродействия обусловлено тем что крутизна фронтов выходного импул са сохраняется, а амплитуда перепада уменьшается за счет введения цепи, состоящей из нескольких диодов и транзистора Cl 1 Недостатком указанного инвертора является повышенное потребление мощности от источника питания в состоянии логической 1 и пониженное значение выходного напряжения логической 1. Известен также ТТЛ элемент, содер жащий входной многоэмиттерный транзистор, ..двухэмиттерный фазоразделитеяьный и выходной транзисторы, резисторы и ускоряющую цепь. База многозмиттерного и коллектор фазоразделйтельного транзисторов соединены че рез резисторы с шиной питания, коллектор первого упомянутого транзистора соединен с базой второго. Один эмиттер фазовращательного транзистора соединен с базой выходного транзистора и через резистор с общей шиной, второй эмиттер соединен с коллектором выходного транзистора с ускоряющейся цепью и выходом элемента . Недостатком известного элемента , является то, что через транзистор ускоряющей цепи при включении выходного транзистора протекают существен ные импульсные токи, в то же время величина базового тока упомянутого транзистора ограничена резистором, включенным между коллектором фазоразделительного транзистора и шиной питания, величину которого нельзя уменьшать, так как это приводит, к расту потребляемой мощности, указанные обстоятельства приводят к увели-. чени времени включения выходного транзистора и росту потребляемой мощности при повышении частоты переключения (за счет развития бросков импульсных токов), а такж% ограничению нагрузочной способности в состоянии логического О. Цель изобретения - уменьшение потребляемой мощности и увеличение быстродействующей нагрузочной способности. Поставленная цель достигается тем, что в интегральную логическую схему, содержацую входной многоэмиттерный транзистор, .база которого через резистор соединена с шиной питания, коллектор - с базой фазоразделительного транзистора, коллектор которого через резистор соединен с шиной питания и базой транзистора ускоряющей це пи, коллектор которого через резистор соединен с шиной питания, эмиттер через диод - с коллектором выходного транзистора и BMXOAOMJ эмиттер выходного транзистора соединен с общей шиной, введен дополнительный транзистор кстлектор которого соединен с шиной питания, база - с эмиттером фазоразде лительного транзистора, через дополни тельный диод- с коллектором выходного транзистора и через последовательно соединенные диод и резистор - с общей шиной, эмиттер дополнительного транзистора соединен через соответствующиа резисторы с общей шиной и бйзой выходного транзистора, при этом коллектор выходного многоэмиттерного тра зистора подключен к его базе. На чертеже изображена схема устроиства. Устройство содержит входной многоэмиттерный транзистор 1, база которого подключена к источнику питания через резистор 2 и фазоразделительный транзистор 3, коллектор которого через резистор Ц подключен к источнику питания. База транзистора 3 соединена с коллектором и базой транзистора 1. В схеме имеется ускоряющая цепь, состоящая из транзистора 5i база которого срединена с коллектором транзистора 3, коллектор через резистор 6 - с источником питания, а эмиттер - с анодон диода 7, катод которог соединен с выходом 8 и коллектором выходного транзистора 9, эмиттер тран зистора 9 подключен к общей шине питзния, коллектор дополнительного тран зистора 10 соединен с источником питания, база - с эмиттером транзистора 3, с анодом дополнительного диода 11, катод которого подключен к выходу 8, и с резистором 12, второй конец которого подключен к аноду диода 13, катод которого соединен с общей шиной, эмиттер транзистора 10 соединен с резисторами Т и 15, вторые концы которых соединены соответственно с общей шиной питания и базой транзистора 9- Эмиттеры транзистора 1 подклю.чены к вхбду устройства. Предлагаемое устройство работает следующим образом. Если на часть входов 16 (или на все) подан низкий уровень напряжения, фазоразделительный транзистор 3 закрыт, следов-ательно, закрыт и выходной транзистор 3, так как в базу его не втекает ток, и на выходе 8 схемы высокий уровень напряжения. Если на все входы 1б подать высокий уровень напряжения, фазоразделительный транзистор 3 откроется и через него потечет ток, который разветвится: часть потечет в цепь, состоящую из резистора 12 и диода 13, а часть - в базу транзистора 10, включенного по схеме эмиттерного повторителя. При этом в базу транзистора 9 задается избыточный ток, обес- пемивающий его быстрое включение, причем величина этого избыточного тока может быть весьма значительной и ограничивается, практически, лишь резистором 15, сопротивление которого выполняется небольшой величины. В начальный момент времени, когда транзистор 9 еще не включился, ток через диод 11 протекать не может и падение напряжения на резисторах i и 12 примерно равны. Напряжение на базе транзистора 5 быстро снижается, что также способствует более быстрому включению выходного транзистора 9. Как только включится выходной транзистор 9, и на его коллекторе напряжение станет равным.падению напряжения на прямосмещенном р-п-переходе, через диод 11 начинает протекать ток, ответвля(ощий 1 часть тока из базы дополнительного транзистора 10 в коллекторную часть выходного транзистора 9. Таким образом, через транзистор 10 протекает ток, необходимый лишь для создания на резисторе 14 падения

510

напряжения, равного прямому падению напряжения на база-эмиттерном переходе выходного транзистора 9 и базовый ток транзистора 9.

При этом уменьшается базовый ток транзистора 10 и его Ёеличина определяется коэффициентом усиления транзистора9 а весь избыточный ток протекает через диод 11 в коллектор транзистора

Таким образом, обеспечивается ограничение степени насьЦения выходного транзистора 9 снижение потребляемой мощности, так как резистор k может в этом случае быть сравнительно большой величины, поскольку не он определяет величину базового тока транзистора Э., а также повышение нагрузочной способности схемы в состоянии логического О, так как при увеличении тока нагрузки часть тока, протекакядего через диод 11, перераспределяется в базу дополнительного транзистора 10 и вызывает увеличение базового тока транзистора 9Если теперь на части входов 16 (или на всех) вновь создать низкий уробень напряжения, транзистор 3 выключается, при этом прекращается ток в базу выходного транзистора, а так как отсутствует избыточный базовый ток, выходной транзистор 9 быстро выключается. При этом будет с ественно меньшим и бросок тока при выключении схемы через форсирующую цепь.

Формула изобретения Интегральная логическая схема, содержащая входной многоэмиттерный

796

транзистор, база которого через, резистор соединена с шиной питания, коллектор - с базой фазоразделительно о транзистора, коллектор которого через резистор соединен с шиной питания и базой транзистора ускоряющей цепи, коллектор которого через резистор соединен с шиной питания, эмиттер через диод - с коллектором выходного транзистора и выходом, эмиттер выходного транзистора соединен с общей шиной, отличающаяся тем, что, с целью уменьшения потребляемой мощности, увеличения быстродействия и нагрузочной способности, введен дополнительный транзистор, коллектор которого соединен с шиной питания, база - с эмиттером фазоразделительного транзистора, через дополнительный диод - с коллектором выходного транзистора и через последовательно соединенные диод и резистор - с общей шиной, эмиттер дополнительного транзистора соединен через соответствующие резисторы с общей шиной и базой выходного транзистора, при этом коллектор входного многоэмиттерного транзистора подключен к его базе.

Источники информации, принятые во внимание при экспертизе

2,Шагурин И,И. Транзисторно-транзисторные логические схемы, Н., Советское радио, 197, с,96,

рис. 3, (прототип).

Авторы

Даты

1983-02-28—Публикация

1979-09-07—Подача