1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых микроэлектронных устройствах.

Известен импульсно-потенциальный логический элемент, содержащий входной многоэмиттерный транзистор, коллектор которого соединен со входом сложного инвертора, выполненного на транзисторах, один или несколько эмиттеров многоэмиттерного транзистора подключены к общей щине через последовательно соединенные резистор и излучающий диод оптрона, фотоприемник которого включен между базой входного транзистора сложного инвертора и общей щиной 1.

Такой элемент способен выполнять только простые импульсно-потенциальные логические функции.

Известны логические элементы, выполняющие усложненные логические функции, содержащие входные цепи на транзисторах, подключенные к эмиттерам многоэмиттерного транзистора, коллектор которого соединен со входом сложного инвертора на транзисторах 2 .

Такие логические элементы являются потенциальными и не могут выполнять импульсно-потенциальных логических ({пункций.

Цель изобретения--расщирение функциональных возможностей логического элемента выполнение.м импу.тьсно-пот нуда 1ьной логической функции LT-fl А; И В,,Ск.

iM (

Для достижения поставленной цели в логическом эле.менте, содержащем многоэмиттерный транзистор, к эмиттерам которого 10 подключены входные цепи, и выходной инвертор, к базе многоэмиттерного транзистора подключен коллектор дополнительного транзистора, база которого через резистор соединена с одним из эмиттеров многоэмиттерного транзистора и с тактовым входом, а эмиттер - с управляющим входом импульсно-потенциального логического элемента.

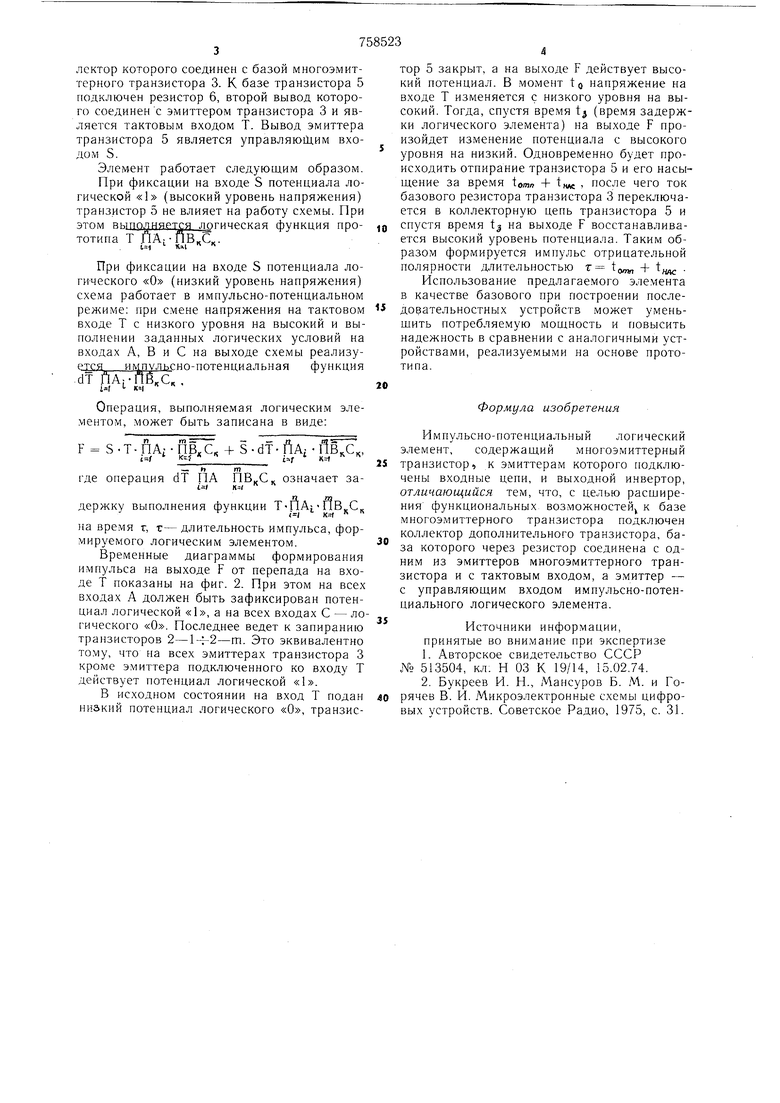

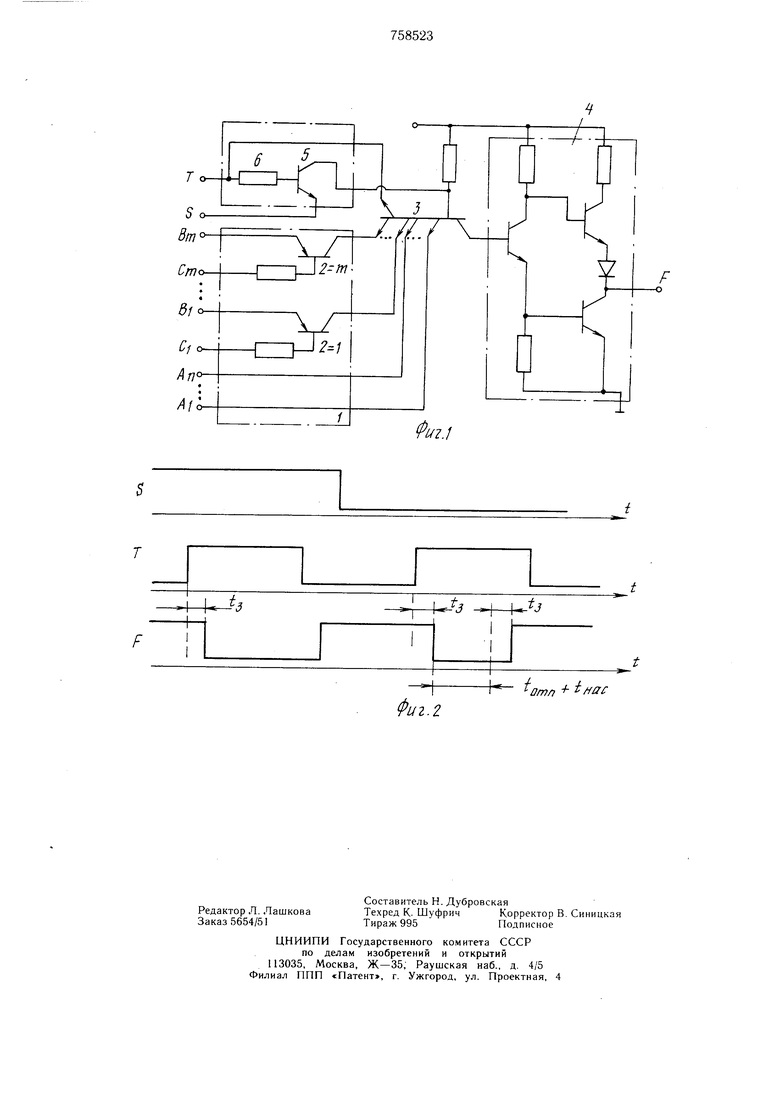

На фиг. 1 представлена принципиальная схема элемента; на фиг. 2 - временная 20 диаграмма работы логического элемента.

Логический элемент содержит входные цепи 1 на транзисторах многоэмиттерный транзистор 3, выходной инвертор 4 и дополнительный транзистор 5, коллектор которого соединен с базой многоэмиттерного транзистора 3. К базе транзистора 5 подключен резистор 6, второй вывод которого соединенс эмиттером транзистора 3 и является тактовым входом Т. Вывод эмиттера транзистора 5 является управляющим входом S. Элемент работает следуюндим образом. При фиксации на входе S потенциала логической «1 (высокий уровень напряжения) транзистор 5 не влияет на работу схемы. При этом выполняется логическая функция прототипа Т ftA: ПВ-С,. Ия1 При фиксации на входе S потенциала логического «О (низкий уровень напряжения) схема работает в импульсно-потенциальном режиме: при смене напряжения на тактовом входе Т с низкого уровня на высокий и выполнении заданных логических условий на входах А, В и С на выходе схемы реализуется импульсно-потенциальная функция dT ЛА-ПВ.С . i( кч Операция, выполняемая логическим элементом, может быть записана в виде: F 5-Т-ПА;-ПВ.С + S-dT-ftAi , fcf ы где операция dT ПА означает зай( держку выполнения функции ТПА; ПВ С па время г, т- длительность импульса, формируемого логическим элементом. Временные диаграммы формирования импульса на выходе F от перепада на входе Т показаны на фиг. 2. При этом на всех входах А должен быть зафиксирован потенциал логической «1, а на всех входах С - логического «О. Последнее ведет к запиранию транзисторов . Это эквивалентно тому, что на всех эмиттерах транзистора 3 кроме эмиттера подключенного ко входу Т действует потенциал логической «1. В исходном состоянии на вход Т подан низкий потенциал логического «О, транзистор 5 закрыт, а на выходе F действует высокий потенциал. В момент to напряжение на входе Т изменяется с низкого уровня на высокий. Тогда, спустя время t (время задержки логического элемента) на выходе F произойдет изменение потенциала с высокого уровня на низкий. Одновременно будет происходить отпирание транзистора 5 и его насыщение за время lom + нм . после чего ток базового резистора транзистора 3 переключается в коллекторную цепь транзистора 5 и спустя время t на выходе F восстанавливается высокий уровень потенциала. Таким образом формируется импульс отрицательной полярности длительностью г ig, + t, . Использование предлагаемого элемента в качестве базового при построении последовательностных устройств может уменьшить потребляемую мощность и повысить надежность в сравнении с аналогичными устройствами, реализуемыми на основе прототипа. Формула изобретения Импульсно-потенциальный логический элемент, содержащий многоэмиттерный транзистор к эмиттерам которого подключены входные цепи, и выходной инвертор, отличающийся тем, что, с целью расщирения функциональных возможностей к базе многоэмиттерного транзистора подключен коллектор дополнительного транзистора, база которого через резистор соединена с одним из эмиттеров многоэмиттерного транзистора и с тактовым входом, а э.миттер - с управляющим входом импульсно-потенциального логического элемента. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 513504, кл. Н 03 К 19/14, 15.02.74. 2.Букреев И. Н., Мансуров Б. М. и Горячев В. И. Микроэлектронные схемы цифровых устройств. Советское Радио, 1975, с. 31.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсно-потенциальный логический элемент | 1974 |

|

SU513504A1 |

| ИМПУЛЬСНЫЙ ДВУХФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «И—ИЛИ/И—ИЛИ—НЕ» | 1971 |

|

SU304698A1 |

| Логический элемент и-не | 1973 |

|

SU531283A1 |

| Транзисторно-транзисторный логический элемент | 1983 |

|

SU1128387A1 |

| Интегральный динамический элемент | 1971 |

|

SU559381A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1973 |

|

SU369714A1 |

| Логический элемент и-не | 1979 |

|

SU790336A1 |

| ТТЛ-инвертор | 1981 |

|

SU1035802A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ТТЛ-элемент | 1985 |

|

SU1277382A1 |

i

1 ГТ

J

J

af

Фиг.2

Авторы

Даты

1980-08-23—Публикация

1978-03-17—Подача