1

Изобретение относится к аппаратуре для приема дискретных сообщений в классе синхронных передач, кодированных с постоянным весом.

Известно устройство для дискретного приема сигналов «в целом, содержаи1,ее распределитель сигналов, каждый выход которого через запоминающий блок подключен к решающей схеме, причем управляющие входы распределителя сигналов, запоминающего блока и решающей схемы соединены с выходами блока управления, вход которого соединен с входом устройства через блок синхронизации. Однако из-за низкой стабильности такое устройство .имеет недостаточно высокую достоверность приема сигналов.

Для повыщения достоверности приема сигналов в предлагаемом устройстве к входу распределителя сигналов и входу блока синхронизации подключен блок дискретизации длительности элементарных посылок, состоящий из последовательно соединенных пороговой схемы и управляемого ключа, к управляющему входу которого подключен элемент И, входы которого соединены с дополнительными выходами блока управления.

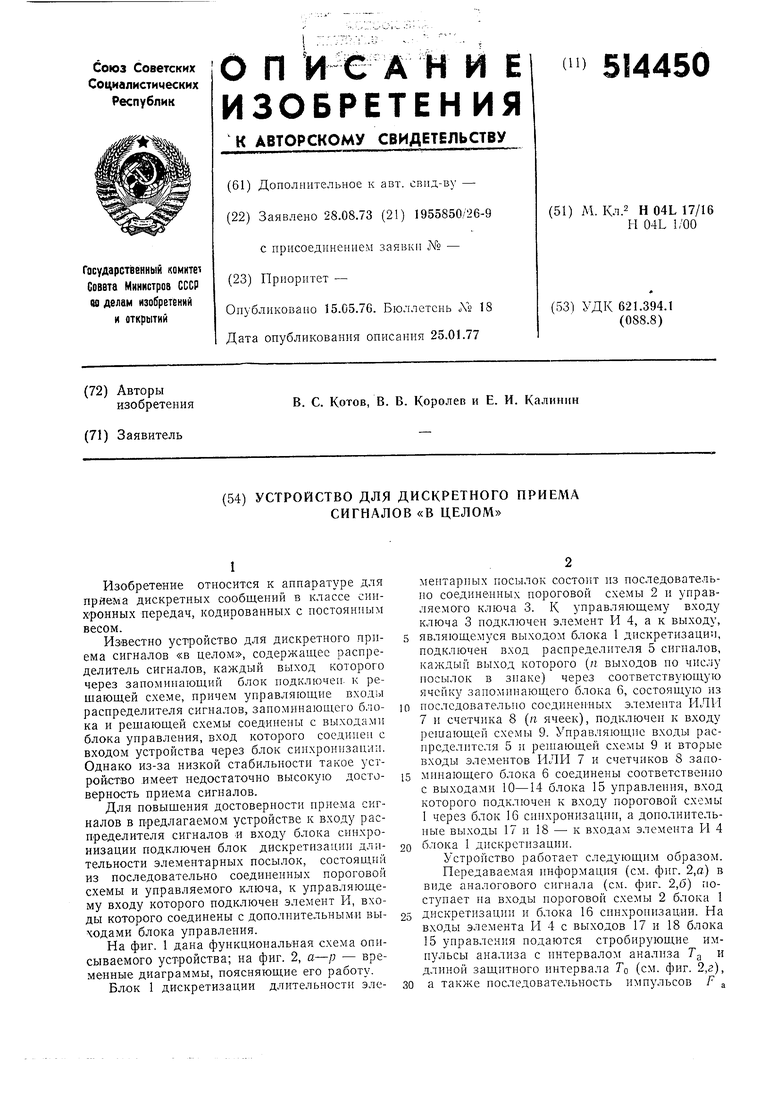

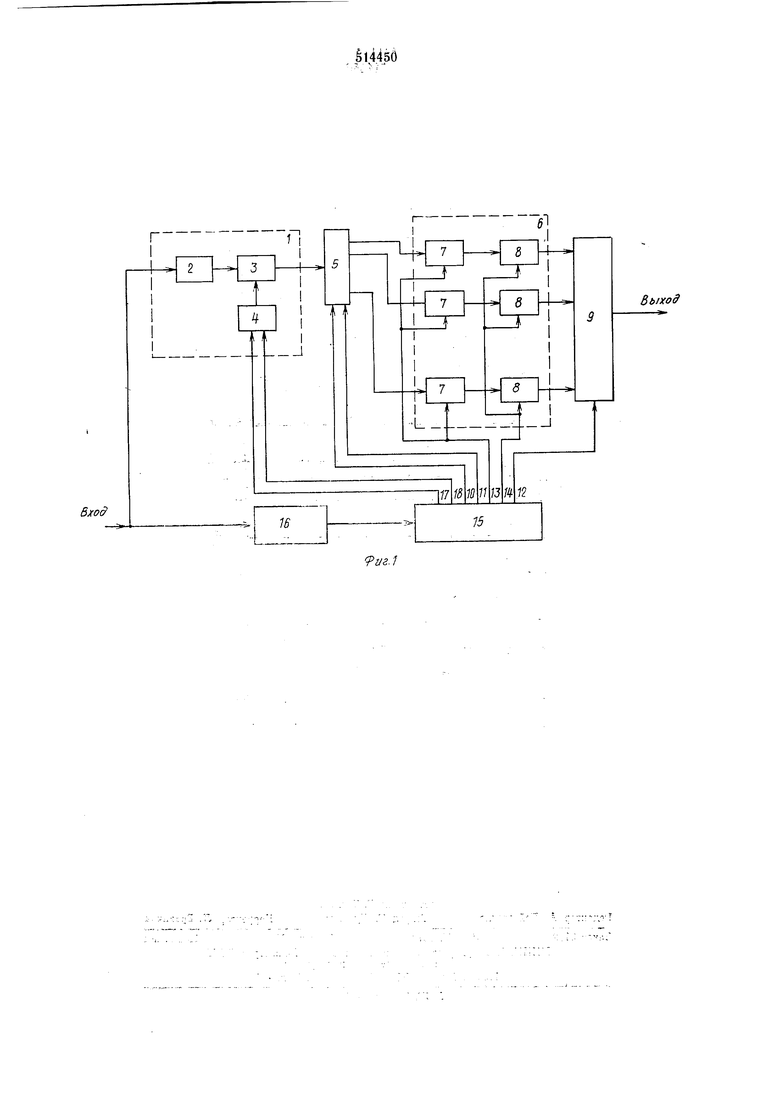

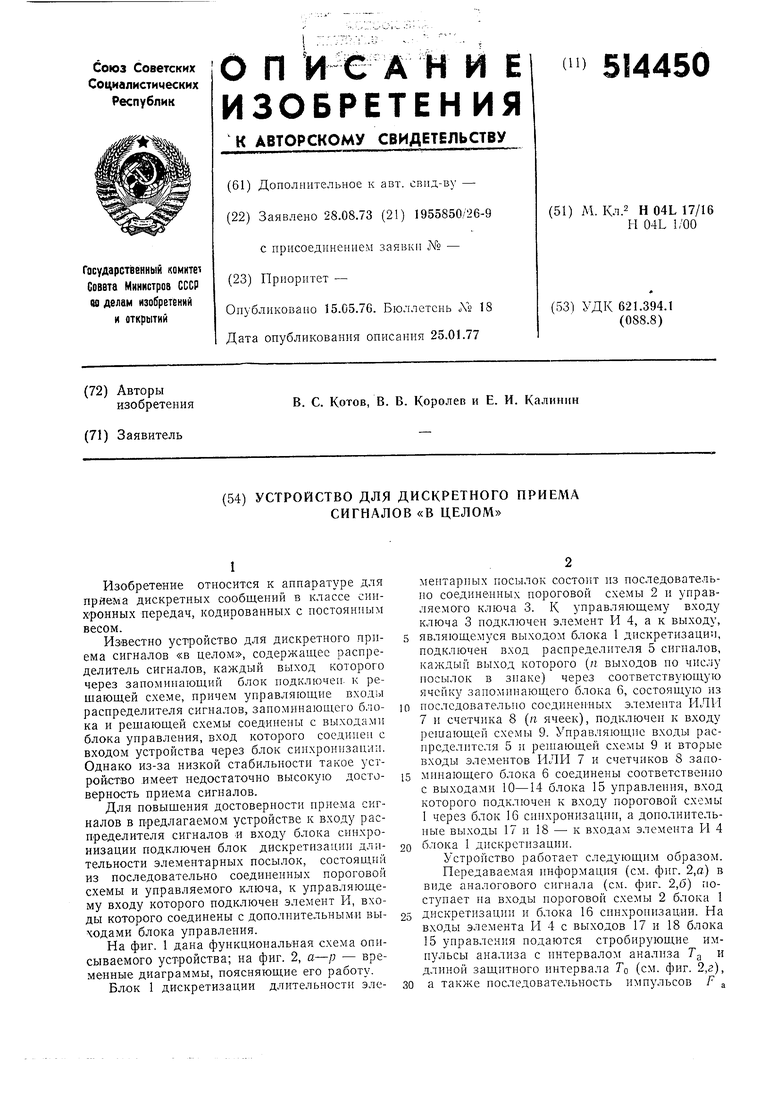

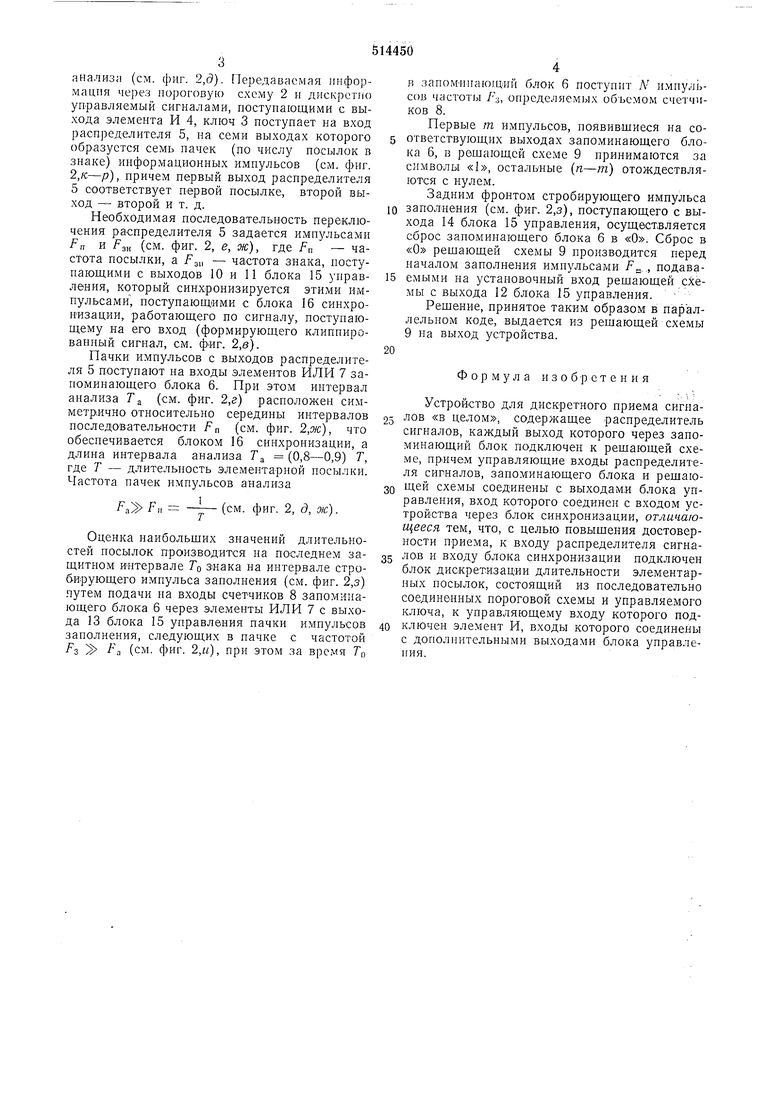

На фиг. 1 дана функциональная схема описываемого устройства; на фиг. 2, а-/; - временные диаграммы, поясняющие его работу.

Блок 1 дискретизации длительности элементарных посылок состоит из последовательно соединенных пороговой схемы 2 и управляемого ключа 3. К управляющему входу ключа 3 подключен элемент И 4, а к выходу, являющемуся выходом блока 1 дискретизации, подключен вход распределителя 5 сигналов, каждый выход которого (п выходов по числу посылок в знаке) через соответствующую ячейку запоминающего блока 6, состоящую из

нослсдовательпо соединенных элемента ИЛИ 7 и счетчика 8 (п ячеек), подключен к входу решающей схемы 9. Управляющие входы распределителя 5 и решающей схемы 9 и вторые входы элементов ИЛИ 7 и счетчиков 8 заноминающего блока 6 соединены соответственно с выходами 10-14 блока 15 управления, вход которого подключен к входу нороговой схемы 1 через блок 16 синхронизации, а дополнительные выходы 17 и 18 - к входам элемента Р1 4

блока 1 дискретизации.

Устройство работает следующим образом. Иередаваемая информация (см. фиг. 2,а) в виде аналогового сигнала (см. фиг. 2,6) поступает па входы пороговой схемы 2 блока 1

дискретизации и блока 16 синхронизации. Иа В.ХОДЫ элемента И 4 с выходов 17 и 18 блока 15 унравления подаются стробирующие импульсы анализа с интервалом анализа Т и длиной защитного интервала Го (см. фиг. 2,г),

а также последовательность импульсов Г

анализа (см. фиг. 2,(). Передаваемая информация через пороговую схему 2 и дискретно управляемый сигналами, поступающими с выхода элемента И 4, ключ 3 поступает на вход расаределителя 5, на семи выходах которого образуется семь пачек (по числу посылок в знаке) информационных импульсов (см. фиг. 2,к-р), причем первый выход распределителя 5 соответствует первой посылке, второй выход - второй и т. д.

Необходимая последовательность переключения распределителя 5 задается имп льсами РП и .РЗН (см. фиг. 2, е, ж, где Fn - частота посылки, а зп - частота знака, поступающими с выходов 10 и 11 блока 15 управления, который синхронизируется этими импульсами, постунающйми с блока 16 синхронизации, работающего по сигналу, поступающему на его вход (формирующего клиппированный сигнал, см. фиг. 2,в).

Пачки импульсов с выходов распределителя 5 поступагот на входы элементов ИЛИ 7 запоминающего блока 6. При этом интервал анализа Г (см. фиг. 2,г) расположен симметрично относительно середины интервалов последовательности Рц (см. фиг. 2,з/с), что обеспечивается блоком 16 синхронизации, а длина интервала анализа Т (0,8-0,9) Т, где Т - длительность элементарной посылки. Частота пачек импульсов анализа

(см. фиг. 2, д, 01с).

fa F,,

Оценка наибольших значений длительностей посылок производится на последнем защитном интервале Го з-нака на интервале стробирующего импульса заполнения (см. фиг. 2,з) путем подачи на входы счетчиков 8 запоминающего блока 6 через элементы ИЛИ 7 с выхода 13 блока 15 управления пачки импульсов заполнения, следующих в пачке с частотой 3 2 а (см. фиг. 2,гг), при этом за время Т

в запомИнающ11гй блок 6 поступит Л и.мпульсов частоты /з, определяемых объемом счетчиков 8.

Первые т импульсов, появившиеся на соответствующих выходах запоминающего блока 6, в рещающей схеме 9 принимаются за символы «I, остальные (п-пг) отождествляются с нулем.

Задним фронтом стробирующего имнульса запол«ения (см. фиг. 2,з), поступающего с выхода 14 блока 15 управления, осуществляется сброс запоминающего блока 6 в «О. Сброс в «О решающей схемы 9 нроизводится неред началом заполнения импульсами f д.., подаваемыми на установочный вход рещающей схемы с выхода 12 блока 15 управления. Решение, принятое таким образом в параллельном коде, выдается из решающей схемы 9 на выход устройства.

Формула изобретения

Устройство для дискретного приема сигналов «в целом, содержащее распределитель сигналов, каждый выход которого через запоминающий блок подключен к рещающей схеме, причем управляющие входы распределителя сигналов, запоминающего блока п решающей схемы соединены с выходами блока управления, вход которого соединен с входом устройства через блок синхронизации, отличающееся тем, что, с целью повыщения достоверности приема, к входу распределителя сигналов и входу блока синхронизации подключен блок дискретизации длительности элементарных посылок, состоящий из последовательно соединенных пороговой схемы и управляемого ключа, к управляющему входу которого подключей элемент И, входы которого соединены с дополнительными выходами блока управления.

11

О 1

О о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дискретного приема сигналов в "целом | 1982 |

|

SU1140260A1 |

| Устройство определения скорости телеграфирования | 1972 |

|

SU474114A1 |

| Устройство приема двоичных сигналов | 1984 |

|

SU1197116A1 |

| Устройство поэлементной синхронизации и регенерации | 1978 |

|

SU741479A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Регенератор двоичных сигналов | 1977 |

|

SU743211A1 |

| Устройство для приема информации | 1983 |

|

SU1088051A1 |

| Демодулятор с перестраиваемым алгоритмом | 1973 |

|

SU540399A1 |

| Регенератор двоичных сигналов | 1979 |

|

SU794752A1 |

| УСТРОЙСТВО ПОИСКА СИГНАЛОВ | 2009 |

|

RU2422982C2 |

У

g

Та

г

е ж

п

К

Л

м и о

/7 Р

V7

Г

J I

-F Fn

иг.2

Авторы

Даты

1976-05-15—Публикация

1973-08-28—Подача