1

Изобретение относится к связи и предназначено для приему двоичных сигналов в синхронных системах связи, в которых отсутствует синхронизция до начала сообщения, а ее источ НИКОМ являются информационные посыпки сообщения.

Цель изобретения - повышение точности приема двоичной информации.

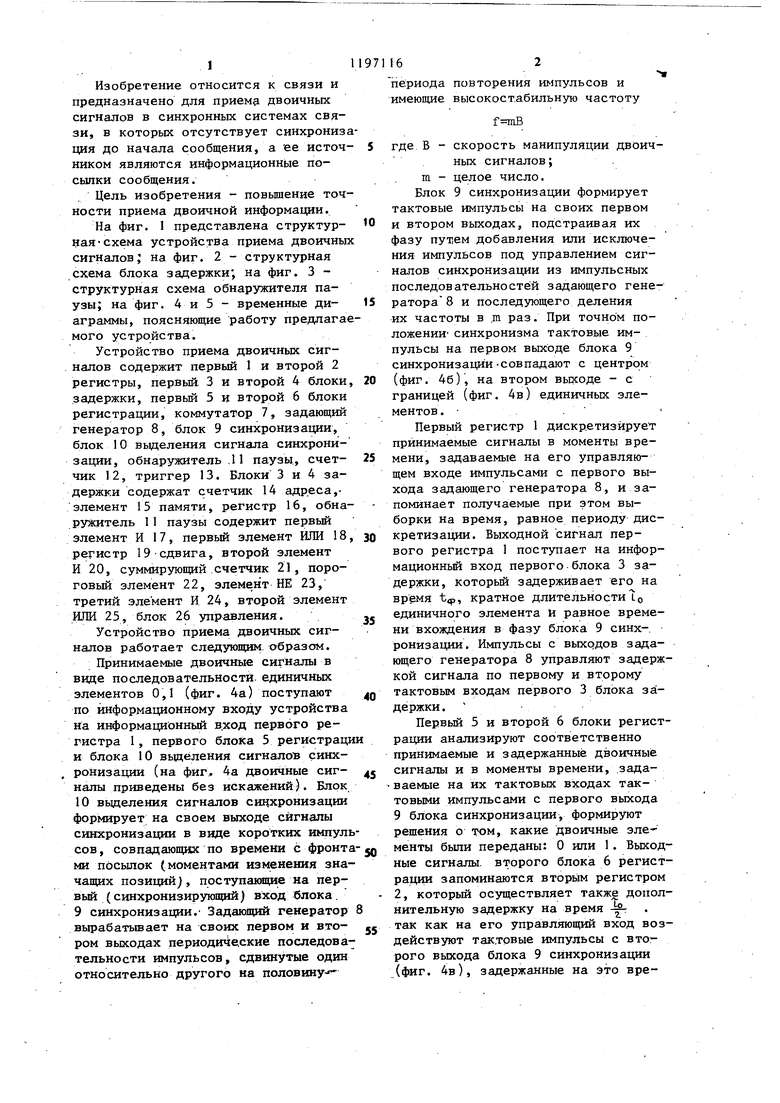

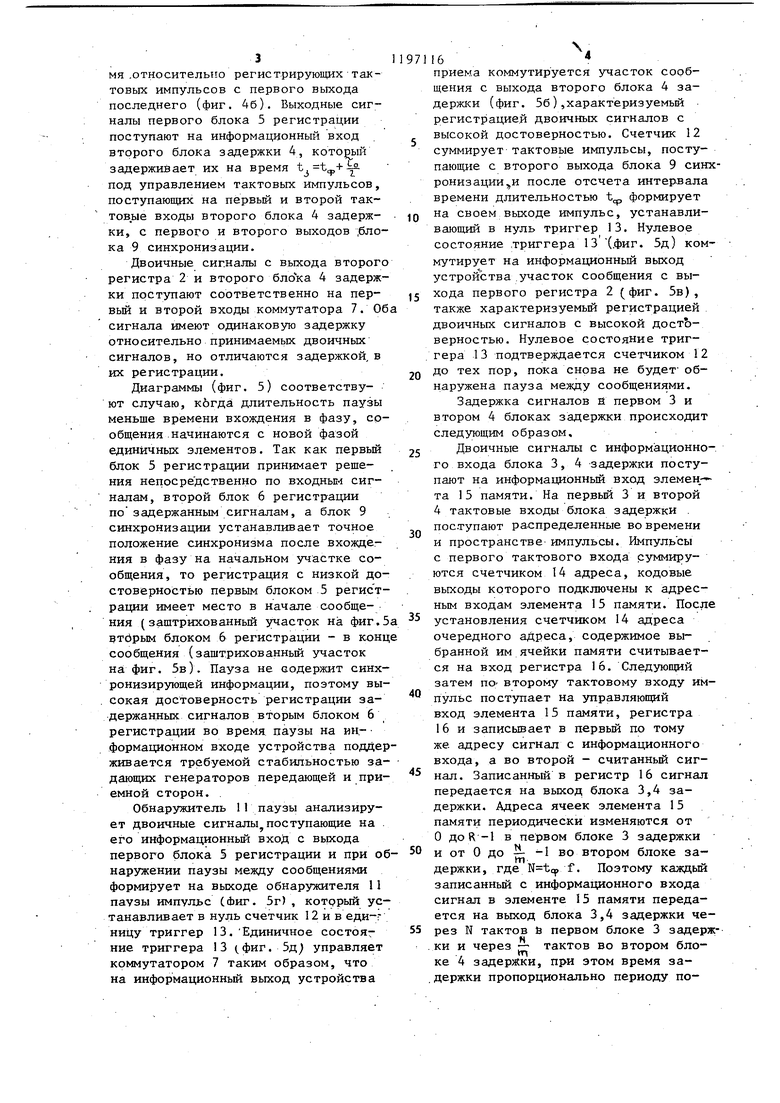

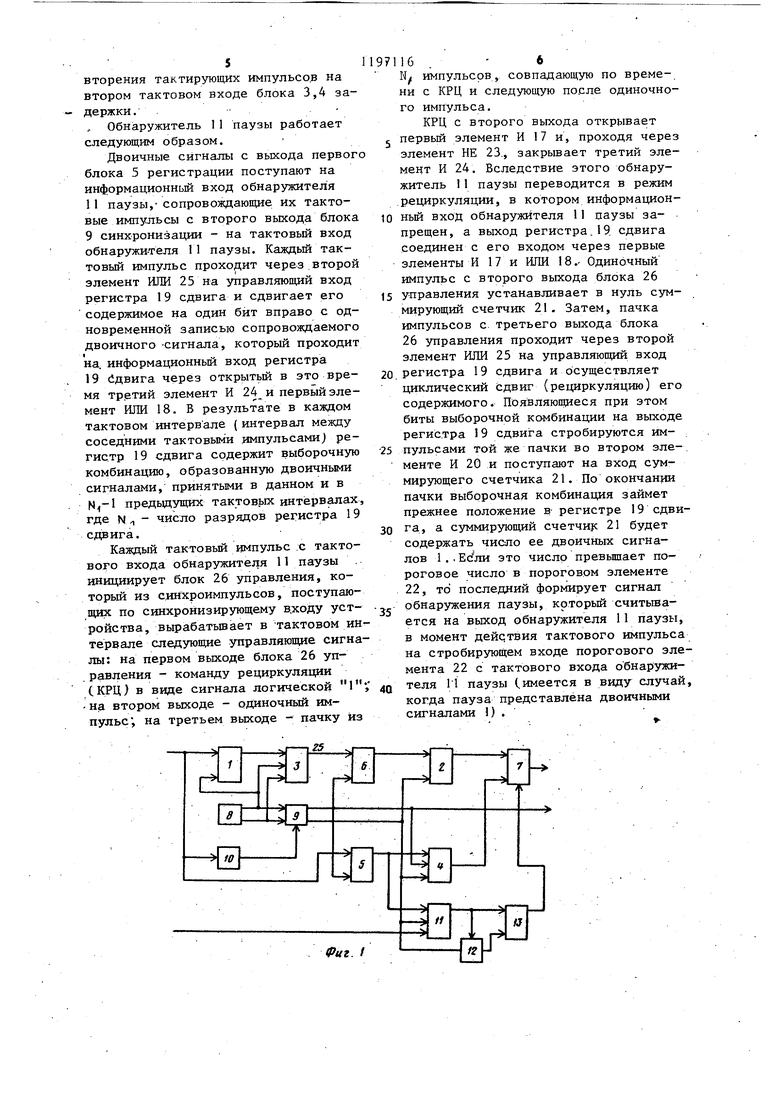

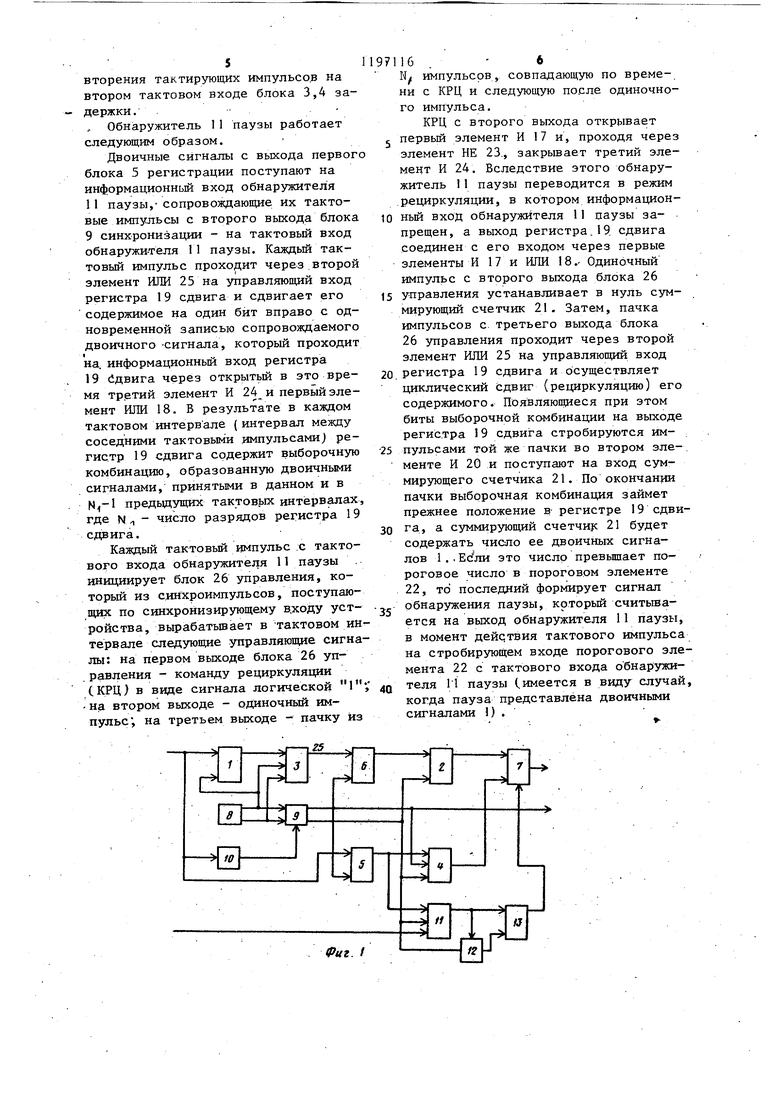

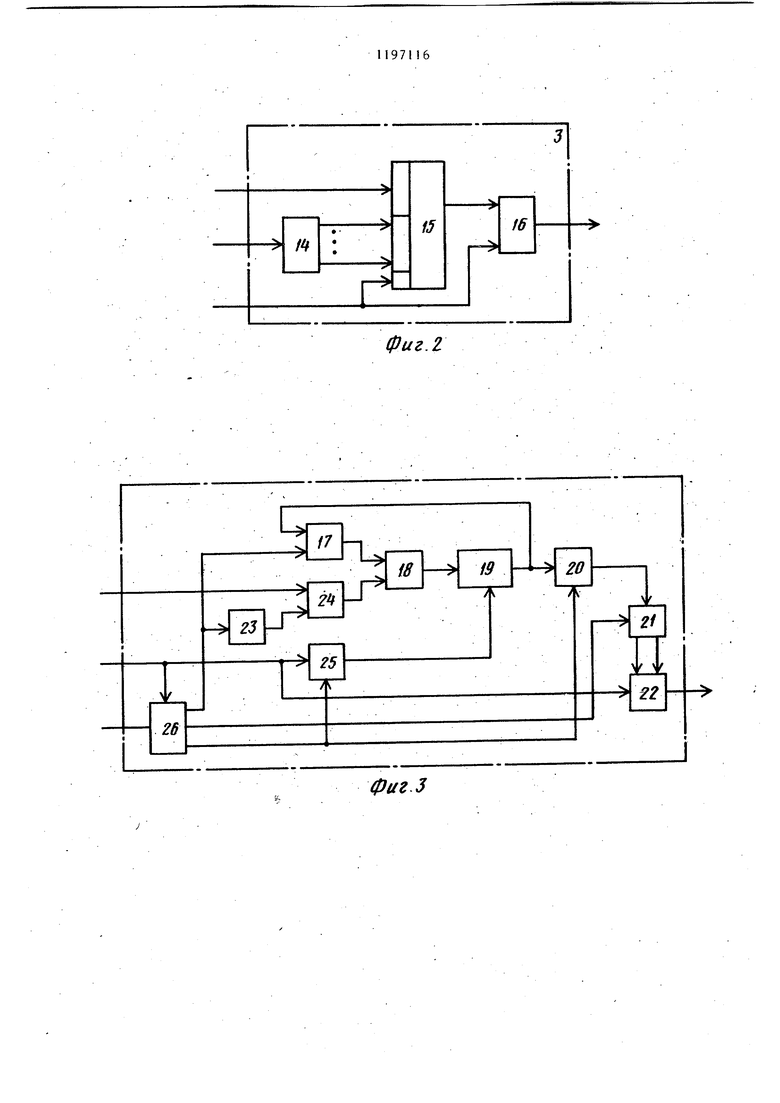

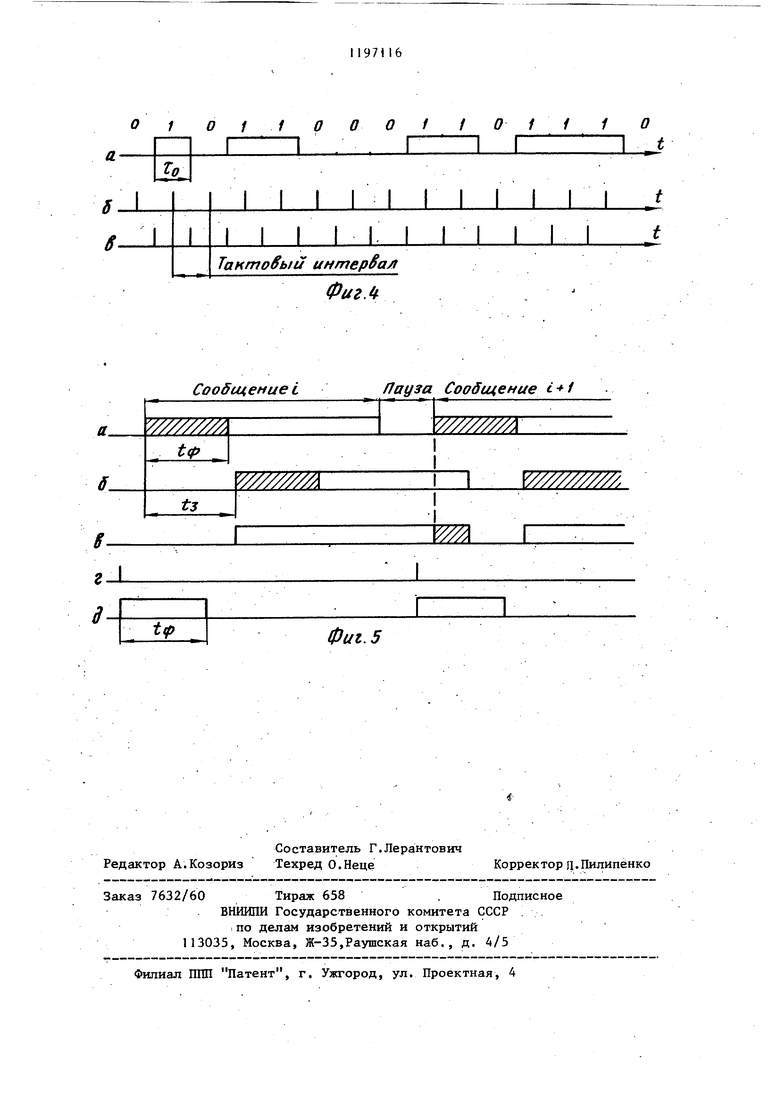

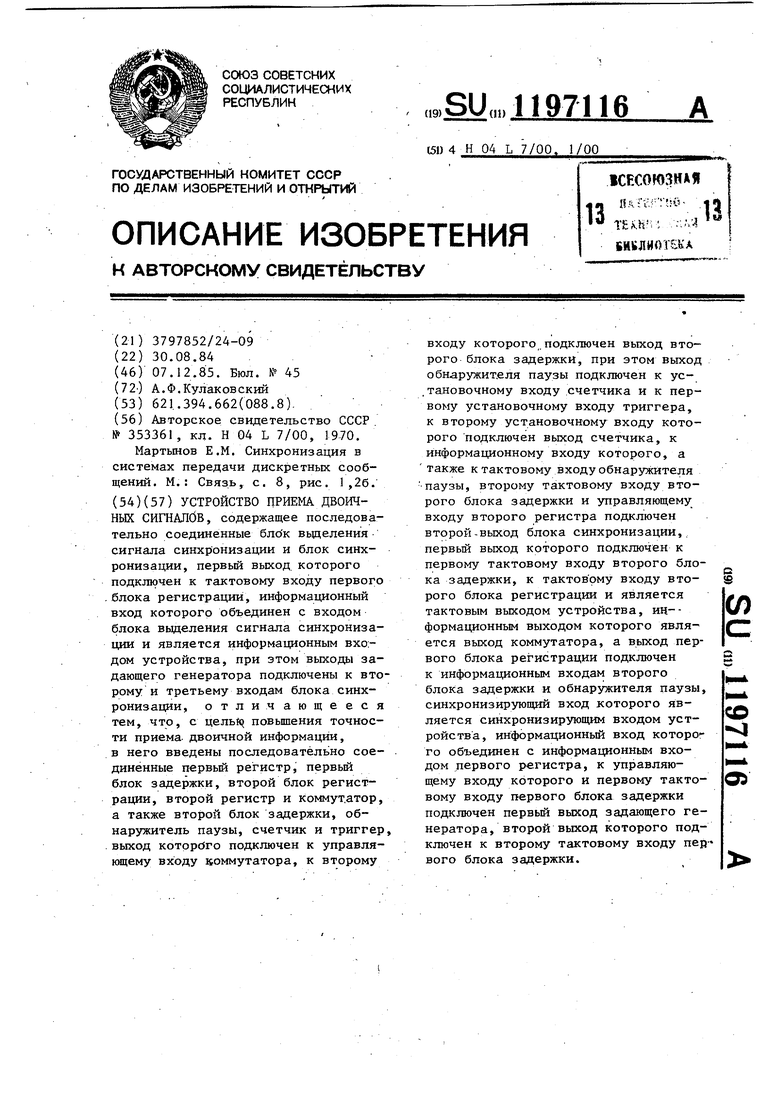

На фиг. 1 представлена структурная-схема устройства приема двоичны сигналов; на фиг. 2 - структурная схема блока задержки; на фиг. 3 структурная схема обнаружителя паузы ; на фиг. 4 и 5 - временные диаграммы, поясняющие работу предлагамого устройства.

Устройство приема двоичных сигналов содержит первый 1 и второй 2 регистры, первый 3 и второй 4 блоки задержки, первый 5 и второй 6 блоки регистрации, коммутатор 7, задающий генератор 8, блок 9 синхронизации, блок 10 выделения сигнала синхронизации, обнаружитель ,11 паузы, счетчик 12, триггер 13. Блоки 3 и 4 задержки содержат счетчик 14 адреса,элемент 15 памяти, регистр 16, обнаружитель 11 паузы содержит первый элемент И 17, первый элемент ИЛИ 18 регистр 19 сдвига, второй элемент И 20, суммирующий счетчик 21, пороговый элемент 22, элемент НЕ 23, третий элемент И 24, второй элемент 25, блок 26 управления. .

Устройство приема двоичных сигналов работает следующим, образом.

Принимаемые двоичные сигналы в виде последовательности единичных элементов 0,1 (фиг. 4а) поступают по информационному входу устройства на информационный в.ход первого регистра 1, первого блока 5 регистраци и блока 10 вьщеления сигналов синхронизации (на фиг. 4а двоичные сигналы приведены без искажений). Блок 10 вьзделения сигналов синхронизации формирует на своем выходе сигналы синхронизации в виде коротких импульсов , совпадающих по времени с фронта ми посылок (моментами измеиения значащих позиций, поступакйцие на первый (синхронизирующий) вход блока. 9 синхронизации. Задающий геиератор вырабатывает на своих первом и втором выходах периодические последовательности импульсов, сдвинутые один относительно другого на половину162периода повторения импульсов и

имеющие высокост.абильную частоту

где В - скорость манипуляции двоичных сигналов; m - целое число.

Блок 9 синхронизации формирует тактовые импульсы на своих первом и втором выходах, подстраивая их фазу путем добавления или исключения импульсов под управлением сигналов синхронизации из импульсных последовательностей задающего генератора В и последующего деления их частоты в m раз. При точном положении синхронизма тактовые импульсы на первом выходе блока 9 синхронизации-совпадают с центром (фиг. 4б), на втором вьрсоде - с границей (фиг. 4в) единичных элементов. .

Первый регистр 1 дискр.етизйрует принимаемые сигналы в моменты времени, задаваемые на его управляющем входе импульсами с первого выхода задающего генератора 8, и запоминает получаемые при этом выборки на время, равное периоду дискретизации. Выходной сигнал первого регистра 1 поступает на информационньй вход первого блока 3 задержки, которьй задерживает его на время , кратное длительности 7о единичного элемента И равное времени вхождения в фазу блока 9 синхронизации . Импульсы с выходов задающего генератора 8 управляют задержкой сигнала по первому и второму тактовым входам первого 3 блока задержки.

Первьй 5 и второй 6 блоки регистрации анализируют соответственно принимаемые и задержанные двоичные сигналы и в моменты времени, .задаваемые на их тактовых входах тактовыми импульсами с первого выхода 9 блока синхронизации, формируют решеИия о том, какие двоичные элементы были переданы: О или 1. Выходные сигналы, второго блока 6 регистрации запоминаются вторым регистром 2, который осуществляет также дополнительную задержку на время так как на его управляющий вход воздействуют так.товые импульсы с вто рого выхода блока 9 синхронизации (фиг. 4в), задержанные на это вре3мя .относительно регистрирующих тактовых импульсов с первого выхода последнего (фиг. 4б), Выходные сигналы первого блока 5 регистрации поступают на информационный вход второго блока задержки 4, который задерживает их на время под управлением тактовых импульсов, поступающих на первый и второй тактов,ые входы второго блока 4 задержки, с первого и второго выходов .бло ка 9 синхронизации. Двоичные сигналы с выхода второг регистра 2 и второго блока 4 задерж ки поступают соответственно на первьй и второй входы коммутатора 7. О сигнала имеют одинаковую задержку относительно принимаемых двоичных сигналов, но отличаются задержкой, в их регистрации. Диаграммы (фиг. 5) соответствуют случаю, кбгда длительность паузы меньше времени вхождения в фазу, со общения .начинаются с новой фазой единичных элементов. Так как первый блок 5 регистрации принимает реще- ния непосредственно по входньи сигналам, второй блок 6 регистрации позадержанным сигналам, а блок 9 синхронизации устанавливает точное положение синхронизма после вхождения в фазу на начальном участке сообщения, то регистрация с низкой до стоверностью первым блоком 5 регист рации имеет место в начале сообщения (заштрихованный участок на фиг. втдрым блоком 6 регистрации - в кон сообщения (заштрихованный участок на фиг. 5в). Пауза не содержит синхронизирующей информации, поэтому вы сокая достоверность регистрации задержанных сигналов вторым блоком 6 регистрации во время паузы на ий- формационном входе устройства подде живается требуемой стабильностью за дающих генераторов передающей и при емной сторон. . Обнаружитель 11 паузы анализирует двоичные сигналы поступающие на его информационный вход с вькода первого блока 5 регистрации и при о наружении паузы между сообщениями формирует на выходе обнаружителя 11 паузы импульс (Фиг. 5г) , которьгй устанавливает в нуль счетчик 12 и в еди-г ниЦу триггер 13.Единичное состояг ние триггера 13 (фиг. 5д управляет коммутатором 7 таким образом, что на информационный выход устройства 16 приема коммутируется участок сообщения с выхода второго блока 4 задержки (фиг. 56),характеризуемьй регистрацией двоичных сигналов с высокой достоверностью. Счетчик 12 суммирует тактовые импульсы, поступающие с второго выхода блока 9 синхронизации,и после отсчета интервала времени длительностью t формирует на своем выходе импульс, устанавливающий в нуль триггер 13. Нулевое состояние .триггера 13 (.фиг. 5д) коммутирует на информационный выход устройства участок сообщения с выхода первого регистра 2 (фиг. 5в), также характеризуемьй регистрацией двоичных сигналов с высокой достоверностью. Нулевое состояние триггера 13 подтверждается счетчиком 12 до тех пор, пока снова не будет- обнаружена пауза между сообщениями. Задержка сигналов а первом 3 и втором 4 блоках задержки происходит следующим образом, Двоичные сигналы с информационного входа блока 3, 4 задержки поступают на информационный вход элемен та 15 памяти. На первьй 3 и второй 4 тактовые входы блока задержки . пос.тупают распределенные во времени и пространстве импульсы. Импульсы с первого тактового входа суммируются счетчиком 14 адреса, кодовые выходы которого подключены к адресным входам элемента 15 памяти. После установления счетчиком 14 адреса очередного адреса, содержимое выбранной им ячейки памяти считывается на вход регистра 16. Следующий затем по/ второму тактовому входу импульс поступает на управляющий вход элемента 15 памяти, регистра 16 и записывает в первьш по тому же адресу сигнал с информационного входа, а во второй - считанный сигнал. Записанный в регистр 16 сигнал передается на выход блока 3,4 задержки. Адреса ячеек элемента 15 памяти периодически изменяются от О доК -1 в первом блоке 3 задержки и от О до -1 во втором блоке задержки, где . Поэтому каждьй записанньй с информационного входа сигнал в элементе 15 памяти передается на выход блока 3,4 задержки через N тактов и первом блоке 3 задержки и через - тактов во втором блоке 4 задержки, при этом время задержки пропорционально периоду по5вторения тактирующих импульсов на втором тактовом входе блока 3,4 задержки. Обнаружитель 11 паузы работает следующим образом. Двоичные сигналы с выхода первог блока 5 регистрации поступают на информационньй вход обнаружителя 11 паузы, сопровождающие их тактовые импульсы с второго выхода блока 9 синхронизации - на тактовый вход обнаружи-теля М паузы. Каждый тактовый импульс проходит через.второй элемент ИЛИ 25 на управляющий вход регистра 19 сдвига и сдвигает его содержимое на один бит вправо с одновременной записью сопровождаемого двоичного -сигнала, который проходит на. информационный вход регистра 19 йдвига через открытьй в это время третий элемент И 24 и первый элемент ИЛИ 18. В результате в каждом тактовом интервале ( интервал между соседними тактовыми импульсами) регистр 19 сдвига содержит выборочную комбинацию, образованную двоичньми сигналами, принятыми в данном и в предьщущих тактовьгх интервалах где N - число разрядов регистра 19 сдвига. Каждый тактовый импульс .с тактового входа обнаружителя 11 паузы инициирует блок 26 управления, который из синхроимпульсов, поступающих по синхронизирующему В.ХОДУ устройства, вырабатьшает в тактовом и тервале следующие управляющие сигн лы: на первом выходе блока 26 управления - команду рециркуляции СКРЦ) в виде сигнала логической 1 -на втором выходе - одиночный импульс; на третьем выходе - пачку и 16 импульсов, совпадающую по време-. и с КРЦ и следующую после одиночного импульса. КРЦ с второго выхода открывает первый элемент И 17 и, проходя через элемент НЕ 23., закрывает третий элемент И 24. Вследствие этого обнаружитель 11 паузы переводится в режим рециркуляции, в котором информационный вход обнаружителя 11 паузы запрещен, а выход регистра.19 сдвига соединен с его входом через первые элементы И 17 и ИЛИ 18.- Одиночный импульс с второго выхода блока 26 управления устанавливает в нуль суммирующий счетчик 21. Затем, пачка импульсов с третьего выхода блока 26 управления проходит через второй элемент ИЛИ 25 на управляющий вход регистра 19 сдвига и осуществляет циклический сдвиг (рециркуляцию) его содеряммого. Появляющиеся при этом биты выборочной комбинации на выходе регистра 19 сдвига стробируются импульсами той же пачки во втором эле-, менте И 20 и поступают на вход суммирующего счетчика 21. По окончании пачки выборочная комбинация займет прежнее положение в регистре 19 сдвига, а суммирующий счетчи|с 21 будет содержать число ее двоичных сигналов l..EdW это число превьшает пороговое число в пороговом элементе 22, то последний формирует сигнал обнаружения паузы, крторьй считьшается на выход обнаружителя 11 паузы, в момент дейртвия тактового импульса на стробируюЩем входе порогового элемента 22 с тактового входа обнаружителя Ii паузы (имеется в виду случай, когда пауза представлена двоичными сигналами 1).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема информации | 1983 |

|

SU1088051A1 |

| Обнаружитель комбинаций двоичных сигналов | 1986 |

|

SU1325724A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

| ОБНАРУЖИТЕЛЬ ПАУЗ РЕЧИ В СИСТЕМЕ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1992 |

|

RU2103826C1 |

| Обнаружитель комбинаций двоичных сигналов | 1988 |

|

SU1596492A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1413656A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Устройство для преобразования форматов слов двоичной последовательности | 1988 |

|

SU1513436A1 |

УСТРОЙСТВО ПРИЕМА ДВОИЧНЫХ СИГНАЛбВ, содержащее последовательно соединенные блок выделения сигнала синхронизации и блок синхронизации, первый выход, которого подключен к тактовому входу первого .блока регистрации, информационный вход которого объединен с входом блока выделения сигнала синхронизации и является информационным вхо:дом устройства, при этом выходы задающего генератора подключены к второму и третьему входам блока синхронизации, отличающееся тем, что, с целЫ9 повьппения точности приема, двоичной информации, в него введены последовательно соединенные первьш регистр, первьй блок задержки, второй блок регистрации, второй регистр и коммутатор, а также второй блок задержки, обнаружитель паузы, счетчик и триггер, . выход KOTppdro подключен к управляющему входу коммутатора, к второму входу которого подключен выход второго блока задержки, при этом выход обнаружителя паузы подключен к ус.тановочному входу счетчика и к первому установочному входу триггера, к второму установочному входу которого подключен выход счетчика, к информационному входу которого, а также к тактовому входу обнаружителя паузы, второму тактовому входу второго блока задержки и управляющему входу второго регистра подключен второй-выход блока синхронизации,, первый вькод которого подключен к первому тактовому входу второго блос S ка задержки, к тактоврму входу второго блока регистрации и является (Л тактовым выходом устройства, ин-формационным выходом которого является выход коммутатора, а выход первого блока регистрации подключен к информационным входам второго блока задержки и обнаружителя паузы, синхронизирующий вход которого яв ляется синхронизирующим входом устройства, информационный вход которого объединен с информационным входом первого регистра, к управляюОд щему входу которого и первому тактовому входу первого блока задержки подключен первьй выход задающего генератора, второй выход которого подключен к второму тактовому входу первого блока задержки.

фиг. г

фиг 3

Фиг л

Сообщение L

Пауза Сообщение

| Авторское свидетельство СССР | |||

| УСТРОЙСТВО для СИНХРОНИЗАЦИИ ДИСКРЕТНЫХ СИГНАЛОВ в СИСТЕМАХ ПРЕРЫВИСТОЙ СВЯЗИ | 0 |

|

SU353361A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Мартьиов Е.М | |||

| Синхронизация в системах передачи дискретных сообщений | |||

| М.: Связь, с | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-12-07—Публикация

1984-08-20—Подача