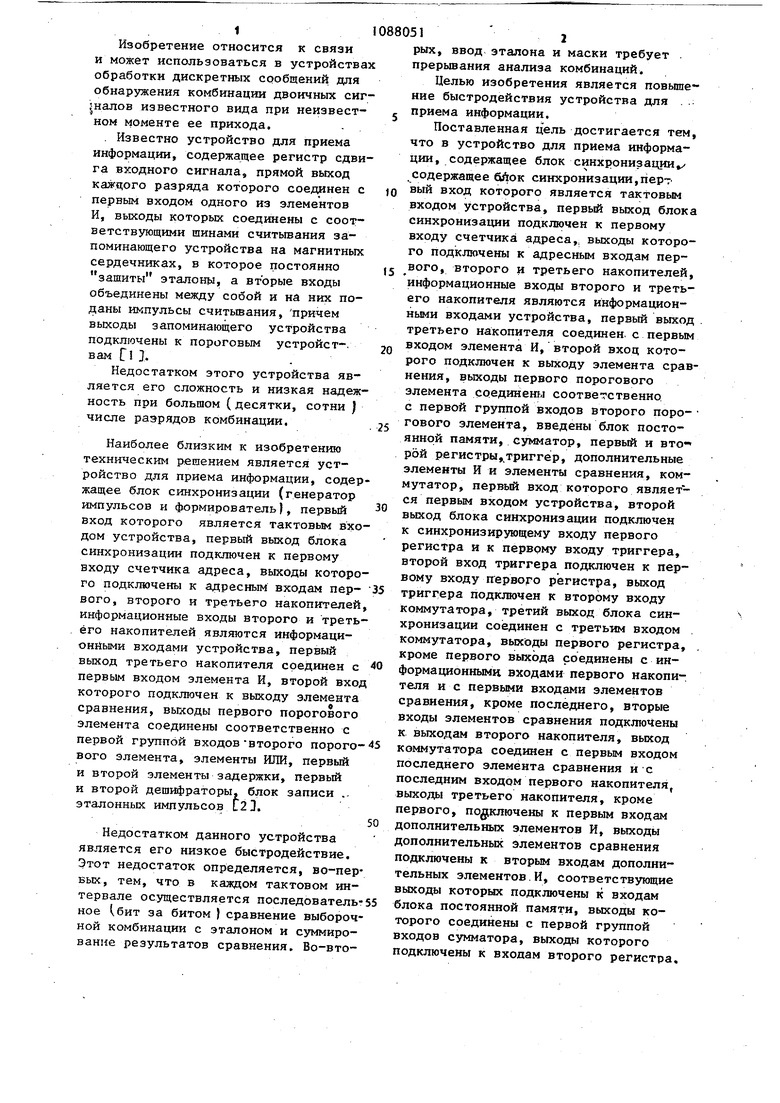

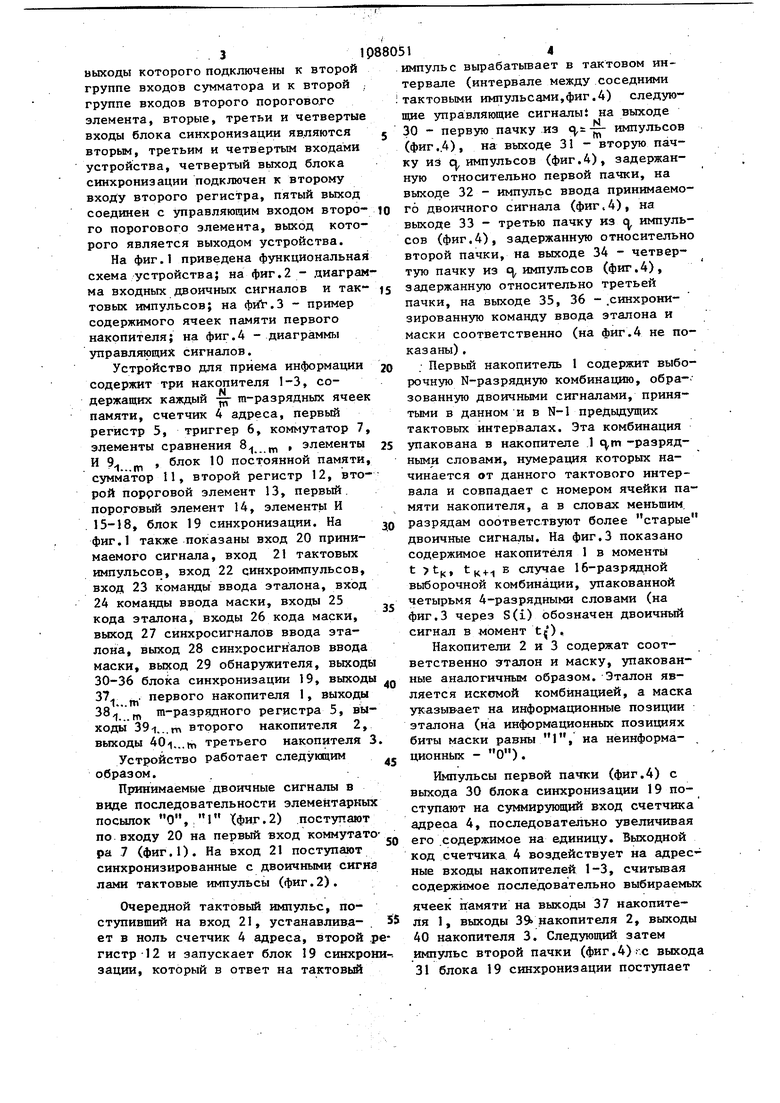

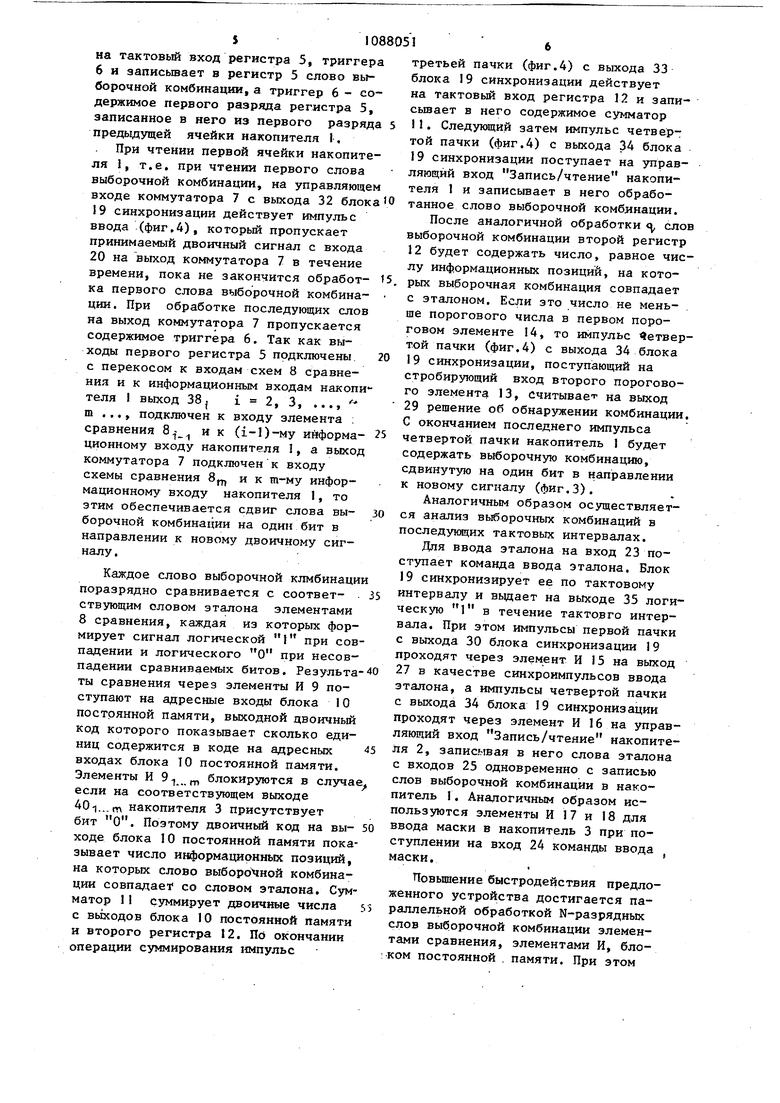

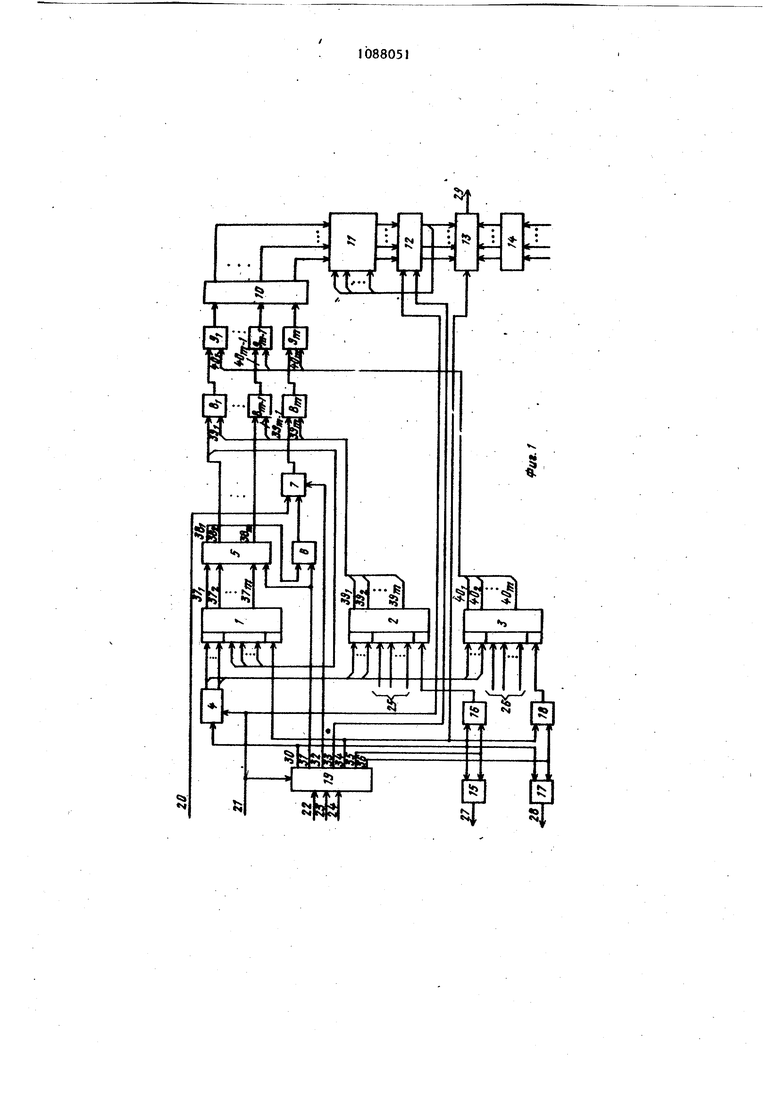

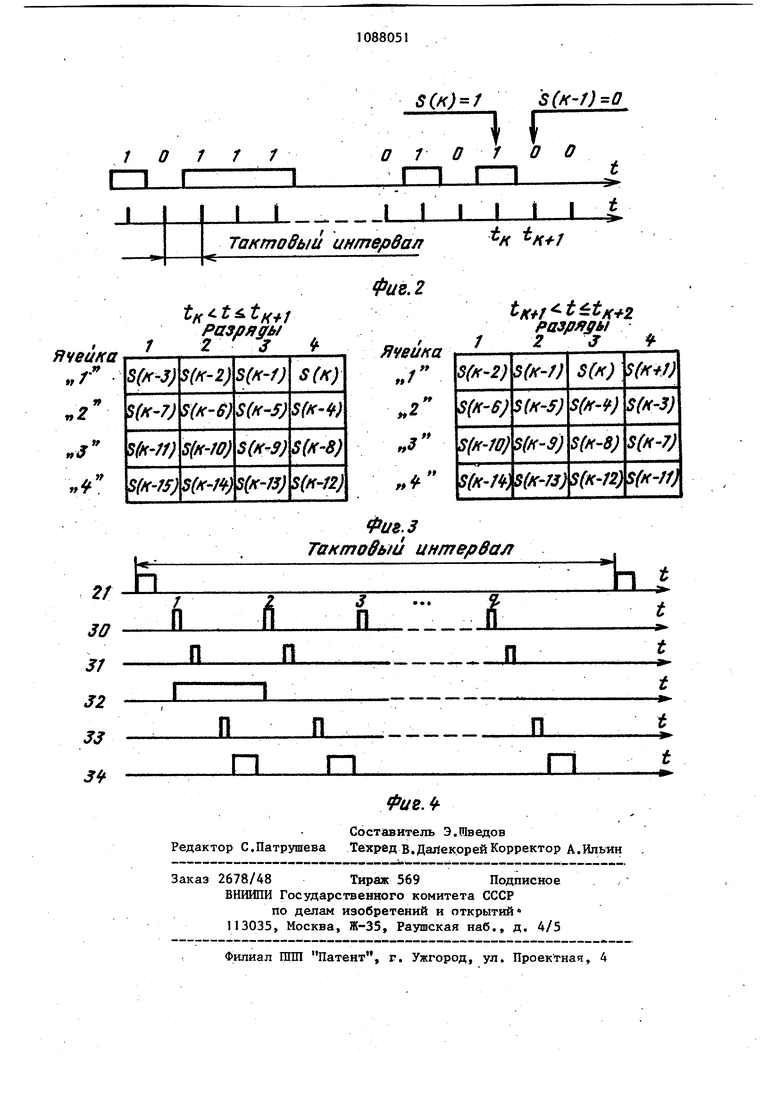

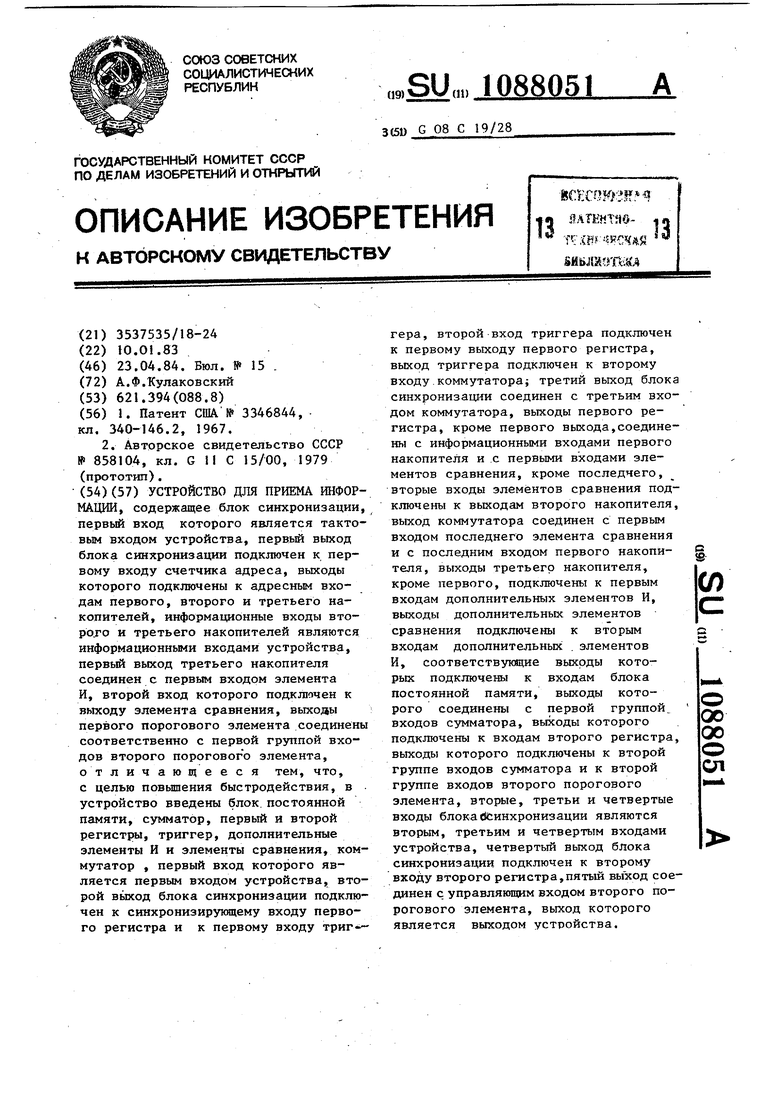

Изобретение относится к связи и может использоваться в устройствах обработки дискретных сообщений для обнаружения комбинации двоичных сиг,налов известного вида при неизвестном моменте ее прихода. . Известно устройство для приема информации, содержащее регистр сдвига входного сигнала, прямой выход каждого разряда которого соединен с первым входом одного из элементов И, выходы которых соединены с соответствующими шинами считьгоания запоминающего устройства на магнитных сердечниках, в которое постоянно зашиты эталоны, а вторые входы объединены между собой и на них поданы импульсы считывания, причем выходы запоминающего устройства подключены к пороговым устройст-. вам Cl J.. Недостатком этого устройства является его сложность и низкая надежность при большом (десятки, сотни ) числе разрядов комбинации. Наиболее близким к изобретению техническим решением является устройство для приема информации, содер жащее блок синхронизации (генератор импульсов и формирователь), первьй вход которого является тактовьм вхо дом устройства, первый выход блока синхронизации подключен к первому входу счетчика адреса, выходы которо го подключены к адресным входам первого, второго и третьего накопителей информационные входы второго и треть его накопителей являются информационными входами устройства, первый выход третьего накопителя соединен с первым входом элемента И, второй вхо которого подключен к выходу элемента сравнения, выходы первого порогового элемента соединены соответственно с первой группой входоввторого порого вого элемента, элементы ИЛИ, первый и второй элементы задержки, первый и второй дешифраторы, блок записи .эталонных импульсов 12D, . Недостатком данного устройства является его низкое быстродействие. Этот недостаток определяется, во-пер вых, тем, что в каждом тактовом интервале осуществляется последователь кое (бит за битом ) сравнение выбороч ной комбинации с эталоном и суммирование результатов сравнения. Во-вто512рых, ввод эталона и маски требует прерывания анализа комбинаций. Целью изобретения является повьше кие быстродействия устройства для . . приема информации. Поставленная цель достигается тем, что в устройство для приема информации, содержащее блок синхронизации х содержащее бйок синхронизации,перТ вый вход которого является тактовым входом устройства, первый выход блока синхронизации подключен к первому входу счетчика адреса,, выходы которого подключены к адресным входам первого, второго и третьего накопителей, информационные входы второго и третьего накопителя являются информационными входами устройства, первый выход . третьего накопителя соединен с первым входом элемента И, второй вход которого подключен к выходу элемента сравнения, выходы первого порогового элемента соединены соответственно с первой группой входов второго поро- гового элемента, введены блок постоянной памяти, сумматор, первый и вто- рой регистры,.триггер, дополнительные элементы И и элементы сравнения, коммутатор, первый вход:которого является первым входом устройства, второй выход блока синхронизации подключен к синхронизирующему входу первого регистра и к первому входу триггера, второй вход триггера подключен к первому входу первого регистра, выход триггера подключен к второму входу коммутатора, третий выход блока синхронизации соединен с третьим входом коммутатора, выходы первого регистра, . кроме первого выхода соединены с информационными входами первого накопителя и с первыми входами элементов сравнения, кроме последнего, вторые входы элементов сравнения подключены к выходам второго накопителя, выход коммутатора соединен с первым входом последнего элемента сравнения и с последним входом первого накопителя выходы третьего накопителя, кроме первого, подключены к первым входам дополнительных элементов И, выходы дополнительных элементов сравнения подключены к вторым входам дополнительных элементов.И, соответствующие выходы которых подключены к входам блока постоянной памяти, выходы которого соединены с первой группой входов сумматора, выходы которого подключены к входам второго регистра. выходы которого подключены к второй группе входов сумматора и к второй группе входов второго порогового элемента, вторые, третьи и четвертые входы блока синхронизации являются вторым, третьим и четвертым входами устройства, четвертый выход блока синхронизации подключен к второму входу второго регистра, пятый выход соединен с управляющим входом второго порогового элемента, выход которого является выходом устройства. На фиг.1 приведена функциональная схема устройства; на фиг,2 - диаграм ма входных двоичных сигналов и тактовых импульсов; на фиТг.З - пример содержимого ячеек памяти первого накопителя; на фиг.4 - диаграммы управляющих сигналов. Устройство для приема информации содержит три накопителя 1-3, содержащих каждый - т-разрядных ячеек памяти, счетчик 4 адреса, первый регистр 5, триггер 6, коммутатор 7, элементы сравнения 8 , элементы , блок 10 постоянной памяти. сумматор 11, второй регистр 12, второй поррговой элемент 13, первый, пороговый элемент 14, элементы И 15-18, блок 19 синхронизации. На фиг. также показаны вход 20 принимаемого сигнала, вход 21 тактовых импульсов, вход 22 синхроимпульсов, вход 23 команды ввода эталона, вход 24 команды ввода маски, входы 25 кода эталона, входы 26 кода маски, выход 27 синхросигналов ввода эталона, выход 28 синхросигналов ввода маски, вькод 29 обнаружителя, выходы 30-36 блока синхронизации 19, выходы 37-1 .., первого накопителя 1, выходы U,. m; т-разрядного регистра 5, выходы 39-t...rT второго накопителя 2, выходы 40-1,..j третьего накопителя 3 Устройство работает следующим образом. Принимаемые двоичные сигналы в виде последовательности элементарных посылок 0,,1 ХФИГ.2) поступают по входу 20 на первый вход коммутато ра 7 (фиг.1). На вход 21 поступают синхронизированные с двоичными сигяа лами тактовые импульсы (фиг.2). Очередной тактовый импульс, поступивший на вход 21, устанавливает в ноль счетчик 4 адреса, второй .р гистр 12 и запускает блок 19 синкрон зации, который в ответ на тактовый импульс вырабатьгеает в тактовом интервале (интервале между соседними тактовыми импульсами,фиг.4) следующие управляющие сигналыJ на выходе 30 - первую пачку из q,-- импульсов (фиг.4), на выходе 31 - вторую пачку из (импульсов (фиг.4), задержанную относительно первой пачки, на выходе 32 - импульс ввода принимаемого двоичного сигнала (фиг.4), на выходе 33 - третью пачку из с импульсов (фиг.4), задержанную относительно второй пачки, на выходе 34 - четвертую пачку из t импульсов (фиг.4), задержанн5 ю относительно третьей пачки, на выходе 35, 36 - .синхронизированную команду ввода эталона и маски соответственно (на фиг.4 не показаны) . Первьй накопитель 1 содержит выборочную N-разрядную комбинацию, обра- зованную двоичными сигналами, принятыми в данном и в N-1 предыдущих тактовых интервалах. Эта комбинация упакована в накопителе 1 -разрядными словами, нумерация которых начинается от данного тактового интервала и совпадает с номером ячейки памяти накопителя, а в словах меньшим, разрядам соответствуют более старые двоичные сигналы. На фиг.З показано содержимое накопителя 1 в моменты в слзгчае 16-разрядной выборочной комбинации, упакованной четырьмя 4-разрядными словами (на фиг.З через S(i) обозначен двоичный сигнал в момент t). Накопители 2 и 3 содержат соответственно эталон и маску, упакованные аналогичным образом,-Эталон является искомой комбинацией, а маска указыв-ает на информационные позиции эталона (на информационных позициях биты маски равны 1, иа неинформационных - О). Импульсы первой пачки (фиг,4) с выхода 30 блока синхронизации 19 поступают на суммирзтощий вход счетчика адреса 4, последовательно увеличивая его .содержимое на единицу. Выходной код счетчика 4 воздействует на адресные входы накопителе й 1-3, считывая содержимое последовательно выбираемых ячеек памяти на выходы 37 накопителя 1, выходы 39 накопителя 2, выходы 40 накопителя 3. Следующий затем импульс второй пачки (фиг.4)с выхода 31 блока 19 синхронизации поступает на тактовый вход регистра 5, триггера 6 и записьюает в регистр 5 слово выборочной комбинации, а триггер 6 - содержимое первого разряда регистра 5, записанное в него из первого разряда 5 предьщущей ячейки накопителя I. При чтении первой ячейки накопителя 1, т.е. при чтении первого слова выборочной комбинации, иа управляющем входе коммутатора 7 с выхода 32 блокаО 19синхронизации действует импульс ввода (фиг.4), который пропускает принимаемый двоичный сигнал с входа 20на выход коммутатора 7 в течение времени, пока не закончится обработка первого слова выборочной комбинации. При обработке последующих слов на выход коммутатора 7 пропускается содержимое триггера 6. Так как выходы первого регистра 5 подключены с перекосом к входам схем 8 сравнения и к информационным входам накопи теля I выход 38j i 2, 3, ..., m ..., подключен к входу злемента ; сравнения 8| и к (1-1)-му ийформационному входу накопителя I, а выход коммутатора 7 подключен к входу схемы сравнения 8 и к тп-му информационному входу накопителя 1, то зтим обеспечивается сдвиг слова выборочной комбинации на один бит в направлении к новому двоичному сигналу. Каждое слово выборочной клмбинаци поразрядно сравнивается с соответствующим словом эталона элементами 8 сравнения, каждая из которых формирует сигнал логической I при сов падении и логического О при несовпадении сравниваемых битов. Результа ты сравнения через элементы И 9 поступают на адресные входы блока 10 постоянной памяти, выходной двоичный код которого показьгаает сколько единиц содержится в коде на адресных входах блока ТО постоянной памяти. Элементы И 9 г„ блокируются в случа если на соответствующем выходе 40-1...гг накопителя 3 присутствует бит О. Поэтому двоичный код на выходе блока 10 постоянной памяти пока зывает число информационных позиций, на которых слово выборочной комбинации совпадает со словом эталона. Сум матор 11 суммирует двоичные числа с вьЬсодов блока 10 постоянной памяти и второго регистра 12. Пс окончании операции суммирования импульс 10880 6 третьей пачки (фиг.4) с выхода 33 блока 19 синхронизации действует на тактовый вход регистра 12 и записьшает в него содержимое сумматор 11. Следующий затем импульс четвертой пачки (фиг.4) с выхода 34 блока 19 синхронизации поступает на управляющий вход Запись/чтение накопителя 1 и записывает в него обработанное слово выборочной комбинации. После аналогичной обработки , слов выборочной комбинации второй регистр 12 будет содержать число, равное числу информационных позиций, на которых выборочная комбинация совпадает с зталоном. Если зто число не мень- . ше порогового числа в первом пороговом элементе 14, то импульс Четвертой пачки (фиг.4) с выхода 34 блока 19 синхронизации, поступающий на стробирующий вход второго порогового злемента 13, считывает на выход 29 решение об обнаружении комбинации. С окончанием последнего импульса четвертой пачки накопитель 1 будет содержать выборочную комбинацию, сдвинутую на один бит в направлении к новому сигналу (фиг.З). Аналогичньпу образом осуществляется анализ выборочных комбинаций в последунидих тактовых интервалах. Для ввода эталона на вход 23 поступает команда ввода эталона. Блок 19 синхронизирует ее по тактовому интервалу и вьодает на выходе 35 логическую 1 в течение тактовго интервала. При этом импульсы первой пачки с выхода 30 блока синхронизации 19 проходят через элемент И 15 на выход 27 в качестве синхроимпульсов ввода эталона, а импульсы четвертой пачки с выхода 34 блока 19 синхронизации проходят через элемент И 16 на управляющий вход Запись/чтение накопителя 2, записрлшая в него слова эталона с входов 25 одновременно с записью слов выборочной комбинации в накопитель I. Аналогичным образом используются элементы И 17 и 18 для ввода маски в накопитель 3 при поступлении на вход 24 команды ввода маски. Повьшение быстродействия предложенного устройства достигается параллельной обработкой N-разрядных слов выборочной комбинации элементами сравнения, элементами И, блоком постоянной . памяти. При этом

710880518

в тактовом интервале требуется cj,предложенное устройство выигрывает

шагов,на каждом из которых осущест- .в быстродействии по сравнению с пррвляется сравнение, маскирование и под-тотипом примерно в-Щ-раз, так как

счет количества единиц, в то времянакопитель в предпожеином устройстве

как в известном устройстве требует- 5не каждом шаге осзпцествляет цикл

ся т, таких шагов. Если накопителисчитывания и цикл записи, а

являются наиболее медленно действую-в прототипе - только цикл счищими элементами в устройстве, тотывания.

5( s(Ki)Q

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1984 |

|

SU1156110A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1413656A1 |

| Устройство классификации N-разрядных двоичных комбинаций | 1982 |

|

SU1089576A1 |

| Обнаружитель комбинации двоичных сигналов | 1983 |

|

SU1270898A1 |

| Выделитель составной комбинации двоичных сигналов | 1984 |

|

SU1223411A1 |

| Логическое запоминающее устройство | 1983 |

|

SU1140172A1 |

| Устройство приема двоичных сигналов | 1984 |

|

SU1197116A1 |

| Логическое запоминающее устройтво | 1979 |

|

SU858104A1 |

УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ, содержащее блок синхронизации, первый вход которого является тактовым входом устройства, первый выход блока синхронизации подключен к первому входу счетчика адреса, выходы которого подключены к адресным входам первого, второго и третьего накопителей, информационные входы второго и третьего накопителей являются информационными входами устройства, первый выход третьего накопителя соединен с первым входом элемента И, второй вход которого подключен к выходу элемента сравнения, выходы первого порогового элемента соединены соответственно с первой группой входов второго порогового элемента, отличающееся тем, что, с целью повышения быстродействия, в устройство введены блок постоянной памяти, сумматор, первый и второй регистры, триггер, дополнительные элементы И и элементы сравнения, коммутатор , первый вход которого является первым входом устройства, второй выход блока синхронизации подключен к синхронизирукяцему входу первого регистра и к первому входу триггера, второй вход триггера подключен к первому выходу первого регистра, выход триггера подключен к второму входу.коммутатора; третий выход блока синхронизации соединен с третьим входом коммутатора, выходы первого регистра, кроме первого выхода,соединены с информационными входами первого накопителя и .с первыми входами элементов сравнения, кроме последнего, вторые входы элементов сравнения подключены к выходам второго накопителя, выход коммутатора соединен с первым входом последнего элемента сравнения i и с последним входом первого накопителя, выходы третьего накопителя, (Л кроме первого, подключены к первым входам дополнительных элементов И, выходы дополнительных элементов сравнения подключены к вторым входам дополнительных . элементов И, соответствукяцие выходы которых подключены к входам блока постоянной памяти, выходы которого соединены с первой группой, оо входов сумматора, выходы которого 00 подключены к входам второго регистра, о ел выходы которого подключены к второй группе входов сумматора и к второй группе входов второго порогового элемента, вторые, третьи и четвертые входы блокабсинхронизации являются вторым, третьим и четвертым входами устройства, четвертый выход блока синхронизации подключен к второму входу второго регистра,пятый выход соединен с управляющим входом второго порогового элемента, выход которого является выходом устройства.

П

«

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США | |||

| 3346844, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Логическое запоминающее устройтво | 1979 |

|

SU858104A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1984-04-23—Публикация

1983-01-10—Подача