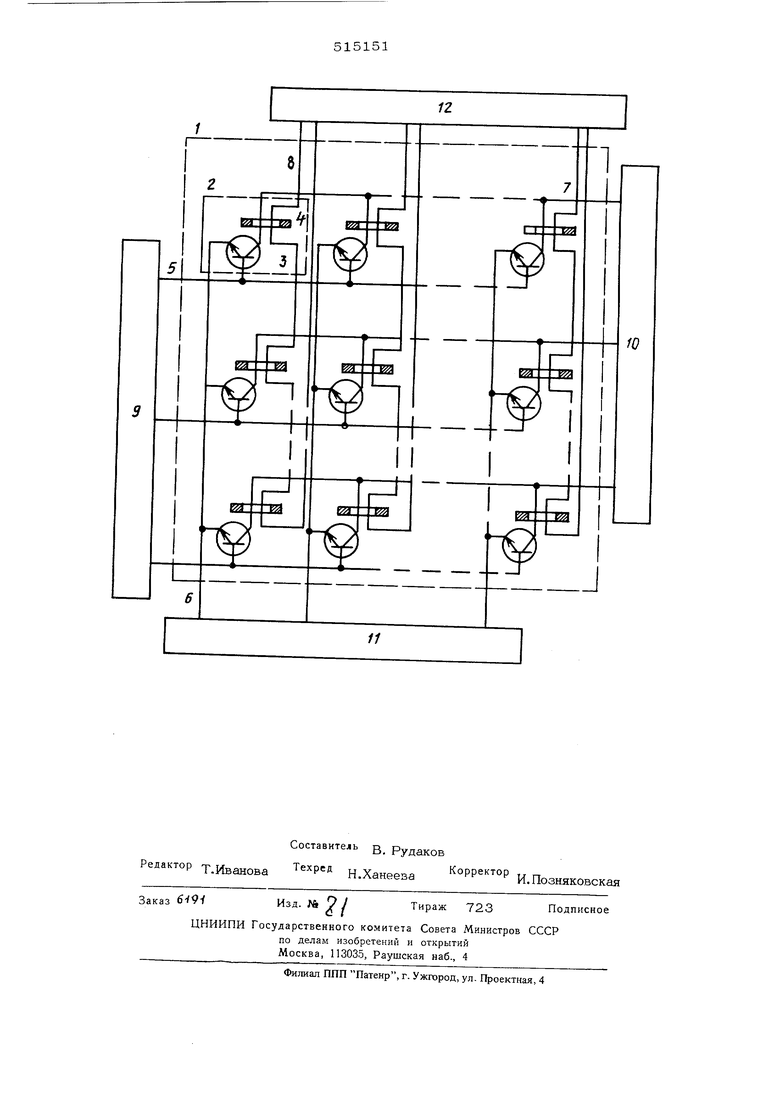

Известно запоминающее устройство, содержащее накопитель, собранный на транзис торах и ферритовых сердечниках, прощитых выходными шинами, подключенными к усилителям считывания, числовыми шинами счи тывания, одни концы котсрых соединены с коллекторами соответствующих транзисторов, к эммитерам которых подключены разрядные шины, а к базам - числовые шины записи - считывания, соединенные с одним из дешифраторов адреса. Недостатком известного устройства явля ется большое количество шин, прощивающих сердечники. В предлагаемом устройстве другие концы числовых щин считывания подключены к выходам другого дешифратора адреса. Такое конструктивное рещение обеспечивает работу транзистора запоминающего элемента при считывании в прям см режиме а при записи - в инвертном. Это позволяет сократить число шин, прошивающих каждый ферритовый сердечник устройства, до двух. На чертеже представлена электрическая схема накопителя предлагаемого устройства вместе с блоком электронного обрамления. Запоминающее устройство содержит накопитель 1 с запоминающими элементами 2, содержащими транзистор 3 и ферритовый сердечник 4 с прямоугольной петлей гистерезиса:, числовые шины записи-считывания 5, которые подключены к базам транзисторов 3:, разрядные щины 6, к которым подключены эммитеры транзисторов 3; числовые шины считывания 7, одни концы которых подключены к выводам коллекторов транзисторов 3, которые, в свою очередь, прошивают ферритовые сердечники 4; выходные шины 8, прошивающие ферритовые сердечники 4; первый дешифратор адреса 9, подключенный к числовым шинам записи - считывания 5; второй дешифратор адреса 10, подключенный к другим конпам числовых шин считывания 7; блок 11 разрядных формирователей, подключенный к разрядным шинам р:, усилители считывания 12, подключенные к выходным щинам 8. Устройство может работать в одном из двух режимов: считывание или запись нуля или единицы. При работе устройства в режиме считывание на выходе первого дешифратора адреса 9, соответствующего выбранному для считывания числу, появляется импульс напряжения, подаваемый в соответствующую числовую шину записи-счи тывания 5, на выходе второго дешифратора адреса 10, соответствующего тому же числу, появляется импульс напряжения, подаваемый в соответствующую числовую шину считывания 7. На всех выходах блока 11, разрядньгх формирователей , подключенных к разрядным шинам 6, установлен нулевой уровень напряжения. Тем самым обеспечива ется протекание токов считывания через запоминающие элементы 2 выбранного числа, причем транзисторы этих запоминающих элементов работают в прямом режиме. Сигналы считанных единиц, наведенные в выход ных шинах 8, поступают в усилители считывания 12. На прочих выходах первого и вто рого дешифраторов адреса 9 и 10 сохраняет ся нулевой уровень напряжения, и токи считывания в шинах остальных чисел не проте- При работе в режиме запись на выходе первого дешифратора адреса 9, соответст вующего выбранному числу, появляется импульс напряжения, подаваемый в соответствующую числовую шину записи-считывания 5. На остальных выходах дешифратора 9 сохраняется нулевой уровень. На всех выходах второго дешифратора адреса присутствует нулевой уровень. В это же время на выходах блока 11 разрядных формирователей тех разрядов, в которые должна быть записана единица, появляются импульсы напряжения, которые подаются по разрядным шинам 6 на эмиттеры транзисторов 3. Тем са мым обеспечивается протекание разрядных токов записи, обратных токам считывания для каждого запоминающего элемента 2, Транзисторы запоминающих элементов выбранного числа при этом работают в инверсном режиме. На выходах усилителей с тех разрядов, в которые должен быть записан нуль, сохраняется нулевой уровень напряжения. Формула изобретения Запоминающее устройство, содержащее накопитель, выполненный на транзисторах и ферритовых сердечниках, прошитых выходными шинами, подключенными к усилителям считывания, числовыми шинами считывания, одни концы которых соединены с коллекторами соответствующих транзисторов, к эмиттерам которых подключены разрядные шины, а к базам - числовые шины записи-считывания, соединенные с одним из дещифраторсе адреса, отличающееся тем, что, с целью упрощения устройства, другие концы числовых шин считывания подключены к выходам другого дешифратора адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1978 |

|

SU750562A1 |

| Магнитное оперативное запоминающее устройство | 1983 |

|

SU1129654A1 |

| Оперативное запоминающее устройство типа @ с обнаружением и исправлением ошибок | 1981 |

|

SU999114A1 |

| Управляющий автомат цифрового устройства числового управления | 1972 |

|

SU507153A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОСЙ1Ч '^ | 1972 |

|

SU436389A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU280547A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| АССОЦИАТИВНО-АДРЕСНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU336697A1 |

| Устройство записи и считывания информации для динамического накопителя на однотранзисторных запоминающих элементах | 1976 |

|

SU727023A1 |

Авторы

Даты

1976-05-25—Публикация

1975-01-15—Подача