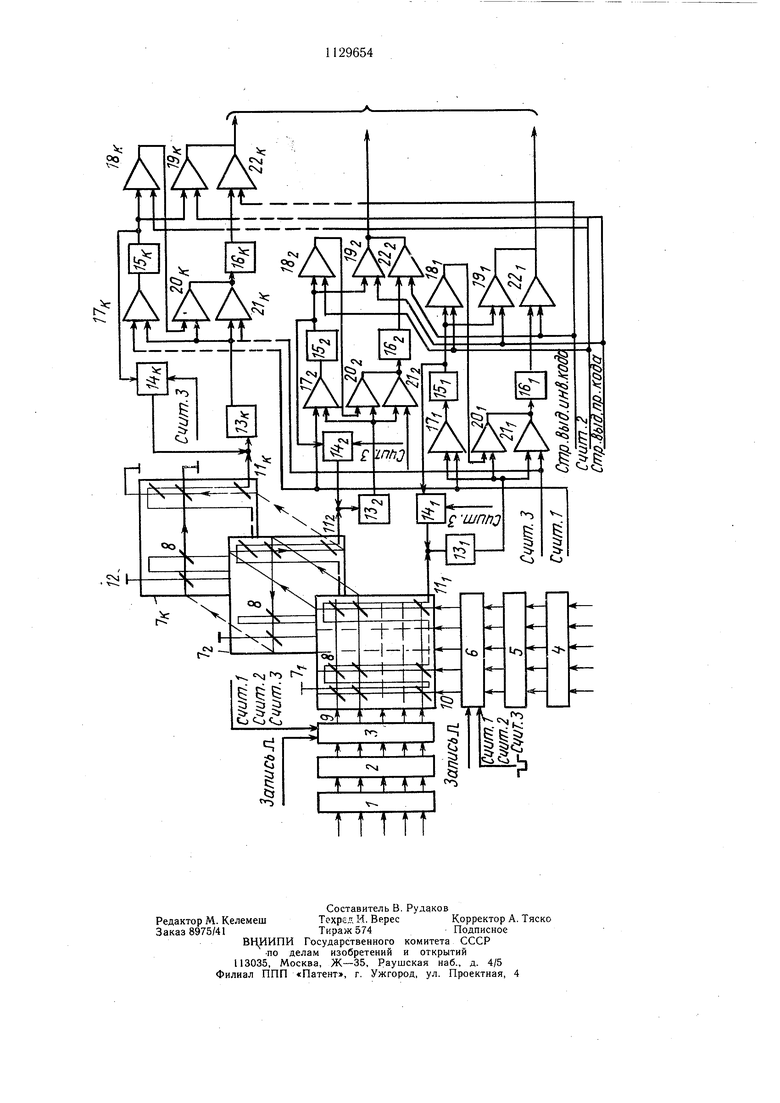

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, |{ может быть применено при созданш надежных систем обработки данных. Известно запоминающее устройство, содержащее накопитель, подключенный к блокам считывания и записи 1. Однако отсутствие в коде выбранного информационного слова информации о работоспособности внутренних элементов запоминающего устройства приводит к невозможности определения без значительных дополнительных аппаратурных затрат достоверности выдаваемой из запоминающего устройства информации. Наиболее близким к изобретению является магнитное оперативное запоминающее устройство матричного типа, содержащее регистры адреса X и Y и усилители-формирователи X и Y к соответствующим адресным щинам ферритовой матрицы, обмотки считывания которой подключены через вентили запрета и через усилители считывания - к регистру кода числа 2. В данном устройстве код адреса считываемого слова подается на дещифраторы X и Y, с выходов которых по сигналу «Считывание усиленные сигналы поступают на считывание записанного информационного слова. Записанное слово воспроизводится путем перемагничивания выбранных сердечников и запоминается на регистре кода числа, как результат прямого чтения информационного слова 2. Однако отсутствие в коде выбранного слова информации о работоспособности внутренних элементов указанного запоминающего устройства снижает его надежность.. Цель изобретения - повыщение надежности устройства за счет получения дополнительной информации о состоянии элементов запоминающего устройства. Поставленная цель достигается тем, что в магнитное оперативное запоминающее устроиство, содержащее последовательно соединенные первый регистр адреса, первый дещифратор адреса и формирователи сигналов первой группы, последовательно соединенные второй регистр адреса, второй дещифратор адреса и формирователи сигналов второй группы, накопитель, состоящий из запоминающих матриц на ферритовых сердечниках, прощитых адресными обмотками и обмотками считывания, одни концы которых подключены к щине нулевого потенциала, другие соответственно - к выходам формирователей сигналов групп и к входам усилителей считывания, триггеры, выходы которых подключены к одним из входов элементов И, введены дополнительные триггеры и группы элементов И, причем вход каждого триггера подключен к выходу первого элемента И одноименной группы, а выход - к первым входам второго и третьего элементов И одноименной группы, вход каждого дополнительного триггера соединен с выходами четвертого и пятого элементов И одноименной группы, а выход - с первым входом щестого элемента И одноименной группы, первые входы первого, четвертого и пятого элементов И каждой группы подключены к выходу соответствующего усилителя считывания, выход каждого второго элемента И группы соединен с вторым входом четвертого элемента И одноименной группы, вторые входы первых, вторых, третьих, пятых и щестых элементов И групп являются соответственно управляющими входами устройства, с первого по ,пятый, выходы третьего и щестого элементов И групп являются информационными выходами устройства. На чертеже изображена функциональная схема магнитного оперативного запоминающего устройства, например k-разрядного (где k ;Я, целое). Устройство содерх ит первые регистр 1 адреса и дещифратор 2 адреса и первую группу формирователей 3 сигналов, относящиеся к координате X устройства, вторые регистр 4 адреса и дещифратор 5 адреса и вторую группу формирователей 6 сигналов, накопитель, состоящий из запоминающих матриц 7i-7к на ферритовых сердечниках 8, прощитых адресными обмотками 9 и 10 и обмотками 11 (-11к считывания, одни концы которых подключены к щине 12 нулево-, го потенциала, а другие соответственно - к выходам формирователей 3 и 6 и к входам усилителей 13i-13к считывания. Устройство также содержит элементы И 14к, триггеры 15t-15к, образующие регистр прямого кода, дополнительные триггеры 16 16к, образующие регистр инверсного кода, и группы элементов И, каждая из которых состоит из элементов И с первого по щестой (например, элементы И 17i-221 с первого по щестой k-я группа - элементы И 17к- 22к с первого по щестой). Устройство работает следующим образом. Предположим, что по первому адресу в матрицах 7i-7к хранится информационное слово, записываемое кодом «10...1 соответственно, код адреса числа записывается в регистрах 1 и 4 с дальнейщей его подачей на дещифраторы 2 и 5. На одном из выходов каждого дещифратора возникает сигнал, который формируется формирователями 3 и 6 и при поступлении сигнала «Считывание 1 направляется по соответствующим адресным обмоткам 9 и 10. Для нащего случая, чтобы произвести считывание информационного слова с первого адреса матриц 7, -7, усиленные и сформированные сигналы поступают на первые адресные обмотки 9 и 10. Сердечники, находящиеся на пересечении возбужденных обмоток 9 и 10 и в которых был записан код «1 (что соответствует нахождению сердечника в состоянии « + В), перемагничиваются в состояние «-В. При этом в обмотках 11( - UK считывания формируются сигналы, которые усиливаются соответственно усилителями 13i-13к и через элементы И 14 i- 14к подаются на запись. «1 в триггеры 151- 15к, в которых хранится прямой код слова. Так как выбранный сердечник матрицы второго разряда находится в состоянии «-В, то на выходе обмотки 11 гсчитывания сигнал не формируется в триггер 15 ги остается пребывать в состоянии «О. Таким образом, по сигналу «Считывание 1 на регистре прямого кода хранится код выбранного слова «10...1, который выдается на выход путем подачи сигнала «Строб выдачи прямого кода информационного слова элементов И 19 - 19к. После прохождения сигнала «Считывание 1 происходит формирование на регистре инверсного кода записанного информационного слова, для чего подается сигнал «Счи тывание 2 одновременно на формирователи 3 и 6, а также на одни входы элементов И , на другие входы которых поступают сигналы соответственно с триггеров 15i-15к. Сформированный сигнал «1 на выходе элементов И 18 i и 18к подается соответственно на одни входы элементов И 20 t и 20к, на другие входы которых подаются с усилителей 13 i и 13к сигналы результата опроса состояния «-В выбранных сердечников матриц первого и k-ro разрядов. При нормально работающем запоминающем устройстве единичные сигналы с выходов элементов И 18 i и 18 к не поступают через элементы И 20 t и 20к на входы триггеров 161 и 6к, которые вследствие этого не изменяют своего «нулевого состояния. Таким образом, формируются «нули инверсного кода информационного слова, подтверждая превыбание сердечников, перешедших по сигналу «Считывание 1 из состояния « + В в состояние «-В. Для нашего случая после этапа «Формирование нулей инверсного кода на регистре инверсного кода будет храниться код «00...О После выполнения этапа «Формирование нулей инверсного кода информационного слова осуществляется формирование его «единиц и восстановление считанного информационного слова. Для этого на формирователи 3 и 6 подается сигнал «Запись, по которому вь1бранные сердечники матриц первого, второго и k-ro разрядов переводятся из состояния «-В4 в состояние «-I-В/. Затем подается сигнал «Считывание 3 на формирователи 3 и 6 на одни входы элементов И 14ь 14 2 и 14к, на другие входы которых заводятся соответственно сигналы с единичных выходов триггеров 15i, 15 2 и 15к. Наличие единичных сигналов с выходов триггеров 151 и 15к: на входах элементов 14 1 и 14 к позволяют осуществлять соответственно формирование импульса запрета считывания выбранных сердечников матриц первого и k-ro разрядов по обмоткам считывания 111 и 11к через элементы И 141 и 14к. Вследствие выработки импульсов запрета данные сердечникипосле окончания импульса «Считывание 3 продолжают оставаться в состоянии «-ЬВ (т. е. в исходном состоянии), Так как во время подачи сигналов «Считывание 3 на вход элемента И Игпоступает нулевой сигнал с триггера 15 а то на его выходе не вырабатывается сигнал запре считывания выбранного сердечника матрицы второго разряда. Вследствие этого данный сердечник переходит из состояния «-ЬВ в состояние «-В, а возникший сигнал - с обмотки 112 на элемент И 21 г на другой вход которого продолжает поступать сигнал «Считывание 3. При наличии указанных сигналов на входе элемента И 21 2 на его выходе вырабатывается сигнал переводящий триггер 16 г в единичное состояние. Таким образом, после этапа восстановления исходного информационного слова на регистре прямого кода хранится прямой код слова «10...1, на регистре инверсного кода инверсный код информационного слова «01... ... который выдается на выход устройства путем подачи сигнала «Строб выдачи инверсного кода на элементы И 22i, 22jLt 22. Режим записи информации в запоминающее устройство обеспечивается последовательной подачей сигнала «Запись на формирователи 3 и 6 с одновременной посылкой кода записываемого слова на регистр прямого кода с дальнейшей подачей сигнала «Считывание 3. Режим записи в этом случае осуществляется аналогично изложенному. Применение предлагаемого устройства позволяет повысить информационную надежность, так как без введения дополнительной информационной избыточности можно проводить анализ состояния работоспособности запоминающего устройства по анализу информации, содержащейся на регистрах прямого и инверсного кода информационного слова.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1986 |

|

SU1316047A1 |

| УСТРОЙСТВО для ВЫБОРКИ ИНФОРМАЦИИ из постоянного ТРАНСФОРМАТОРНОГО ЗАПОМИНАЮЩЕГО | 1973 |

|

SU377868A1 |

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

| Устройство для контроля параметров ферритовых сердечников запоминающей матрицы | 1984 |

|

SU1200346A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Многоканальное оперативное запоминающее устройство | 1987 |

|

SU1432606A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

МАГНИТНОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее последовательно соединенные первый регистр адреса, первый дешифратор адреса и формирователи сигналов первой группы, последовательно соединенные второй регистр адреса, второй дешифратор адреса и формирователи сигналов второй группы, накопитель, состоящий из запоминающих матриц на ферритовых сердечниках, прошитых адресными обмотками и обмотками считывания, одни концы которых подключены к шине нулевого потенциала, другие соответственно - к выходам формирователей сигналов групп и к входам усилителей считывания, триггеры, выходы которых подключены к одним из входов элементов И, отличающееся тем, что, с целью повышения надежности устройства, в него введены дополнительные триггеры и группы элементов И, причем вход каждого триггера подключен к выходу первого элемента И одноименной группы, а выход - к первым входам второго и третьего элементов И одноименной группы, вход каждого дополнительного триггера соединен с выходами четвертого и пятого элементов И одноименной группы, а выход - с первым входом шестого элемента И одноименной С2 € группы, первые входы первого, четвертого и пятого элементов И каждой группы под(Л ключены к выходу соответствующего усилителя считывания, выход каждого второго эле мента И группы соединен с вторым входом четвертого элемента И одноименной группы, вторые входы первых, вторых, третьих, пятых и шестых элементов И групп являются соответственно управляющими входами устройства, с первого по пятый выходы треto тьего и шестого элементов И групп являют( ся информационными выходами устройства. а сд N

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство | 1976 |

|

SU631994A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Дроздов Е | |||

| А., Прохоров В | |||

| И., Пятибратов А | |||

| П | |||

| Основы вычислительной техники | |||

| М., Воениздат, 1964, с | |||

| Крутильно-намоточный аппарат | 1922 |

|

SU232A1 |

| Плуг с фрезерным барабаном для рыхления пласта | 1922 |

|

SU125A1 |

Авторы

Даты

1984-12-15—Публикация

1983-02-02—Подача